# **Hypersensitive Electrical Characterization of 2D Graphene Transistor Matrix**

**MS Thesis**

**Submitted by:** **Shah Fahad**

**Registration No:** **331-FET/MSEE/F13**

**Supervised by:** **Prof. Dr. Ahmed Shuja Syed**

**Session 2013-2016**

**Department of Electronic Engineering**

**Faculty of Engineering and Technology**

**International Islamic University Islamabad Pakistan**

TH-16096

Accession No

M. *Neil*

M.S.

621.381

SHH

بِسْمِ اللَّهِ الرَّحْمَنِ الرَّحِيمِ

كِتَابٌ مُّبِينٌ

# **Hypersensitive Electrical Characterization of 2D Graphene Transistor Matrix**

**Shah Fahad**

**331-FET/MSEE/F13**

Submitted in partial fulfillment of the requirements for the

Master of Philosophy degree in Electronics Engineering with specialization in Advance Electronics at the faculty of Engineering and Technology department of Electronic Engineering International Islamic University Islamabad

Supervisor:

Day, Month, Year

Title of Thesis: Hypersensitive Electrical Characterization of 2D Graphene Transistor Matrix

Name of Student: Shah Fahad

Registration No: 331-FET/MSEE/F13

Accepted by the Faculty/Department of Electronic Engineering International Islamic University Islamabad in partial fulfilment of the requirements for the Master of Philosophy Degree in Electronics Engineering with specialization in Advance Electronics.

**Viva Voice Committee:**

Dean

Chairman/Director/Head

External Examiner

Supervisor

Member

Dr. Ihsan ul Haq

(Day, Month, Year)

## **DEDICATION**

**This Thesis is dedicated to my**

**Beloved Parents**

**And**

**My Friends**

# Certificate

This is certifying that the work contained in this thesis entitled:

**"Hypersensitive Electrical Characterization of 2D Graphene Transistor Matrix"** been carried out by **Shah Fahad** under the registration **331-FET/MSEE/F-13** in Advanced Electronics Laboratories under my supervision. In my opinion, this is fully adequate in scope and qualifies the degree of the MS Electronic Engineering with specialization of the Advanced Electronics.

**Supervisor**

**Engr. Prof. Dr. Ahmed Shuja Syed** \_\_\_\_\_

**Advisor to Rector & President (Engineering Programs)**

**Principal Investigator IIU- Islamic Development Bank Advanced Electronic Laboratories Project**

**International Islamic University, Islamabad, Pakistan**

**Tel: +92-51-9019453**

**E-mail: ahmed.shuja@iiu.edu.pk**

# Table of contents

|          |                                       |           |

|----------|---------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                   | <b>1</b>  |

| 1.1      | Introduction                          | 1         |

| 1.2      | Thesis motivation                     | 3         |

| <b>2</b> | <b>Graphene background and theory</b> | <b>6</b>  |

| 2.1      | Graphene history                      | 6         |

| 2.2      | Graphene structure                    | 7         |

| 2.3      | Moore's law                           | 8         |

| 2.4      | Silicon vs Post-Silicon Technology    | 10        |

| 2.4.1    | Short term solution                   | 12        |

| 2.4.2    | Long term solution                    | 12        |

| 2.5      | Why graphene?                         | 12        |

| 2.6      | Graphene roadmap 2020                 | 13        |

| 2.7      | Graphene's Extraordinary Properties   | 15        |

| 2.7.1    | Electronic properties                 | 15        |

| 2.7.2    | Mechanical strength                   | 16        |

| 2.7.3    | Optical properties                    | 16        |

| 2.8      | Graphene synthesis                    | 17        |

| 2.8.1    | Chemical vapor deposition             | 18        |

| <b>3</b> | <b>Graphene Literature Review</b>     | <b>20</b> |

| 3.1      | CVD Graphene a Review                 | 20        |

| 3.2      | Graphene synthesis on Ni              | 21        |

| 3.3      | Graphene transistor matrix            | 24        |

| 3.4      | Graphene metal interface              | 26        |

| 3.5      | Metal contacts for graphene devices   | 28        |

| 3.5.1    | Carrier injection                     | 29        |

| 3.5.2    | Energy band diagram                   | 30        |

| 3.6      | Graphene field effect transistors     | 32        |

| 3.6.1    | Graphene-FETs                         | 33        |

| 3.6.2    | Field effect in graphene              | 33        |

| 3.7      | Graphene FETs structures              | 34        |

| 3.7.1    | Back-gated GFETs                      | 34        |

|          |                                                                      |           |

|----------|----------------------------------------------------------------------|-----------|

| 3.7.2    | Graphene Top-gated FETs .....                                        | 35        |

| 3.7.3    | Dual-gated GFETs .....                                               | 36        |

| <b>4</b> | <b>Characterization techniques, material and equipment's .....</b>   | <b>37</b> |

| 4.1      | Electrical characterization .....                                    | 37        |

| 4.2      | Hall Effect .....                                                    | 38        |

| 4.3      | The Van der Pauw method .....                                        | 40        |

| 4.3.1    | Methodology .....                                                    | 40        |

| 4.4      | Transfer length measurements .....                                   | 43        |

| 4.4.1    | Methodology of TLM .....                                             | 44        |

| 4.5      | Equipment's .....                                                    | 46        |

| 4.5.1    | Nano-chip reliability grade Hall Effect System .....                 | 46        |

| 4.5.2    | Application & Specification .....                                    | 47        |

| 4.5.3    | Automatic System of Material Electro-physical Characterization ..... | 48        |

| 4.5.4    | Atomistic Layer Nano-master Deposition System .....                  | 51        |

| 4.5.5    | Rapid Thermal Processing System .....                                | 52        |

| <b>5</b> | <b>Samples preparation and experiments .....</b>                     | <b>53</b> |

| 5.1      | Wafer cleaving/dicing .....                                          | 54        |

| 5.2      | Sample preparation for van der pauw .....                            | 55        |

| 5.3      | Transfer Length Model sample preparation .....                       | 56        |

| 5.4      | Experimental section .....                                           | 57        |

| 5.4.1    | Contactless measurements .....                                       | 57        |

| 5.4.2    | Contacted experiments .....                                          | 59        |

| 5.4.3    | TLM base experiment .....                                            | 61        |

| <b>6</b> | <b>Results and Discussions .....</b>                                 | <b>62</b> |

| 6.1      | Section 1 .....                                                      | 63        |

| 6.2      | Section 2(a) .....                                                   | 69        |

| 6.2.1    | Section 2(b) .....                                                   | 75        |

| 6.2.2    | Section 2(c) .....                                                   | 79        |

| <b>7</b> | <b>Summary and future work .....</b>                                 | <b>82</b> |

| 7.1      | Summary and key findings .....                                       | 82        |

| 7.2      | Future outlook .....                                                 | 84        |

| <b>8</b> | <b>References .....</b>                                              | <b>86</b> |

## List of figures

|                                                                                                                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Fig 1.1: graphene transistor matrix structure .....                                                                                                                                                   | 4  |

| Figure2.1: (a) graphene hexagonal structure (b) band gap representation of graphene .....                                                                                                             | 7  |

| Figure 2.2: Transistor gate length vs year of production by ITRS.....                                                                                                                                 | 9  |

| Fig 2.3: Intel Abandoning Silicon with 7nm and Beyond – Silicon Alternatives Coming By 2020 .....                                                                                                     | 11 |

| Fig 2.4: Europe's Graphene Flagship technology roadmap, targeting research areas designed to take graphene and related 2d composites from academic institutions into society.....                     | 14 |

| Fig 2.5: General scheme for CVD graphene growth on Ni substrate .....                                                                                                                                 | 18 |

| Fig 3.1: CVD method for Graphene growth step by step.....                                                                                                                                             | 22 |

| Fig 3.2: graphene transistor matrix specification.....                                                                                                                                                | 26 |

| Fig 3.3: energy band diagram for (a) metal/semiconductor (b) metal/metal (c) metal/graphene contacts.....                                                                                             | 30 |

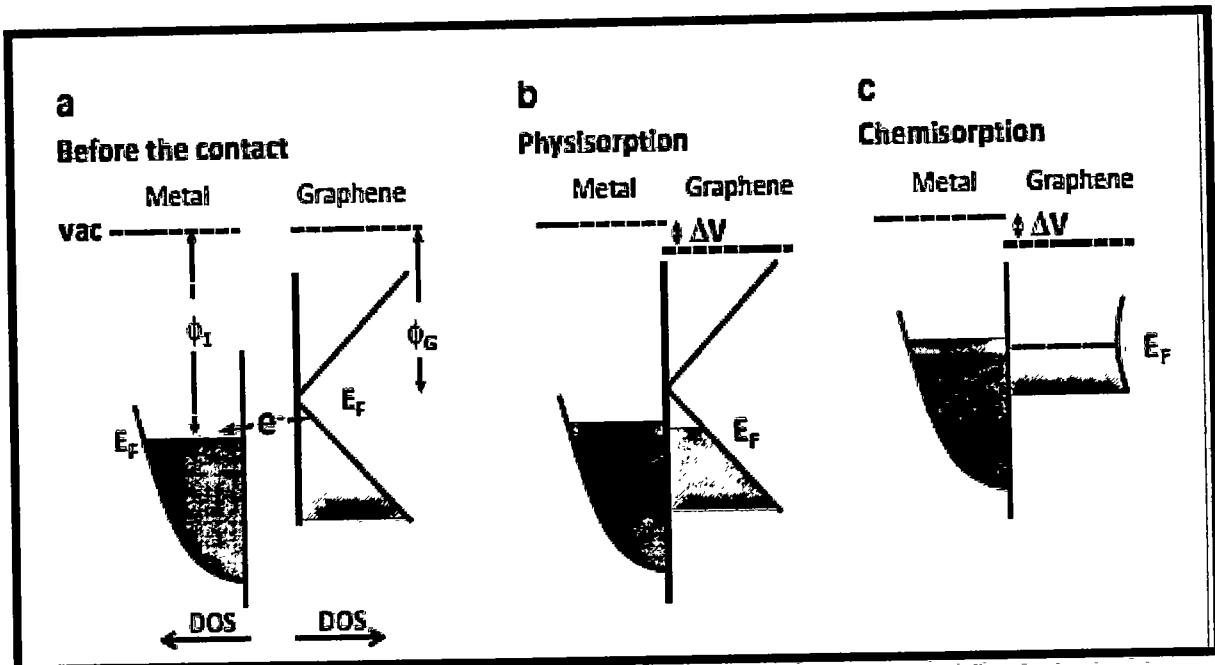

| Figure 3.4: The relation between the density of states and the energy at the metal/graphene interface (a) before and after the contact formation (b) physisorption metal (c) chemisorption metal..... | 31 |

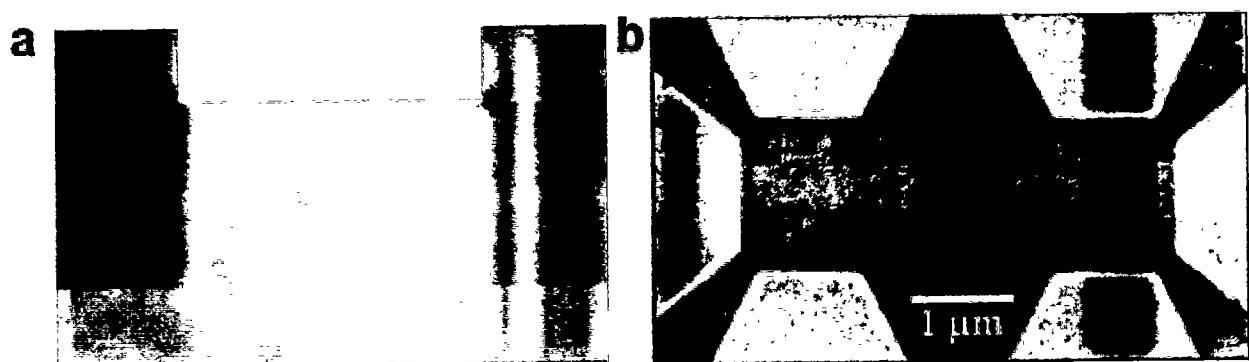

| Fig 3.5: (a) schematic diagram (b) SEM image of back-gated FET.....                                                                                                                                   | 34 |

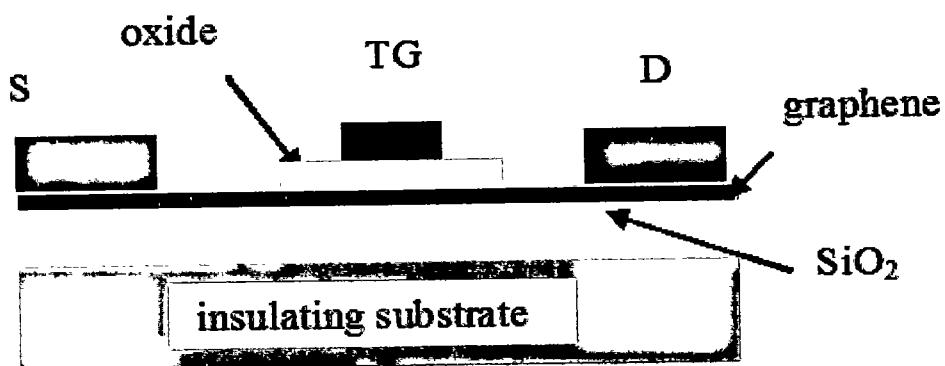

| Fig 3.6: schematic diagram of graphene top-gated FET.....                                                                                                                                             | 35 |

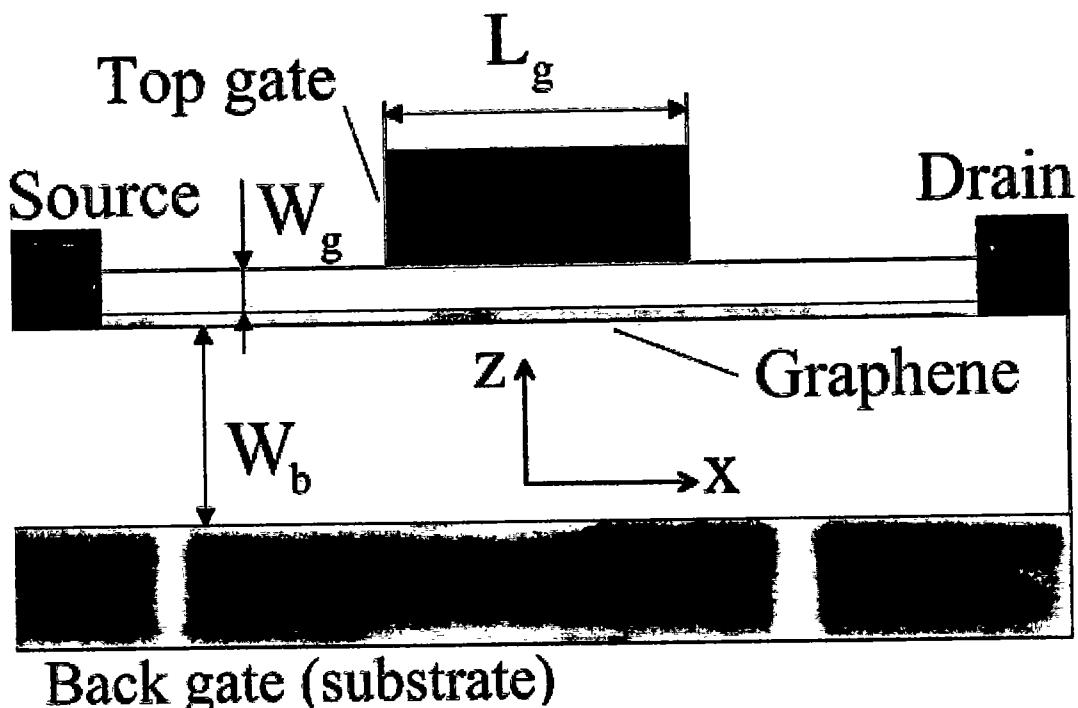

| Fig 3.7: Schematic of dual-gated graphene field effect transistor.....                                                                                                                                | 36 |

| Fig 4.1: (a) basic schematic of Hall Effect (b) Hall Effect for n-type semiconductor (special case)....                                                                                               | 38 |

| Fig 4.2: possible sample geometries for Van der pauw technique.....                                                                                                                                   | 40 |

| Fig 4.2 (b) : The Van der pauw terminal setup for finding $R_A$ and $R_B$ .....                                                                                                                       | 41 |

| Fig 4.3: schematic of Hall measurements.....                                                                                                                                                          | 42 |

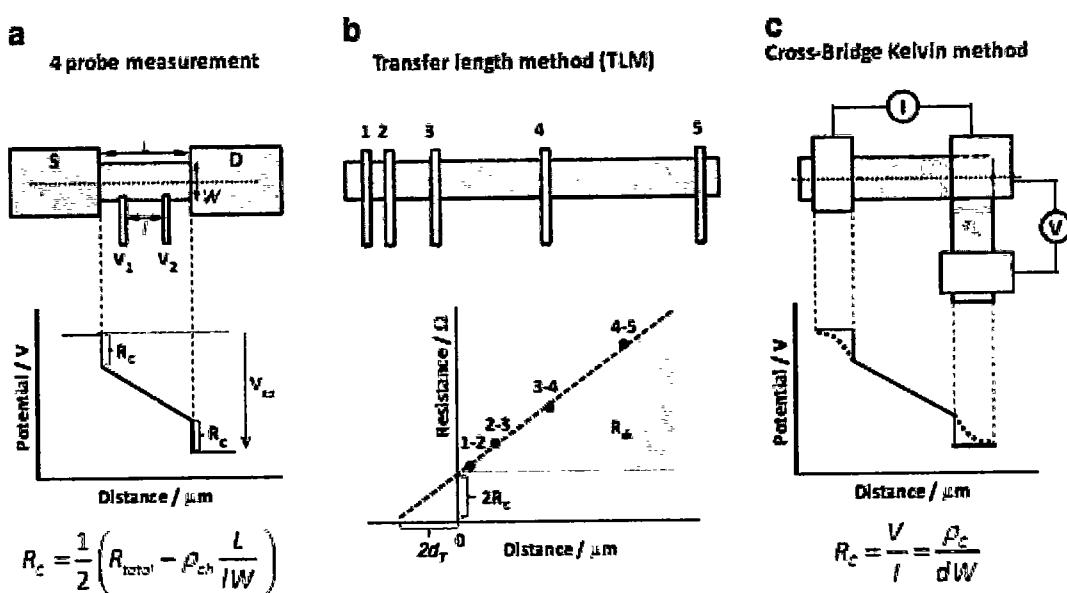

| Fig 4.4: (a) Four-probe measurement, (b) transfer length technique (c) cross-bridge Kelvin technique.....                                                                                             | 43 |

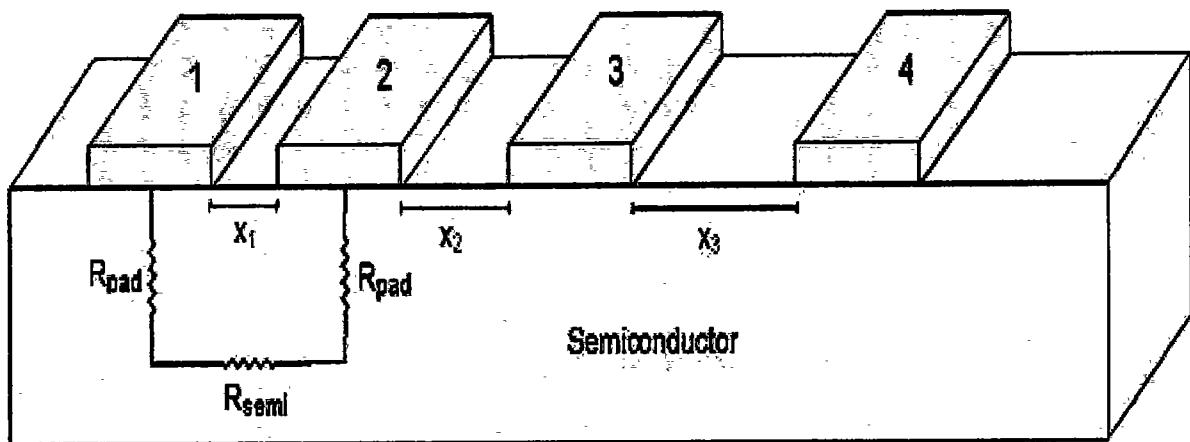

| Fig 4.5: Metal pattern for TLM separated by a varying distance.....                                                                                                                                   | 44 |

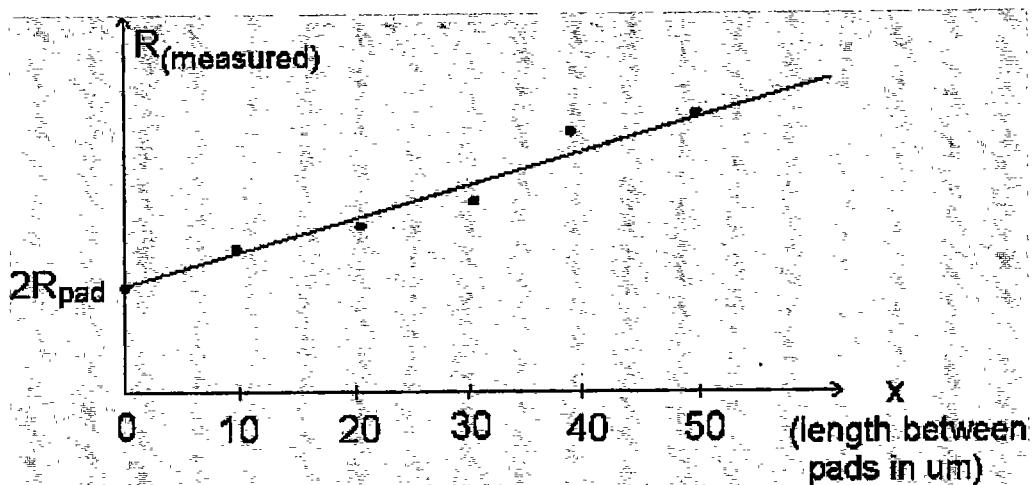

| Fig 4.6: plot b/w resistance and separation of 2 pads.....                                                                                                                                            | 45 |

| Fig 4.7: The basic units of nano chip reliability grade hall effect system. The image is taken by the authority permission of Advance Electronic Lab International Islamic University Islamabad.....  | 47 |

| Fig 4.7: (a) ASMEC parameters and Application.....                                                                                                                                                    | 49 |

| Fig 4.7: ASMEC main parts (Advance Electronic Lab) International Islamic University.....                                                                                                              | 50 |

| Fig 4.8: Atomistic Layer Nano-master Deposition System units.....                                                                                                                                     | 51 |

| Fig 4.9: Rapid thermal processing system (Advance Electronic Lab IIU Islamabad).....                                                                                                                  | 52 |

| Fig 5.1: wafer cleaving in lab.....                                                                                                                                                                   | 54 |

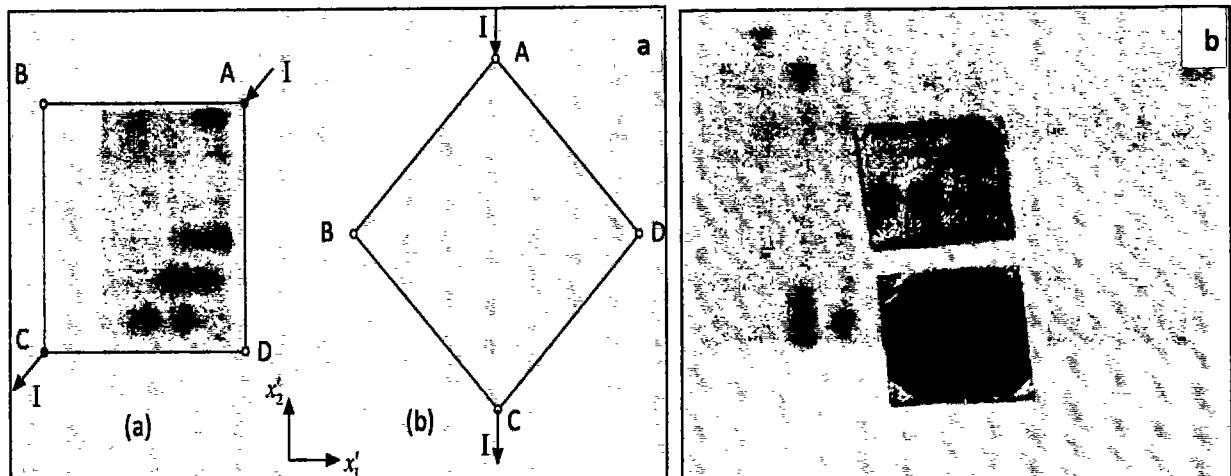

| Fig 5.2: (a) possible contact placement (theoretical) (b) sample designed in lab.....                                                                                                                 | 55 |

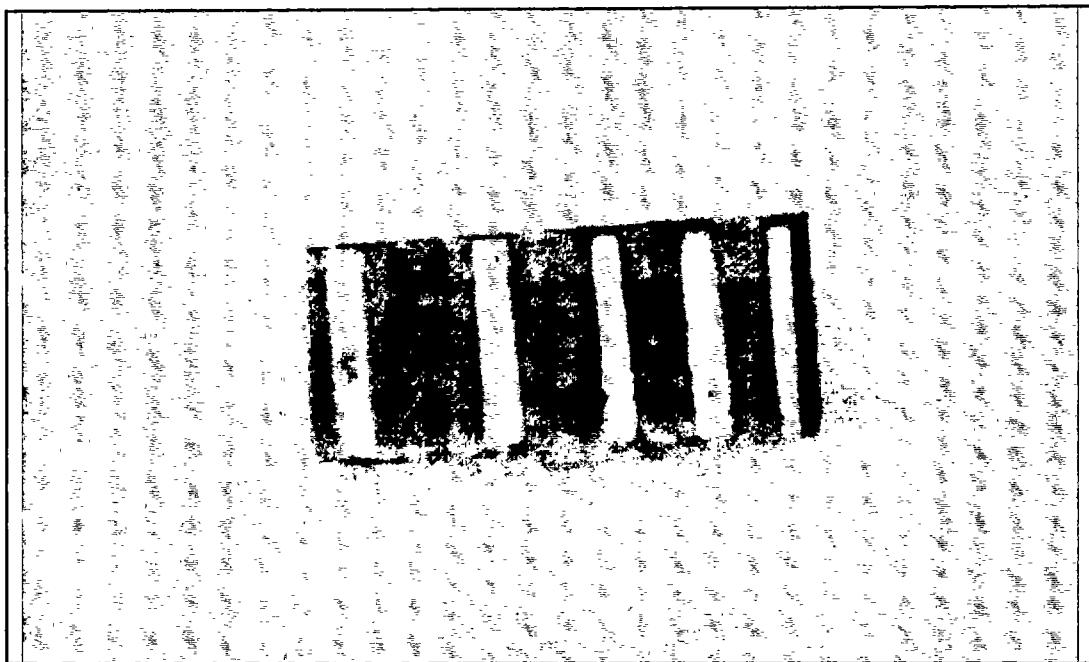

| Fig 5.3: A TLM structure designed in AEL (Advance Electronic Lab).....                                                                                                                                | 56 |

| Fig 5.4: (a) sample placement (b) connecting wires (c) permanenet magnet (d) contact check and measurements.....                                                                                      | 58 |

| Fig 5.5: basic ASMEC procedure (a) sample placements (b) readings by built in software .....                                                                                                          | 60 |

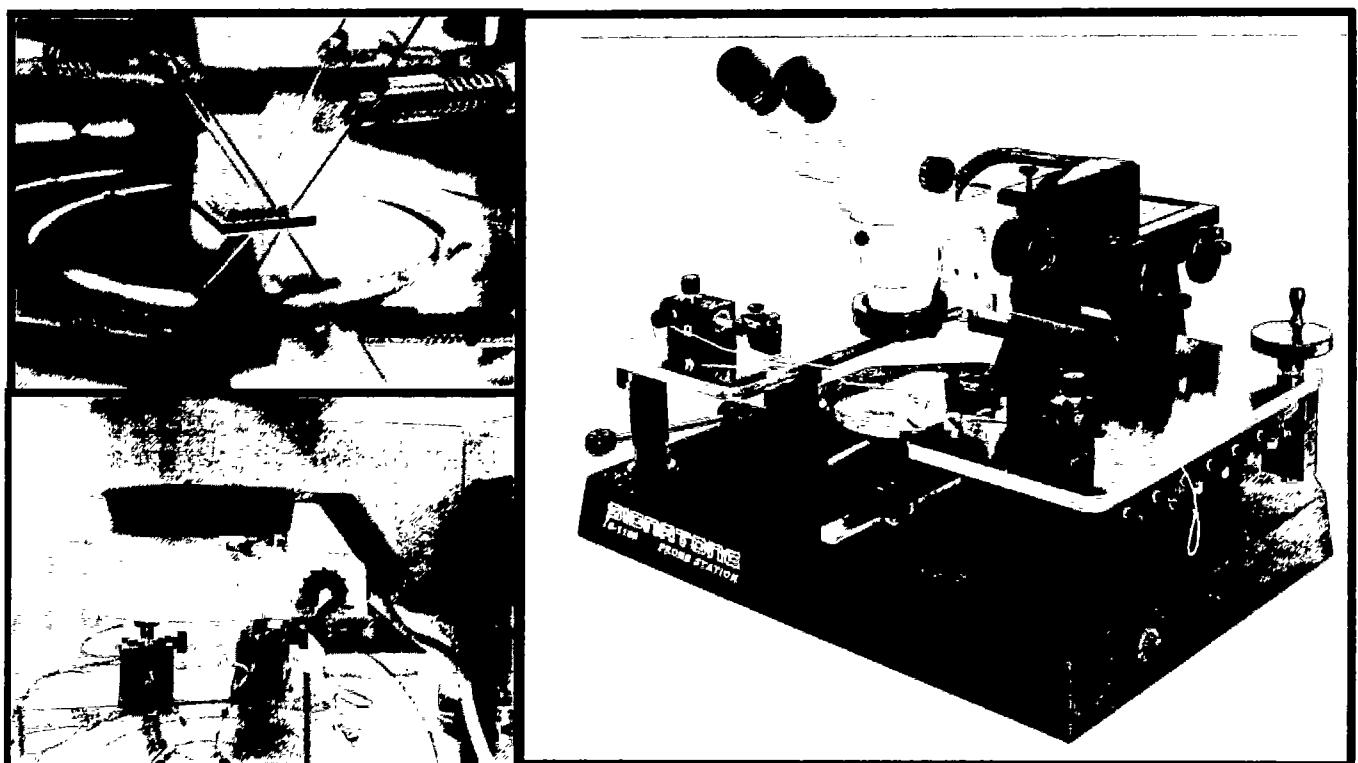

| Fig 5.6: multi head probe station schematic for TLM measurements.....                                                                                                                                 | 61 |

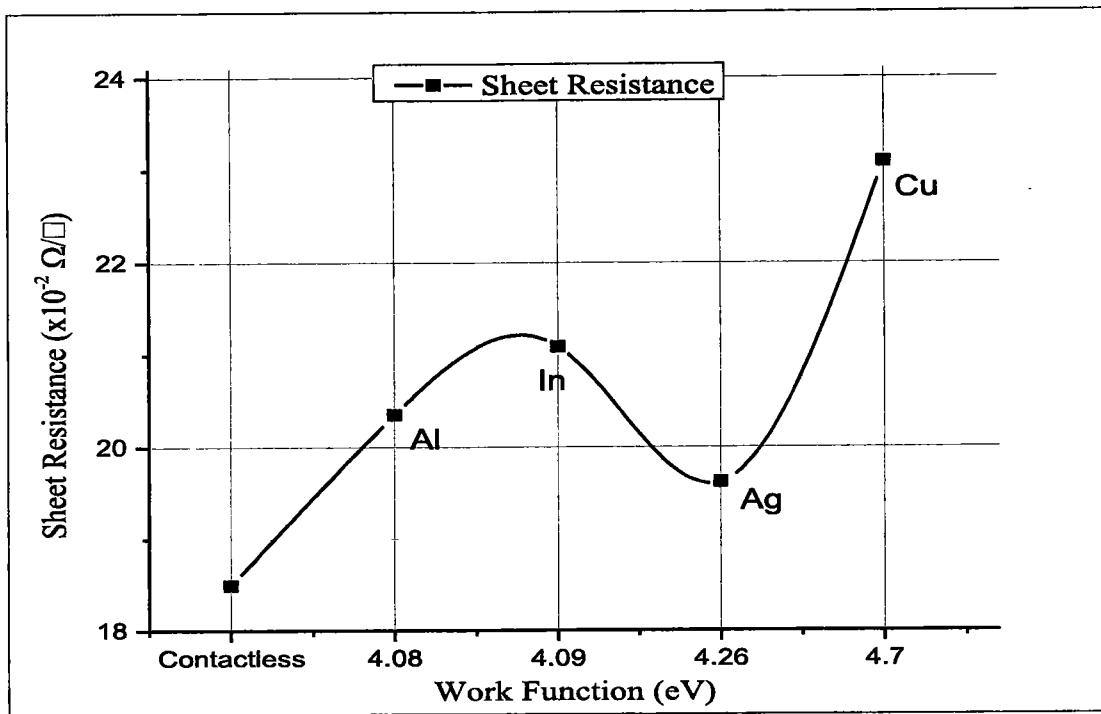

| Fig 6.1: sheet resistance of graphene transistor matrix vs metals work function.....                                                                                                                  | 65 |

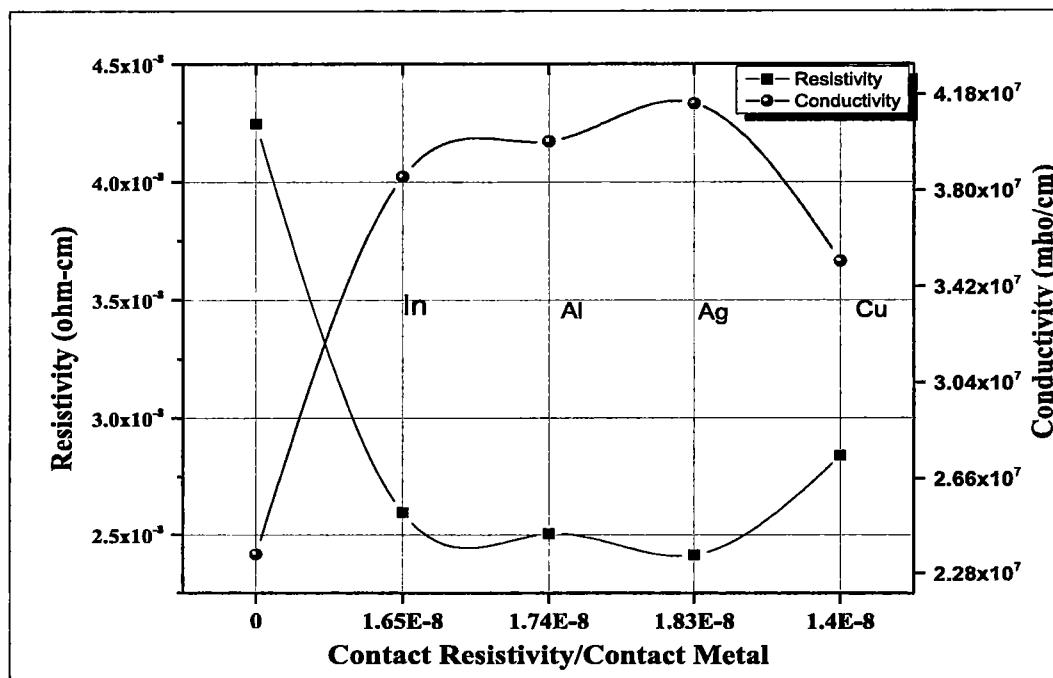

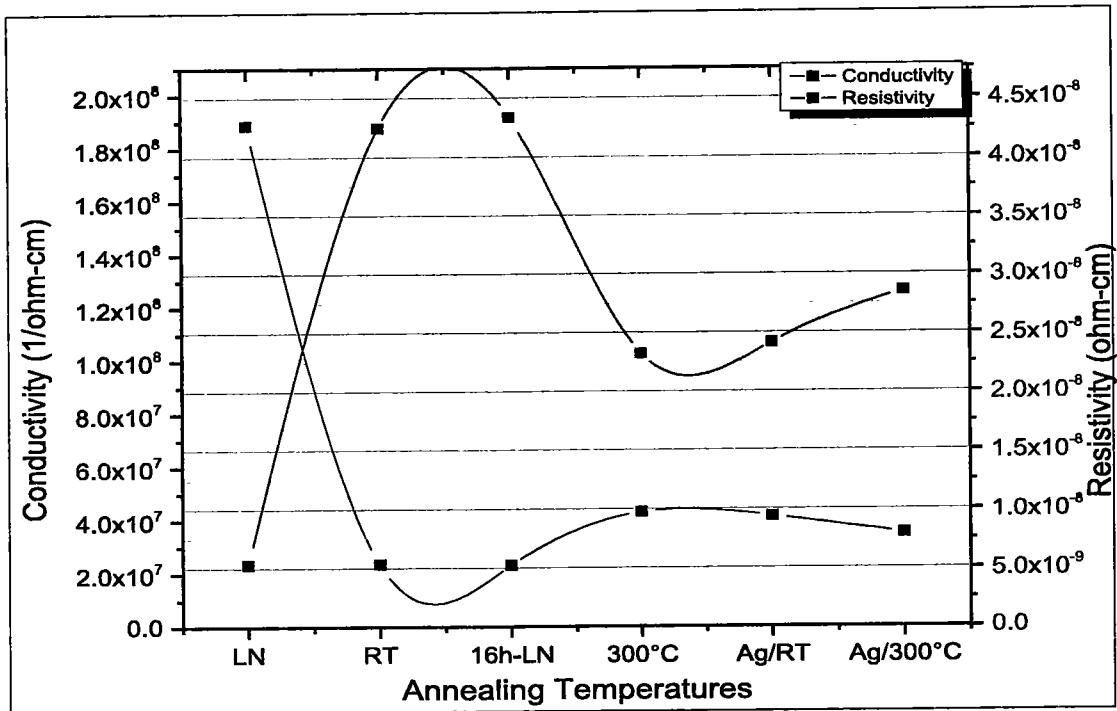

| Fig 6.2 electrical resistivity & conductivity of graphene/Ni interface without and with contacts.....                                                                                                 | 66 |

|                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

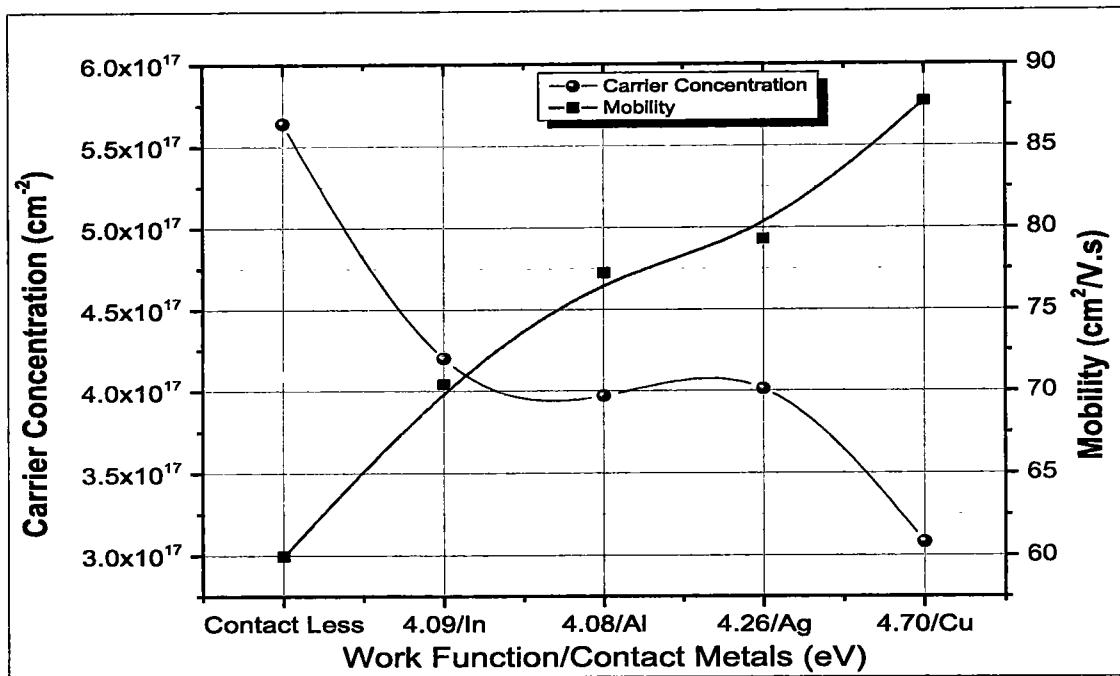

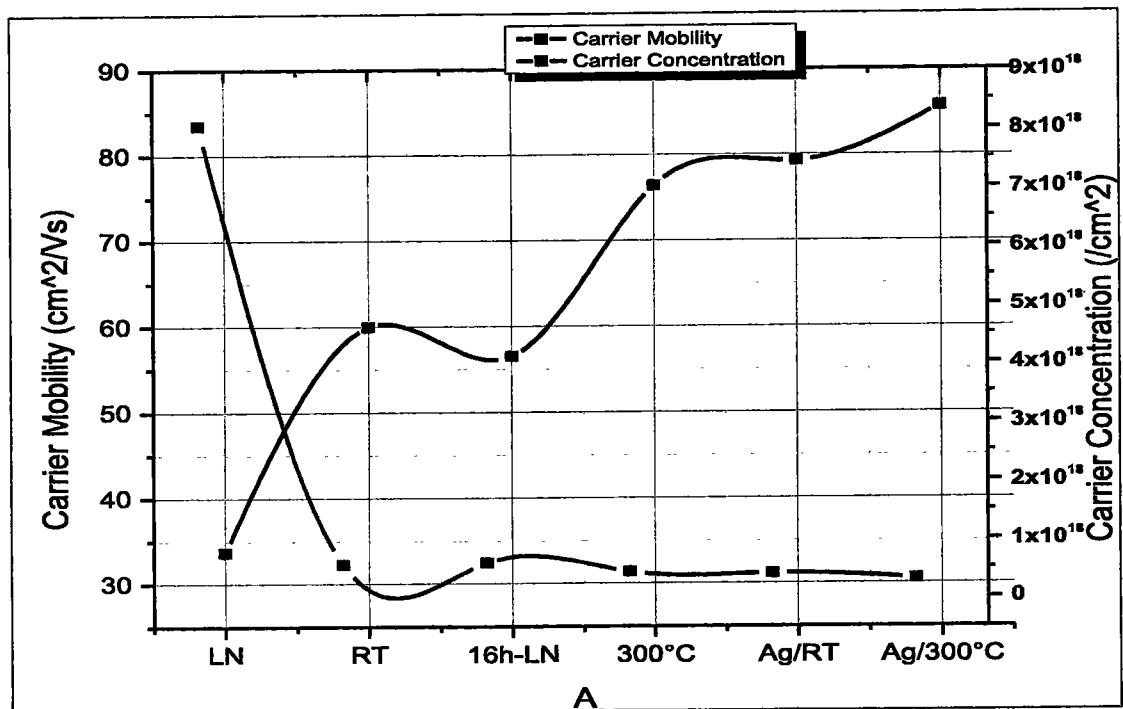

| Fig 6.3: carrier concentration and mobility of graphene transistor matrix .....                                                               | 68 |

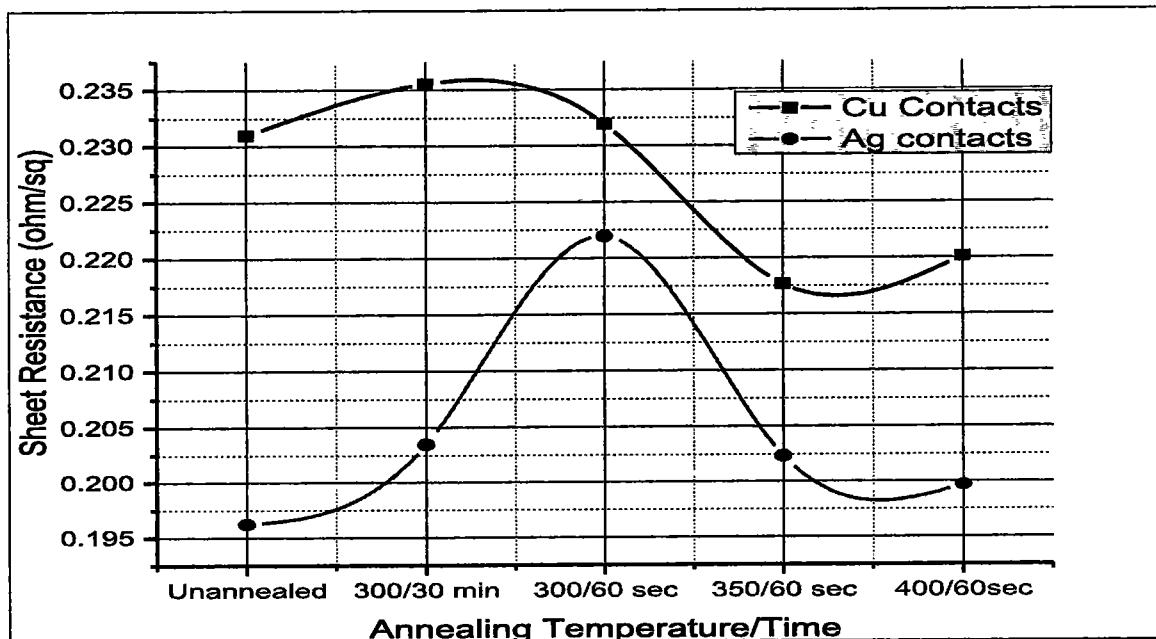

| Fig: 6.4: sheet resistance variation at different annealing temperature.....                                                                  | 70 |

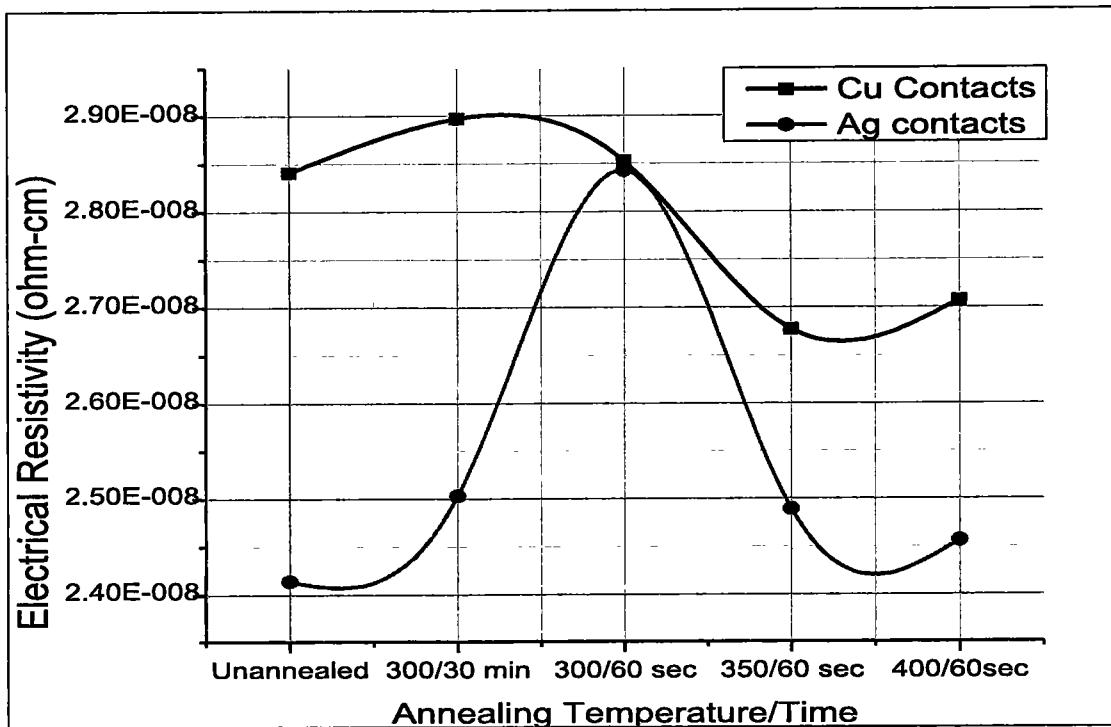

| Fig 6.5: electrical resistivity of graphene/Ni interface at different annealed temp with Ag & Cu contacts.....                                | 71 |

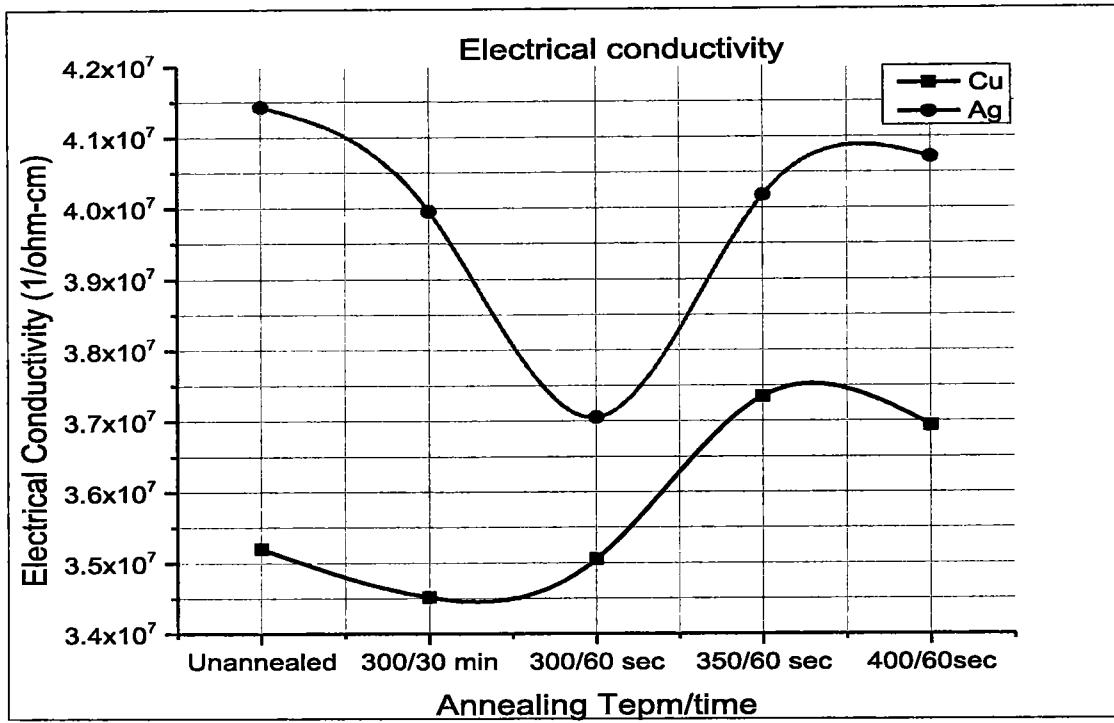

| Fig 6.6: Electrical conductivity variation with different annealing temperature.....                                                          | 72 |

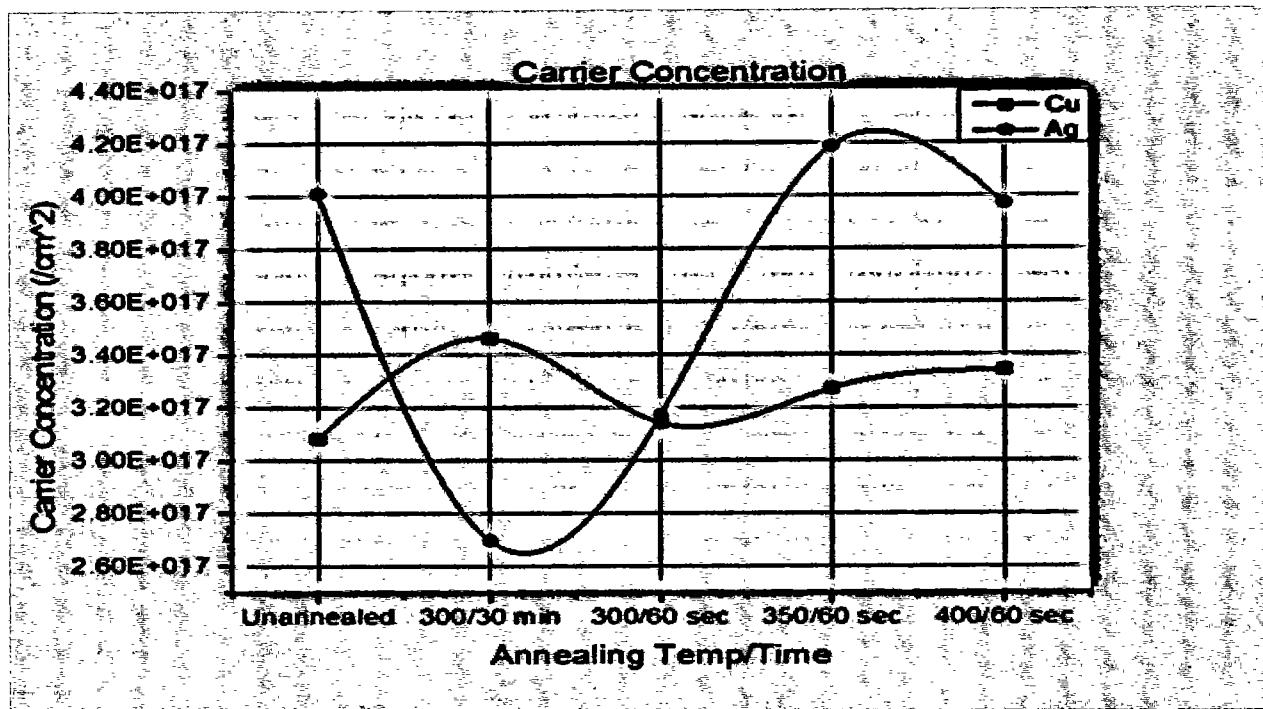

| Fig 6.7: carrier concentration in terms of different annealing temperature when we deposit Cu & Ag contacts.....                              | 73 |

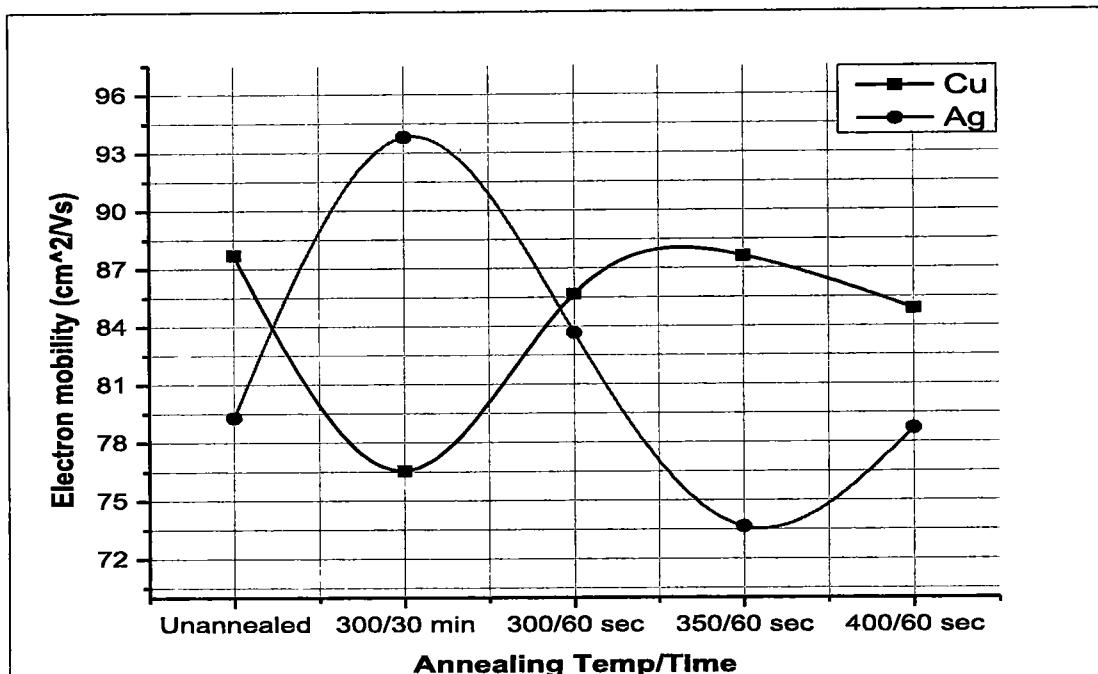

| Fig 6.8: mobility variation of graphene transistor matrix at different annealing temperature when Cu and Ag is used as contact material ..... | 74 |

| Fig 6.9: comparison report in terms of sheet resistance at various temperature conditions.....                                                | 76 |

| Figure 6.10: the electrical resistivity & conductivity at 77k vs room temperature.....                                                        | 77 |

| Fig 6.11: carrier concentration & mobility of graphene transistor matrix on different temperatures .....                                      | 78 |

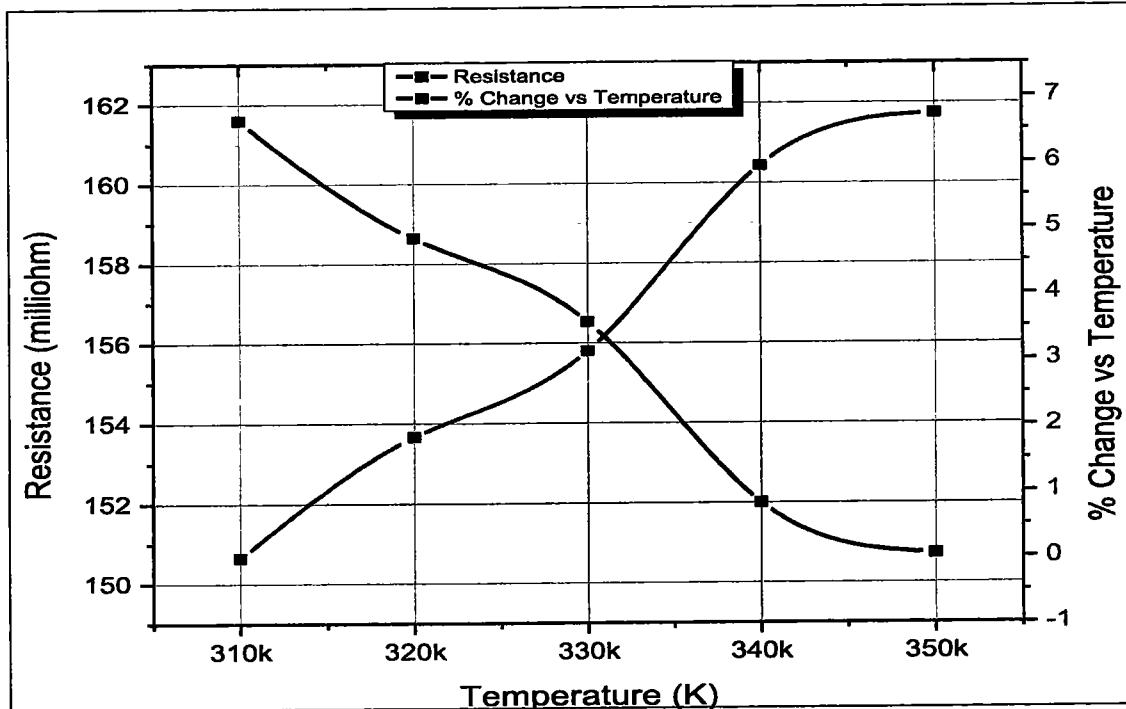

| Fig 6.12: Resistance vs temperature (black line), Temperature vs %change in Resistance (blue line).....                                       | 80 |

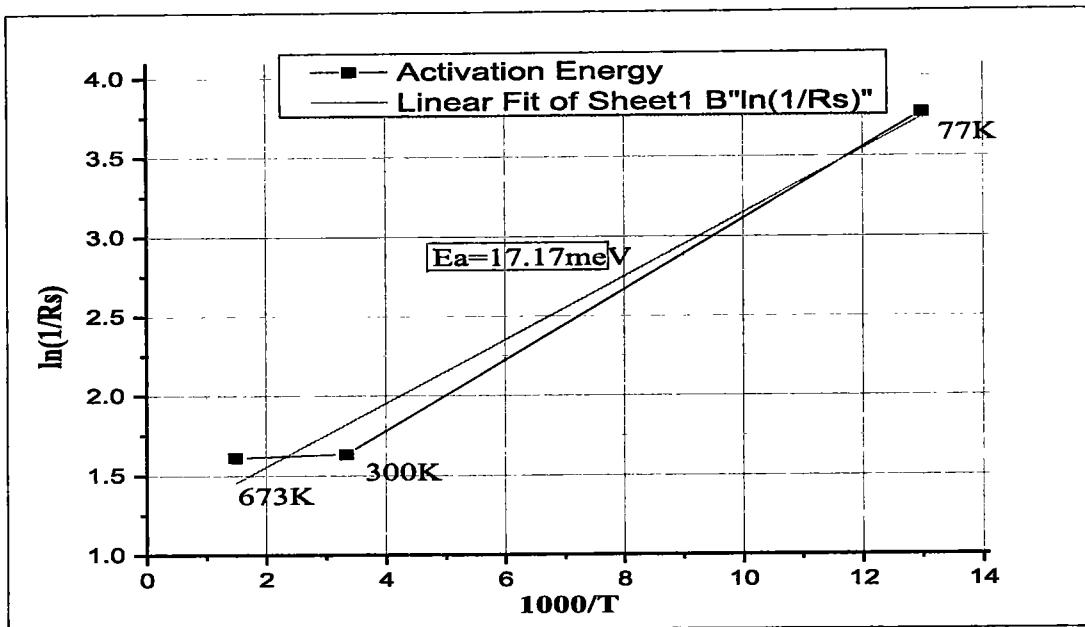

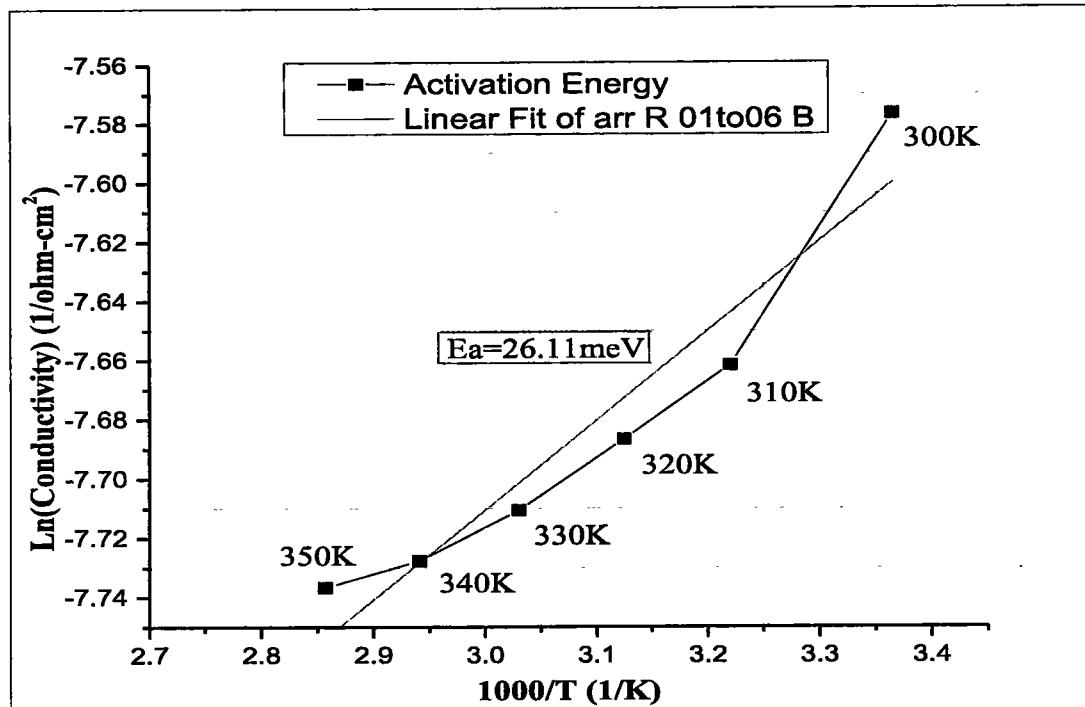

| Fig 6.13: The 1/T dependency of conductivity of graphene transistor matrix .....                                                              | 81 |

## **List of tables**

|                                                                              |    |

|------------------------------------------------------------------------------|----|

| Table 1.1: ITRS roadmap for current and future technology.....               | 1  |

| Table 2.1 synthesis techniques for graphene.....                             | 17 |

| Table 4.1: Nano chip reliability grade Hall Effect system specification..... | 48 |

| Table 4.2: ASMEC specification and operational ranges.....                   | 49 |

| Table 6.1: experimental data/parameters for contact metallization .....      | 64 |

## 1.1 Introduction:

In 1965 the co-founder of Intel Gordon E Moore published a paper around six years after the invention of first integrated circuit by Robert Noyce, by the title 'cramming more components on to integrated circuit' in which he predicted that the numbers of transistors inside a chip will become double every two years [1]. Moore's law was a guideline for semiconductor industries to achieve their future targets and long term planning. Construction of a semiconductor device needs a lot of operation like photolithography, etching, and metallization, so to perform these operation industries need the most advance and sophisticated machine made by commercial companies worldwide. Now for new advancements in these commercial designing tools, the semiconductor industry association USA, Japan, UK, South Korea and Taiwan led the foundation of International Technology Roadmap for Semiconductors (ITRS) in 1998. The last ITRS roadmap was published in 2013 in which the nodes are defines for future technology [2].

| Year | Node        | Year | Node   | Year    | Node  |

|------|-------------|------|--------|---------|-------|

| 1971 | 10 $\mu$ m  | 1995 | 350 nm | 2010    | 32 nm |

| 1974 | 6 $\mu$ m   | 1997 | 250 nm | 2012    | 22 nm |

| 1977 | 3 $\mu$ m   | 1999 | 180 nm | 2014-15 | 14 nm |

| 1982 | 1.5 $\mu$ m | 2001 | 130 nm | 2016-17 | 10 nm |

| 1985 | 1 $\mu$ m   | 2004 | 90 nm  | 2018-19 | 7 nm  |

| 1989 | 800 nm      | 2006 | 65 nm  | 2020-21 | 5 nm  |

| 1994 | 600 nm      | 2008 | 45 nm  |         |       |

Table 1.1: ITRS roadmap for current and future technology.

In table 1.1 the node means the size of transistor gate or we can say that the industry has the capability to pattern the desire length structure by photolithography. For complete details of the device shrinking Intel had presented a Tick-Tock model adopted by chip manufacturers [3]. In table 1.1 the node 10 nm is known as beyond CMOS technology and is not a silicon based technology because the physical limits of silicon prevent it further miniaturization. As a CMOS transistor function involved both holes and electrons as a charge carrier but as we know that holes mobility's are very low in silicon as compared to electron. Next is the heating issue because the performance of silicon degrades at high temperature while the alternative material like gallium nitride Silicon carbide and graphene perform well at high temperatures and does not require a heat sink. The most important issue related to silicon transistor is that upon further miniaturization the silicon dioxide loses its insulation properties.

So to keep Moore's law alive chip manufacturing industries are going to shift to the post silicon technologies but the question is which new material is the best contender to replace silicon. The ITRS have suggested two types of solutions, a short term solution and a long term solution. The short term solution is to replace silicon CMOS technology with Ge and in GaAs or All Ge CMOS technology. The long term solution is to replace silicon or the materials in the short term solution with CNT (Carbon Nano Tube), Graphene, TMDC (Transition metal dichalcogenide). In this thesis we are going to explain the long term solution because our projects are based on graphene transistor structure. Graphene is a single sheet of carbon in honeycomb lattice structure and is a good conductor of heat and electricity. The electron mobility of graphene is 100 times greater than silicon [4]. Single sheet of graphene is thermodynamically stable at room temperature while the miniaturization in silicon is the

main issue. Graphene based transistor can be used for Tera Hertz transistor application as IBM has already graphene based front end receiver which operates at 4.3 GHz. The main issue related to graphene is the compatibility with other material because graphene's too much high conductivity is difficult to handle.

## **1.2 Thesis Motivation:**

Graphene is the 2D, single atom thick sheet of hexagonally arranged carbon atoms and is the basic building block for carbon nanotube and fullerenes. Graphene was discovered by two scientists Andre Geim and Konstantin Novoselov at the University of Manchester in 2004 and get Nobel Prize in physics in 2010 [5]. Graphene is a Novel material also known as the material of the century due to its extra-ordinary and magical properties. According to Dirac equation the relativistic mass of charge carriers inside a graphene is zero and can travel with a speed nearly to the speed of light that is why these charge carriers are called the Dirac fermions. Graphene has exceptional and the most unique electrical, optical and mechanical properties. Mechanically graphene is 100 times stronger [6] than steel with breaking strength of 43- Nm and with elastic limit of 20% [7] means that it can be stretched 20% more than its original shape without any damage. The most important property of graphene is its highest electron mobility of  $200,000 \text{ cm}^2 \cdot \text{V}^{-1} \cdot \text{s}^{-1}$  [8] at room temperature 100 times greater than silicon and the carrier density of  $10^8 \text{ A/cm}$  100 times more than Cu. Graphene is optically transparent and absorb only 2.3% of light and also the lightest material by weight as only a gram of graphene can cover a whole football ground.

Now the most considerable thing is that graphene is the most sensitive material and all of these properties changes when graphene becomes in interface with other materials like

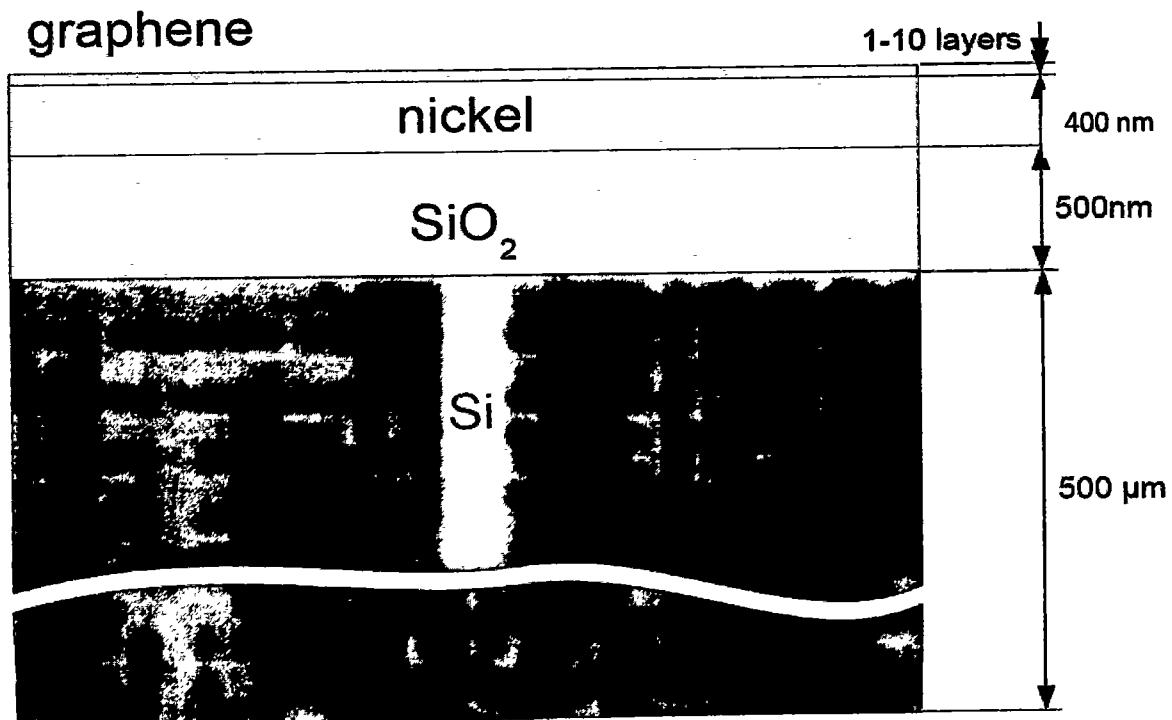

metals and dielectrics. In case of metal interface, the modification in properties of graphene occurs due to charge transfer, change in band structure and also due to re-hybridization. Also in case of Ni magnetization may produce in graphene and can create tunneling effects. The interface between metal and graphene depends upon the metal degree of interaction and its structure and the minimum inter layer distance between them after interaction. For strong bonding the inter-layer distance should be less than  $2\text{A}^\circ$  [9] as in case of Ni also for charge transfer the work function may play a key role. The most important thing is the lattice mismatch between the underlying metal and graphene. Nickel and graphene possess relatively the same lattice constant so Ni and graphene makes a hypersensitive interface. The device structure we are using in our research is grown by CVD method and have the following parameters shown in Figure 1.1:

Figure 1.1: graphene transistor matrix structure.

|                                    |                                         |

|------------------------------------|-----------------------------------------|

| Wafer size= 100 mm                 | growth method =CVD                      |

| Graphene thickness= 1 to 10 layers | wafer thickness =500 um                 |

| Wafer orientation of Si= (110)     | SiO <sub>2</sub> layer thickness=500 nm |

| Ni layer thickness= 400 nm         |                                         |

The device structure mentioned above is known as "Graphene Transistor Matrix" and can be used for variety of graphene based transistor application when fabricated on silicon substrate. The choice of graphene layer interface with nickel (400 nm) is developed in such a way to study the hypersensitive interface electrical characterization for exfoliation in making future graphene based transistor protocol. The detailed hypersensitive electrical characterization may be able to provide us an insight to this customized transistor matrix for its utilization during graphene transistor fabrication. The problem is to identify the potential of this design structure in the applicability of few layers of two-dimension graphene transistor fabrication with lesser processing and engineering steps.

## Chapter 2: Graphene Background and Theory

### 2.1 Graphene History:

Graphene known as a miracle material is the 2D allotrope of Carbon and the world's thinnest material ever known to mankind. Graphene is only one atom thick and considered to be the strongest material ever imagined. Its 2D nature can also be proved mathematically and when it is stretched it looks like a chicken wire.

Graphene is impermeable means that upon warming its shrinks and expands when cold, made from the ordinary Graphite as the led used in our pencils. The word graphene is nomenclature as Graphite and -ene [10] as a suffix named by the German Chemist H.P Boehm in 1962. P.R Wallace in 1947 was the first who explored the mystery of this wonder material theoretically by understanding the 3D Graphite electronic properties through the massless fermi Dirac equation.

In 1948 [11] the first ever TEM image of few layers of Graphite were published by G. Ruess. A few years later the single layer Graphene was directly observed by Electron Microscopy. In 1990 the researchers start to mechanically exfoliate the graphite thin films flakes and up to 2004[12] they were close to have 50 to 70 layers thick Graphite flakes. In 2004 two scientists at the university of Manchester Andre Geim and Kostya Novoselov [13] used bulk Graphite to extract monoatomic layers of graphene and transferred them onto  $\text{SiO}_2$  /Si substrate using the micromechanical cleavage also known as the scotch tape method. Graphene synthesized by the cleavage technique led the foundation to the direct observation of quantum Hall effect in Graphene, which provides the evidence of massless Dirac fermions theoretically predicted.

Adre Geim and Kostya Novoselov received the Nobel Prize in Physics in 2010 for their groundbreaking experiments and pioneer research in 2D materials [14]. It is so hard to produce Graphene large sheets but now a days many new emerging production techniques has been developed such as CVD (chemical vapor deposition), roll to roll method, nanotube slicing and production through electrochemical method. Since 2004 after the extraction of Graphene from the bulk Graphite there is an explosion in terms of Graphene production methodology, characterization, extraordinary properties as well as potential industrial application.

## 2.2 Graphene structure:

Graphene is two-dimension crystalline form of carbon. In the hexagonal pattern the carbon atoms are densely packed with separation of  $1.42 \text{ \AA}$  [15]. Each carbon atom with four electron forms 3 sigma bonds with its neighbors and the remaining one electron makes Pi bond which is out of plane and makes Electron Sea.

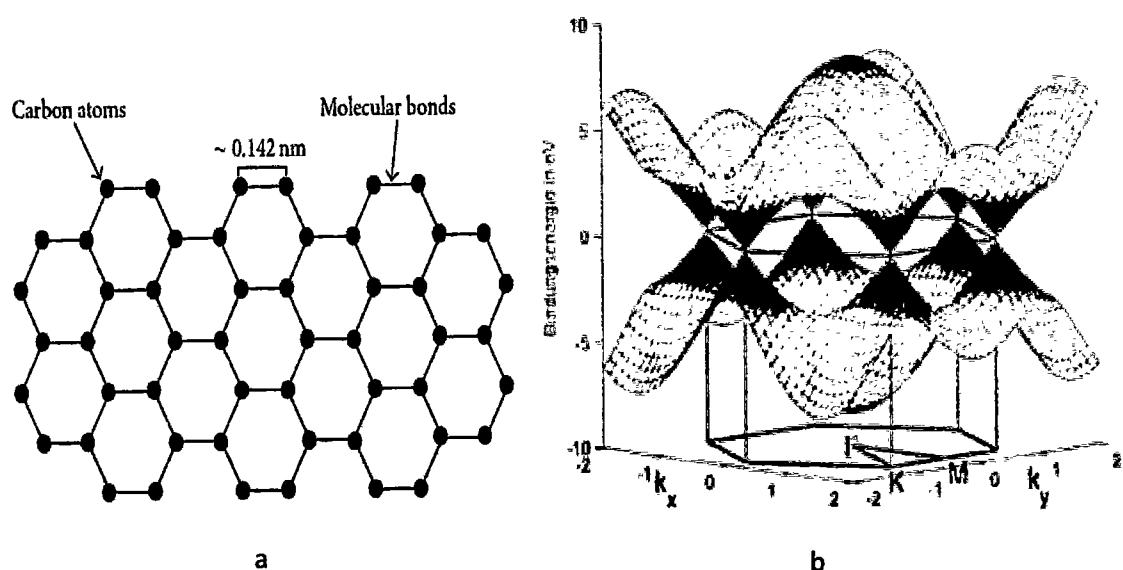

Figure 2.1: (a) graphene hexagonal structure (b) band gap representation of graphene

Graphene is stable in 2D form due to the  $sp^2$  hybridization in which 2 electrons in the carbon atom occupy the 1S spherical shell while the remaining 4 electrons are accommodated in the 2S and 2P shells.  $sp^2$  hybridization is obtained by the hypothetical mixing of 2S and 2P orbitals. The 4<sup>th</sup> electron has occupied a P orbital perpendicular the plane which makes an electron cloud that is why graphene have the ballistic charge transportation property. In graphene due to its 2D nature every carbon is available to contribute in chemical reaction and also in all allotrope of carbon graphene has the maximum ratio of edge atoms. Scientists reported that as compared to multi-layer graphene the single layer of graphene is 100 times more reactive [16].

Graphene is semi metal with zero band gap and its valance and conduction band overlaps at Dirac points at the edge of Brillouin-zone as shown in Figure 2.1. Graphene sheet is a 2-dimension membrane in a 3-dimension space so there is more configuration like, by stacking many sheets on top of each other forms graphite which is a 3D form of carbon allotrope. These layers are stacked together by a force called the Van der Waals which interacts weakly. Similarly, by rolling the graphene sheets in to the cylindrical form we can get a carbon nanotube, the 1D cousin of graphene and they both shares some of the most extra-ordinary properties of graphene. There are many more like rolling the graphene sheets into a spherical shape called Buckminsterfullerene and the Fullerenes the 0D cousin of this wonder material graphene.

### **2.3 Moore's law:**

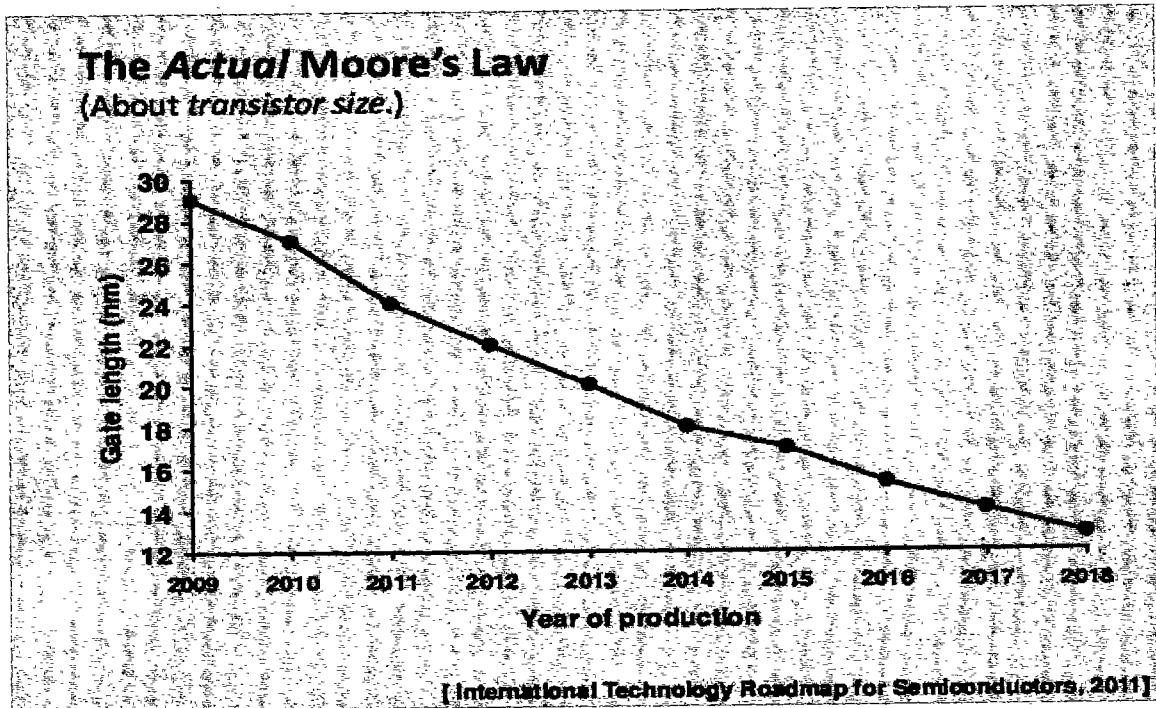

In 1965 the co-founder of Intel Corporation Gordon E. Moore stated a very famous law known as Moore's law which states that the total number of transistors or electronic

components in a dense Integrated circuit doubles every 2 years and the rate will be continuing for at least a decade [17]. These predictions were described in his paper "Cramming more components onto integrated circuits" published on 19 April 1965[18]. Moore's prediction proved accurate for many decades and also used for future planning to set targets for advancements in semiconductor industry developments and research. Moore's law is some kind not a physical law because the growth rate predicted by Moore held steady from 1975 up to 2012 and was faster at the first decade 1965 to the end of 1975. There is also a modified version in which instead of two years the performance of integrated circuits would double every 18 months. This modified version of Moore's law was presented by the Intel executive David House in 1975[19]. The ITRS (International Technology Roadmap for Semiconductor) investigated in 2010 that the rate would be too slow at 2013 and onward and probably 2015 will be the year of saturation of Moore's law.

Figure 2.2: Transistor gate length vs year of production by ITRS

In 2012 and onward we have a 22nm architecture but Intel announced that at the end of 2016 they will have a 14 nm processing architecture in the market and at the mid 2017 the will be able to release a 10 nm processing chips based technology. IBM also claimed that they had created a 7nm transistor based chips and will soon be in market for competition. But the most important thing is what will be beyond 7nm and what will be the future of the Moore's law [18-19]. There are many aspects but in these thesis only the topic related problem and solution will be under consideration and will be briefly discussed in the next topic silicon vs post silicon technology.

## **2.4 Silicon vs Post-Silicon Technology:**

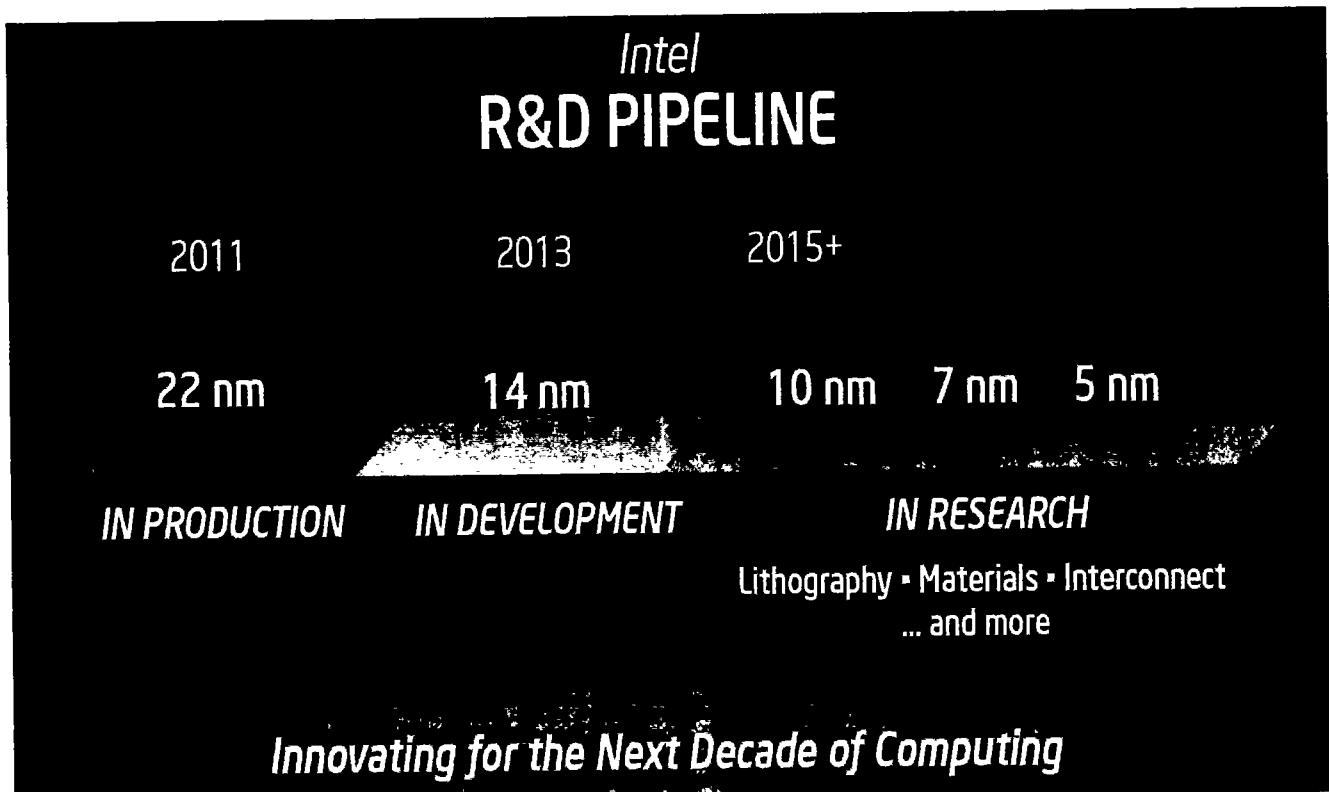

After the magical prediction of Moor's law, the competition to miniaturize the device size raises new and some serious challenges for semiconductor industries. Silicon based MOS transistors ruled the semiconductor industry up to past 50 years, but the Moore's law also stated that one day we will reach the limits of transistor to function as a transistor because the physical dimensions of silicon based transistor makes it impossible to optimize its behavior and we have to attain an optimum between gate leakage current and device performance. Scaling down of silicon based transistors around 7 nm are more difficult and need to be so expensive technology to fabricate at the industry level as shown in Figure 2.3 which shows the future of current trends in developments of Intel processing node technology [20].

Digital computing is totally based on the ON and OFF concept called the binary representation and these states are the main theory behind the transistor to function like a switch. The basic issue with the silicon based transistors is that upon scaling down to 7 nm

the transistor is set to be so close to each other's so they may be effect each other's functionality due to the Quantum Tunneling effect which means that this interference will make the transistor's to stay always in the ON state, so the processing will be against the fundamental concept of digital computing.

Figure 2.3: Intel Abandoning Silicon with 7nm and Beyond – Silicon Alternatives Coming by 2020

So 1<sup>st</sup> solution is to find an alternative material which could be scaled down and also have the fastest switching speed. The 2<sup>nd</sup> solution is the optical regime. The choice of alternative material is straight forward mean to find a new material which could be scaled down but also be fabricated using the standard silicon manufacturing technology. The solution to alternative material are composed of two types.

#### **2.4.1 Short term solution:**

The basic idea behind the short term solution is to find a new material having some identical properties like silicon and can be fabricated using the current technology. The most promising material to supersede silicon for next few years is group III-V semiconductor. These are four elements in the form of compounds in which one is (In GaAs) indium gallium Arsenide the other one is (InP) indium phosphide.

IMEC (International Medical Equipment's Collaborative) are given a task by leading semiconductor manufacturing companies like Intel, TSMC, IBM and Samsung to find the next thing after silicon, and they had already fabricated a Fin FET by using In GaAs and InP.

#### **2.4.2 Long term solution:**

The long term solution is to find a new material as well as a new emerging fabricating technology. Now a day's many researches are working on the two-dimension material after the invention of Graphene in 2004 which is the 2D allotrope of carbon. Graphene is more stable and the strongest material on the face of earth which the reason that the semiconductor industry is so interested in it. This is due to some extra-ordinary properties of graphene which will be discussed in the next topic "Why Graphene".

### **2.5 Why Graphene?**

Graphene called the substance of 20<sup>th</sup> century also known as the new silicon. The question arise here why graphene is important; the answer is graphene possess some extra-ordinary properties which makes graphene so important to replace the current semiconductor

material like silicon because it is far better than silicon. Here we discuss some magical properties of graphene and compare it with silicon.

- Graphene is 2D while silicon cannot be sliced to 2D form because it becomes unstable while graphene is stable in 2D form

- Graphene is good conductor of heat as well as the electric charges while the silicon is not the good one compare to graphene

- Graphene is 97% transparent while the silicon is not

- Graphene is flexible and can be rolled while silicon is fragile

- Electron mobility of graphene is 200 times greater than silicon

- And the most important is that graphene is not limited to only semiconductor industry graphene has a variety of application almost in every field of modern technology present.

The above listed properties and there are many more makes graphene so important that one-day graphene will replace silicon and will make the chances for the survival of Moore's law.

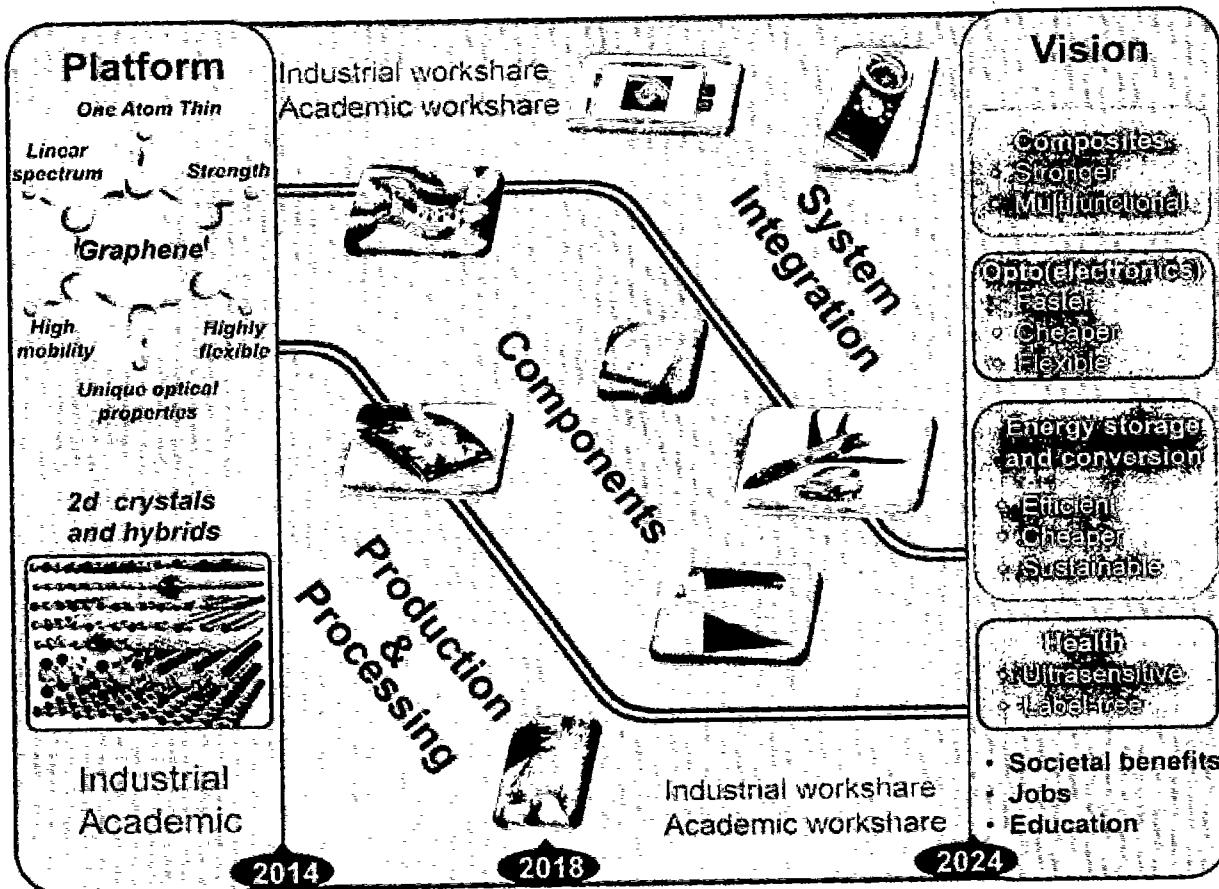

## **2.6 Graphene roadmap 2020:**

In October 2013 142 partners from 23 countries across the world sit together to form Graphene Flagship. Graphene Flagship was established by the European commission to find long terms solution to current challenges like big data systems. The findings are published in the research journal *Nanoscale* and have given open access to it [21]. This paper is the contribution of more than 60 academics and industry to find science and technology roadmap for graphene as well as other related 2D materials and also graphene based 2D

materials composites. The graphene roadmap covers the next decade and beyond as shown in Figure 2.4.

Figure 2.4: Europe's Graphene Flagship technology roadmap, targeting research areas designed to take graphene and related 2d composites from academic institutions into society

The main goal of graphene flagship is to provide guidance to industrial and community research to develop graphene and related 2D materials based products. The graphene roadmap is divided into three broad areas.

- (1) The 1<sup>st</sup> task is to find new 2D material, study there potential in developing new technology and the production of these material at industrial level.

(2) The 2<sup>nd</sup> task is to identify the concept of new devices and the components which will be utilized GRM's like graphene based high frequency electronic transistors for RF application, graphene spintronic and optoelectronics.

(3) The 3<sup>rd</sup> task is system integration means to bring GRM's based new components and structure them to form a system which would have the capability to provide new application areas such as energy application and flexible electronics.

## **2.7 Graphene Extraordinary Properties:**

Before the isolation of graphene in 2004, on the basis of theoretical formulation it was believed that due to thermal instability it is impossible for two dimension compounds to remain stable at room temperature. But from the isolation of single layer of graphene from bulk graphite is possible because graphene is single sheet of carbon and it is stable at room temperature in its 2D form. Research suggests that the reason behind graphene stability is the smallest and the strongest bonding between carbon atoms which prevents it from destabilization. Here we are discussing some extra-ordinary properties of graphene related to our research scope.

### **2.7.1 Electronic Properties:**

Graphene is zero overlapped band gap semi metal in which both the electrons and holes are charge carriers. Every carbon atom in graphene hexagonal structure have a free electron available for charge transportation and also the effective masses of both the charge carriers are zero called the Grapinos or Dirac fermions.

Experiments show that the electron mobility of suspended graphene is  $15,000 \text{ cm}^2/\text{V.S}$  and remain the same with span in temperature form 10K to 100K. Theoretically predicted

electron mobility of graphene is  $200,000 \text{ cm}^2 /V \cdot \text{S}$  at room temperature which is  $10 \times 10^6$  times higher than copper. Sheet resistance of graphene is in the order of  $10^{-6} \Omega \text{cm}$  less than silver [22]. The most important electrical property of graphene is that at room temperature the electron in graphene 2D structure can covers a micrometer distance without any collision, this phenomenon is called the ballistic transport of charge carriers. Graphene can also be doped to engineer the bandgap for some desired application.

### **2.7.2 Mechanical Strength:**

Graphene is the strongest material ever known to mankind, this is due to the strongest C-C bond with a very small separation of 0.142 nm. The tensile strength of graphene is 130 GPa as compared to structure steel having 400 MP [23]. Not only graphene is the strongest material but it is the lightest material also as  $0.77 \text{ mg/cm}^2$  which means that graphene is 1000 times lighter than paper sheet, and the most dramatic thing is that a single gram of graphene by size can cover a whole football ground. Graphene is flexible too having the Young modulus of 0.5 Tpa and the spring constant of 1-5 N/m.

### **2.7.3 Optical properties:**

Graphene is 97% transparent material and absorb only 2.3% of white light if it is only the single sheet. Graphene due to its fine structure if we add another layer its optical properties remain the same. The opacity of graphene  $\pi\alpha=2.3\%$  and in the visible frequency range its optical conductivity  $G = G = e^2/4\hbar$  ( $\pm 2-3\%$ ).

Upon laser illumination intensively Kerr effect happen in graphene with a nonlinear phase shift and the Kerr coefficient of  $10^{-7} \text{ cm}^2 \cdot \text{W}^{-1}$ . Kerr effect in graphene determines the nonlinear effects as a medium in which the most important is Soliton [24].

## 2.8 Graphene synthesis

There are many well-known techniques by which we can create graphene single layer or mono layer graphene, only names of these techniques will be discussed here because in our research the graphene we are using is grown by chemical vapor deposition method so the main focus will be one CVD method for graphene synthesis.

Before going to brief details of CVD method here we have listed some other techniques through which we can create graphene.

|                                       |                                     |

|---------------------------------------|-------------------------------------|

| <b>Mechanical exfoliation</b>         | <b>Molten salts</b>                 |

| <b>Sodium ethanol oxide pyrolysis</b> | <b>Hydrothermal self-assembly</b>   |

| <b>Electrochemical synthesis</b>      | <b>Nanotube slicing</b>             |

| <b>Roll-to-roll</b>                   | <b>Carbon dioxide reduction</b>     |

| <b>Spin coating</b>                   | <b>Supersonic spray</b>             |

| <b>Graphene synthesis by laser</b>    | <b>Microwave-assisted oxidation</b> |

Table 2.1: synthesis techniques for graphene.

### 2.8.1 Chemical vapor deposition:

Chemical vapor deposition is mostly used for growing graphene using transition metal substrates like Ni, Cu, Pd, Ru because it is the most inexpensive and the most promising approach w.r.t to cost and quality of graphene. Figure 2.5 shows the steps involves in production of graphene using the CVD method

Figure 2.5: General scheme for CVD graphene growth on Ni substrate

First of all, a metal substrate for example Ni is heated either by a furnace or some other constant heating source up to 1000 °C under lowest vacuum pressure [25]. Methane and hydrogen gases are passes through the chamber in which the plasma state is already crated. The hydrogen acts as a catalyst to crack the methane bonds and after cracking when it hits the heated metal substrate its starts diffusing. After sometimes finally the supersaturation in

which the corban atoms segregated on the surface of Ni to form graphene layers. Here the main factors which mostly effect the CVD processes for graphene production is the numbers of graphene layers which you want to grow, temperature of the target substrate, cooling rate, type of the target metal substrate, thickness of the substrate and the solubility of carbon atoms into the target substrate. For example, for single layer of graphene one will prefer Cu as substrate because the solubility of Corban in Cu is less than Ni which will be used to grow multi layers of graphene.

## Chapter 3: Graphene Literature Review

In this chapter we are presenting a review on some important topics related to our research like the CVD process for graphene growth on transition metals and specially on Ni substrate, next we will discuss that why we are using some specific dimensions of structure, graphene and metal interface, contact materials and graphene transistor modeling. Graphene is very sensitive material and all the properties of graphene totally depend upon how we are going to deal with it. In dealing with graphene the first step is by what method the graphene is synthesized because the quality of graphene should be high and there should be no contamination because any contamination even though only single atom of other material may affect the properties of graphene so all the requirements for synthesis of graphene should be fulfilled. Next as we discussed earlier that graphene is very sensitive material because all the properties of graphene changes when it becomes in interface with other material so it's very difficult to tackle because the graphene thickness is in nanometers so in this chapter we also discussing some work done with graphene metal interface and all its effect on the graphene properties and the combine properties of interfaced structures.

### 3.1 CVD Graphene a Review:

Graphene a 2D form of carbon having a honeycomb structure drawn attention of many scientists due to its unique electrical, mechanical and optical properties. Due to the

importance of this wonder material many research and review papers has been published.

These papers present the general perspective of graphene research like graphene electronic properties, graphene based photonics and optoelectronics, graphene synthesis, graphene transistors and graphene application in energy storage as well as bio sensing application.

Many journal has been reported on the chemical vapor deposition growth of graphene on metal surface. CVD method for graphene was first time reported in 2008 and with time to time it has been modified due to some important factors like cost, graphene quality and throughput of the system.

The basics of general CVD methods are discussed in chapter no 2. Here we will discuss application specific CVD in which the target metal substrate will be Ni.

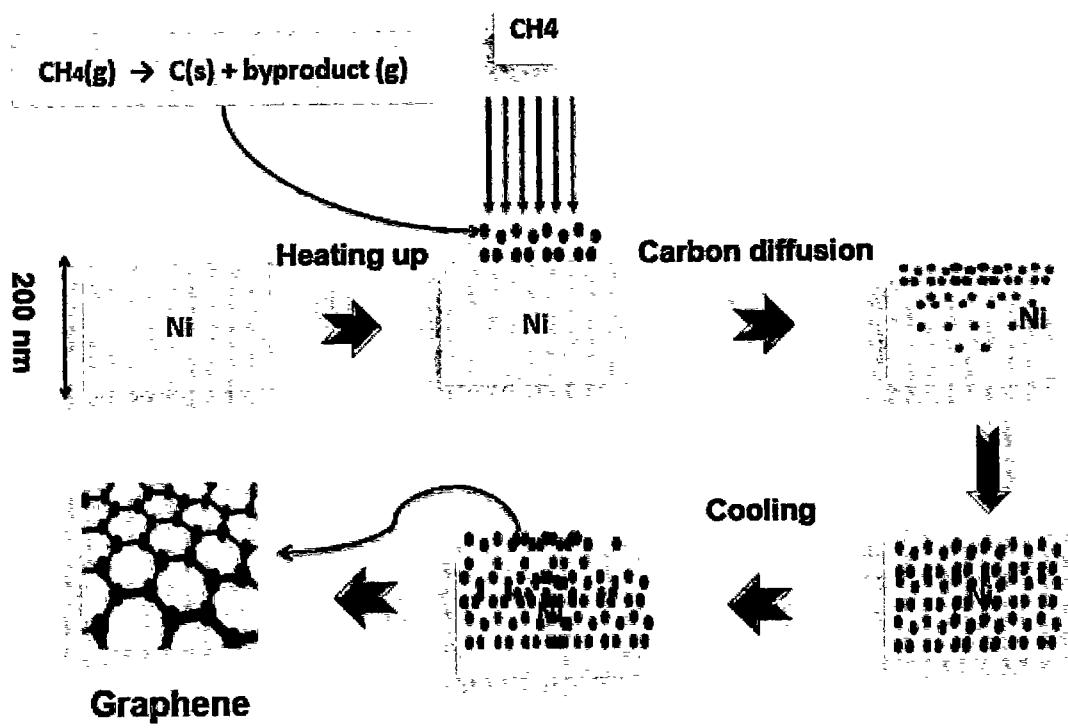

### **3.2 Graphene synthesis on Ni:**

Y. Zhang et al, explains in their review journal the most promising and widely used CVD method for graphene growth on Ni substrate [26]. We are explaining this method in very detail as the matrix we are using in our research is grown on such technique.

Generally, at the starting point the polycrystalline Ni is annealed in the presence of Ar/H<sub>2</sub> up to 1,000°C at atmospheric pressure. The annealing is done to increase the grain size and to minimize impurities. The annealed Ni substrate is exposed to a mixture of hydrogen and

methane gases. In this step the bonds of the methane break and the carbon atoms starts to diffuse inside the heated Ni substrate as shown in Figure 3.1 and form a solid solution. At the final stage of the CVD process the sample is cool down in the presence of Ar gas. At high temperature like 1,000°C compare to Cu, Ni has the highest carbon solubility and gradually decrease with decrease in temperature [27].

During the cooling down process the segregation of carbon atoms occurs which means that carbon atoms diffuse out towards the Ni surface to form graphene layers.

Figure 3.1: CVD method for Graphene growth step by step [28]

Ni is used mostly for graphene growth because Ni and graphene have relatively similar hexagonal lattice and similar lattice constant [29]. To grow single layer of graphene the

preferable metal substrate is Cu, because the solubility of carbon is less than as compare to Ni and for bilayer and beyond Ni is the best choice.

The growth of graphene on Ni substrate by CVD is a combination of two sub processes in which no 1 is the precipitation and the 2<sup>nd</sup> is the carbon segregation process. The segregation behavior is totally dependent on the cooling rates which directly effects the graphene thickness and the quality as well [30]. By medium cooling we can easily get few layers of graphene. Next the most important role in the graphene morphology is the structure and grain size in the Ni substrate.

T.H. Bointon et al, synthesized graphene by a new method known as a cold-wall chemical vapor deposition. They explained that this modified version of CVD is the most cost effective 99% cheaper than ordinary hot wall CVD and it is 100 times faster method for growing high quality graphene. Graphene produced through method has lowest defect density as observed by Raman Spectroscopy and the electron mobility's of  $3300 \text{ cm}^2/\text{V. S}$  measured through atomic force Microscopy also the quantum hall effect can be observed on single layer of graphene grown by this technique [31].

X.Chen, L. Zhang worked on the large area graphene grown by CVD. The main objective is to provide a detailed and recent review on the large area synthesis of graphene single, bilayer and multiple layers sing different substrate and upon the challenges in the production of

graphene. They used many target substrates like Cu, Ni, Pt, Ge, Ir, Co, Cu-Ni alloys which shows different growth manners in terms of single and multiple layers [32].

L.Huang, Q.H. Chang et al, reports the synthesis of high quality graphene on Ni substrate using a cold wall reactor by Rapid thermal chemical vapor deposition. In this new emerging method, they skip the step of carbon precipitation mechanism and used a shortest time of 10 seconds for production of graphene films. Their results show that the graphene grows in the absence of hydrogen precursor has the lowest sheet resistance of 367 ohm/sq and the optical transmittance of 97.3% for 550 nm wavelength which is much better than graphene grown by ordinary hot wall CVD method.

The data suggests that graphene grown on this method have comparable electrical and optical properties to those grown by CVD on Cu substrates [33].

They also find the graphene grown on such technique can be directly transferred to any target substrate without casting a PMMA to minimize the chance of any contamination and impurity.

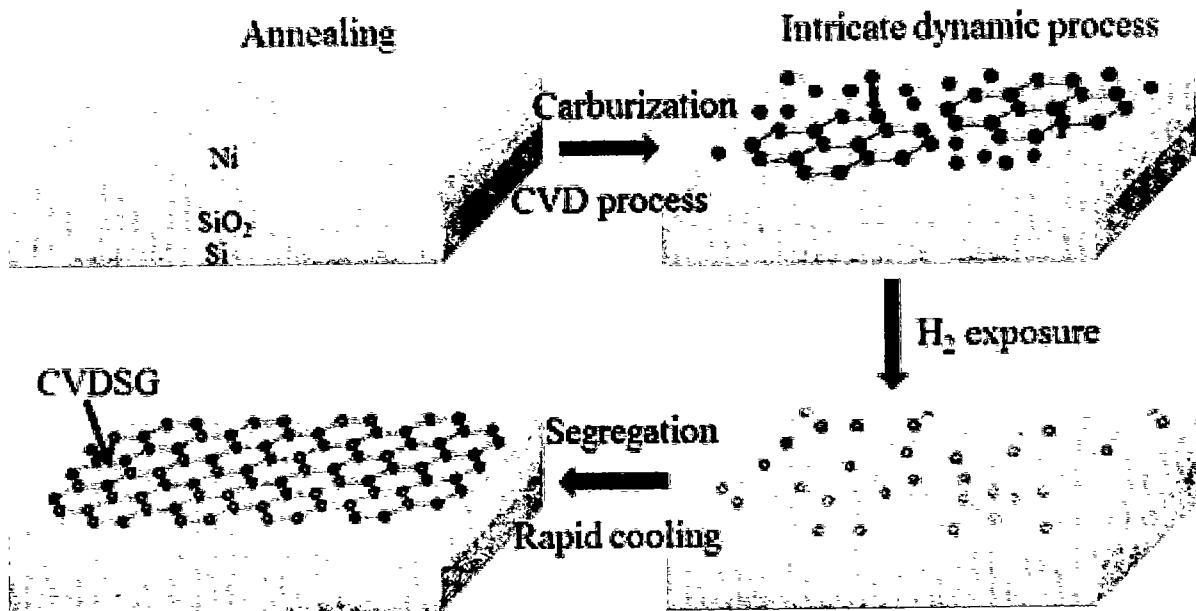

### **3.3 Graphene transistor matrix:**

The structure we are using in our research work is known as graphene transistor matrix. The growing technique is chemical vapor deposition in which graphene is directly deposited

on Ni/SiO<sub>2</sub>/Si. Ni is used as catalyst to grow graphene on its surface. The thickness of graphene surface is not uniform it vary from 1 to 10 layer due to the specific thickness of Ni.

The average is taken to be 4 layers with thickness of 1.23 nm measured by spectroscopic ellipsometer available in advance electronics lab at IIUI. The specification of the transistor matrix is listed below

- Wafer Size: 100 mm in diameter

- Growth Method: Chemical Vapor Deposition Technique

- Film thickness: 1-10 monolayer

- Average layers & thickness: 4 layers, 1.23 nm

- Graphene film is multilayer with thickness varying in the range 1-10 layers;

- Nickel film is deposited on the substrate covered by thermally grown oxide layer

- Ni layer thickness is 400 nm;

- silicon oxide layer thickness is 500 nm;

- The thickness of the wafer is 500  $\mu$ m;

- The crystallographic orientation of Si is 100 (Miller indexes);

- Defect density of films is very low;

Figure 3.2: graphene transistor matrix specification

### 3.4 Graphene metal interface:

As we study in chapter 2 that intrinsic graphene sometimes called the suspended graphene possess some extra-ordinary properties like the ballistic transport of charge carriers with the speed of light having no mass, highest electron mobility's, excellent conductor of heat and energy, optical transmittance of 97.3% and the young modulus of 0.5 TPa [34]. The most important property of graphene is that it's neither a metal neither semiconductor because the electron of graphene can only be characterized by Dirac cones which have the relativistic properties like light. There are some other related sub properties to the above mentioned in

which the first one is the lowest sheet resistance due to its 2D nature of graphene, the 2<sup>nd</sup> one is lower resistivity, the 3<sup>rd</sup> one is highest conductivity, the 4<sup>th</sup> one is carrier concentration and the 5<sup>th</sup> one is the mobility of graphene. Now the properties we discussed are directly affected when we make an interface of graphene with metals, semiconductors and insulators or graphene is sandwiched between other two materials may be between two metals or metal and semiconductor or metal and an insulator. This due to a fact that the fermi level of graphene changes when interfaced with another material which have different work function than graphene either the work function of the other material is less or greater than graphene due to which the fermi level of graphene changes this phenomenon is called the fermi level pinning. Here we are presenting a review on the previous work done on the graphene and metal interface.

C.Gong et al, investigated the first principal study of graphene and metal interface. They used 12 interface metal and study the electronic behavior of the interface structure, graphene doping types with the fermi level pinning and the doping density profile. They divided the interfaces in to physisorption and chemisorption. The metals like (Ag, Pt, Al, Au, Ir) forms a physisorption interface while the metals (Ti, Ni, Ru, Co, Pb) makes a chemisorption interface with graphene and concluded that for practical application the key parameter is the external

applied electric field which can be used to modulate the fermi levels and also to control the doping levels profiles [35].

Z. Xu et al, worked on the mechanical interaction of graphene and metal interface and focus on two the most important metal substrate Ni and Cu, because both of these metals used as a catalyst to grow graphene by the chemical vapor deposition process. The target is to find the mechanical interface cohesive energy, atomic geometry and strength. In their result they find out that due to same geometry and same lattice structure the interface between graphene and Ni has the highest cohesive energies than that of Cu interface with graphene. The results they found are totally based on density function theory [36].

### **3.5 Contact metals for graphene devices:**

As we know that intrinsic graphene has the highest electron mobility but when it becomes with contact its mobility degrades because the contact resistivity is the performance killer for graphene devices. The important thing is which kind of contact graphene form with different transition metals. Studies and experimental work suggests that many metal/graphene contacts are ohmic in nature due no band gap relatively similar to metals. The values of metal/graphene contact resistivity are very high due to some limitation, in terms of physics called the (DOS) density of states means that the density of states in graphene is very less causes the high contact resistivity. In this section of thesis, we are going

to discuss issues related to metal/graphene interface effects on contact resistivity and the methods to reduce the contact resistance, also the techniques to find the contact resistance.

### **3.5.1 Carrier injection:**

The tunneling current which enters from metal to graphene, if we look at it by the view point of electrical transport which is directly proportional to the density of states and so to the transmission probability. We know that density of states of metal/graphene has inverse relation with the contact resistivity [37]. Also by considering the term transmission probability, the important factor included is the momentum of charge of the charge carriers and the separation distance between metal and graphene. Now it is totally dependent upon the metal whose charge carrier's matches with that of graphene charge carriers. Another important factor is the fermi wave number, larger the fermi wave number so the larger is the fermi wave sphere and it will make the separation distance increase. For example, the Al and graphene have high contact resistivity due to the oxidation of Al in open air and can be used as top gate insulator.

TH-16096

The grain size of the deposited metal on graphene surface creates fluctuations and causes to increase the contact resistivity [38]. Also to create density of states in graphene by chemical doping or by ion implantation, it is not an easy task because the C-C bond is very strong so it will need a lot of energy to break the bonds. Theory suggests that the metal/graphene

interface can be divided into two groups one is physisorption and the other is a chemisorption group. These groups are already briefly discussed in the previous section. The method to calculate the density of states in graphene includes the scanning tunneling microscopy, photo-emission spectroscopy and the C-V analysis.

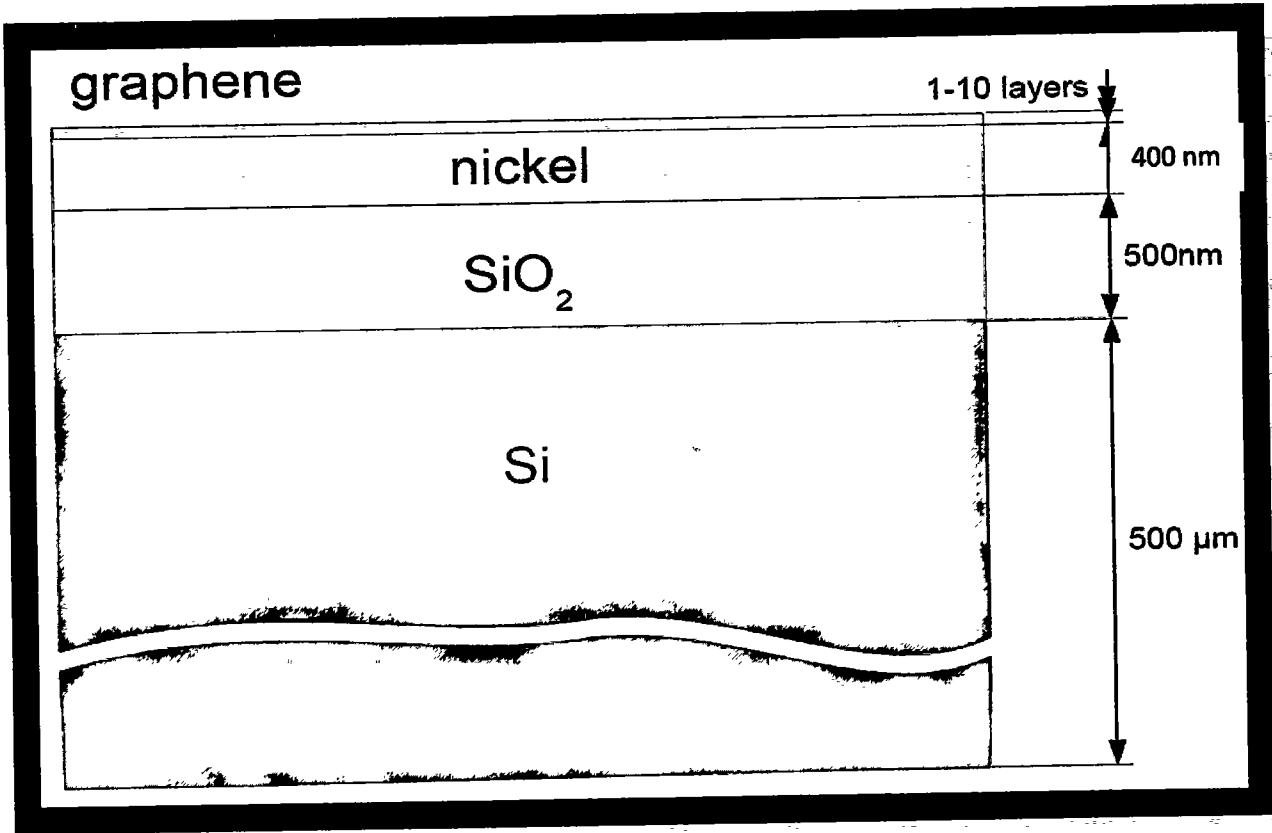

### 3.5.2 Energy band diagrams:

As we know that a metal and semiconductor form a schottky contacts while the metal/metal contacts are ohmic in nature. Now in the case of graphene the metal/graphene the situation is quite similar to that of metal/metal ohmic contacts because the graphene is a semi-metal with zero bandgap. The bandgap engineering in metal/semiconductor, metal/metal, and metal/graphene are shown in Figure 3.3:

Figure 3.3: energy band diagram for (a) metal/semiconductor (b) metal/metal (c) metal/graphene contacts.

Figure 3.4: The relation between the density of states and the energy at the metal/graphene interface (a) before and after the contact formation (b) physisorption metal (c) chemisorption metal [39]

Figure 3.2 and Figure 3.3 shows the complete process in terms of energy band diagrams that's how charges can transfer from metal to graphene surface in case of chemisorption and physisorption contacts. The finding shows that the graphene work function is 4.5 eV [40].

Now what is the practical methodology to find the contact resistivity of metal/graphene interface? The most reliable method for this purpose is the (TLM) transfer length method which will be explained in the next chapter based on the characterization techniques.

### **3.6 Graphene Field Effect Transistor:**

As we know that generally an FET (Field Effect Transistor) is composed of 3 electrodes known as source, gate and drain and during the conduction mode the majority and minority carriers are actually dependent upon the doping types of the substrate. For example, in n-MOSFETs the electron are the minority carriers due to the p-type doped substrate. Similarly, a dual-gate FET has four has four electrodes and it has advantage over ordinary single gate FET in terms of high switching rates, low power consumption and minimum noise. The 3 electrodes in FET are equivalent to emitter, base, and collector in BJT. Recently there are different types of FETs has been developed for the requirements of modern technology application, some of them are silicon, carbon nanotube, organic field effect transistors and so on. But some of them are not actually fulfilling the requirements for current and future technology application in terms operating frequency, miniaturization in size, noise, leakage currents etc. According to Moore's law the no of transistors in densely packed are should become double every two years, so to fulfill the prophecy of Moore's law we should have to miniaturize the size of transistor every two years. But now we are at the stage that further miniaturization of these devices and materials from which they are fabricated are not thermodynamically stable at room temperatures so we have to rely on some other emerging materials which would be thermodynamically stable in this critical situation and can be

further miniaturized to keep going on the Moore's law. This leads us to a new era of two dimension materials and the most promising is the Graphene. As discussed in the early topics the complete details about graphene that why it is so important to use graphene due to its some extraordinary properties

### **3.6.1 Graphene-FETs:**

Graphene has the highest electron mobility and quite unique band structure which makes it a suitable candidate to be used for field effect transistor applications. To overcome the encountered obstacle in carbon nanotubes, silicon nanowires and organic materials graphene can be used as a channel material in the field effect transistors. The most important thing about graphene FETs that it can follow Moore's law and can further be miniaturized.

### **3.6.2 Field Effect in Graphene:**

Graphene a semi metal with zero band gap and the charge carriers according to fermi Dirac statistics having no mass and can be converted from holes to electron and from electron to holes by applying an electric potential also at the Dirac point the electric field as well as the concentration of charge carriers becomes zero [41]. Positive voltage at gate input graphene becomes an electron conductor while negative voltage at gate input graphene conducts holes as a majority carrier. From quantum hall effect theory, in an experiment from

conductivity and hall coefficient we conclude that gate voltage is responsible for converting the charge carriers from holes to electron and vice versa.

### 3.7 Graphene FETs Structures:

The highest electron mobility and unique band structure makes graphene a promising material for transistor application like FETs. Here we are discussing different structures of graphene based field effect transistors.

#### 3.7.1 Back-gated GFETs:

In this model the CVD graphene is transferred to a dielectric substrate or directly grown on the dielectric surface by roll to roll method. A lithographic and reactive ion etching are performed to make metal electrodes on surface of graphene. The first graphene channel based back-gated field effect transistor was fabricated by the graphene inventor K. Novoselove and his team in 2004 as shown in Figure 3.5:

Figure 3.5: (a) schematic diagram (b) SEM image of back-gated FET [42]

In the above image the slight darker part is graphene channel while the darker part the dielectric layer of silicon dioxide.

### 3.7.2 Graphene top-gated FETs:

Here in this model a CVD grown graphene film is used as a channel material while silicon dioxide or PMMA is used as a gate dielectric as shown in Figure 3.5.

Figure 3.6: schematic diagram of graphene top-gated FET [42]

The metal gate is fabricated on the surface of dielectric. In circuit application point of view, the top-gated GFETs are more flexible than back-gated GFETs but the carrier's mobility is lower than back-gated GFETs. The reason is that the gate insulator scatters the charge carriers. Another dis-advantage of top-gated GFETs is that during the fabrication of top gate the chances for graphene damage increases throughout the processes. So here we conclude that getting high carrier's mobility using a top-gated graphene FET is very crucial and need very fine processing steps to fabricate it.

### 3.7.3 Dual-gated GFETs:

Here we are using two gates one top and another back gate. The highly doped silicon is used as a back gate while the metal electrode is used as a top gate as shown in Figure 3.6.

Figure: 3.7: Schematic of dual-gated graphene field effect transistor [43]

The model shown above is designed to study the I-V characteristics of graphene channel. Poisson equations are used to evaluate the top and back gate voltage parameters. The theoretical and experimental work combine shows that the top gate voltage remain low, no matter how much you increase the current across the source-drain.

## Chapter 4: Characterization Techniques, Material & Equipment's

### 4.1 Electrical characterization:

There are basically three stages of evolution in electrical characterization of materials. In the 1800s the conductance  $G$  and the electrical resistance  $R$  were considered to be the physical quantities to characterize any material under consideration. Both  $R$  &  $G$  were obtained from the I-V curve. But later on experiments showed that resistance  $R$  is not uniform for different shapes and geometries of same material, which means that different the geometry different the resistance value. To solve this, issue the concept of electrical resistivity (2<sup>nd</sup> level) comes to existence and it was proved that electrical resistivity or electrical conductivity is inherent property of intrinsic material and it is independent of the shape and geometry of the substance. This concept first times allowed scientists in history to experimentally classify the current carrying capacities of different materials.

Next in first decade of the 1900s scientists realize that resistivity is not the only fundamental parameter to electrically characterize any material [44]. This is due to the reason that there exist many material having different shapes and different geometrical structures but yet they have same electrical resistivity values, also many same materials may give different electrical resistivity values due to different techniques upon which they are synthesized which is a special case for semiconductors due to non-uniform doping profile. So it is clear in case of semiconductor only electrical resistivity is not enough for electrical characterization. So to overcome this issue quantum mechanical theories plays an important role and leads us to a 3<sup>rd</sup> level to use some new parameters like the electron mobility  $\mu$  and the carrier concentration to characterize the semiconductor materials.

## 4.2 Hall Effect:

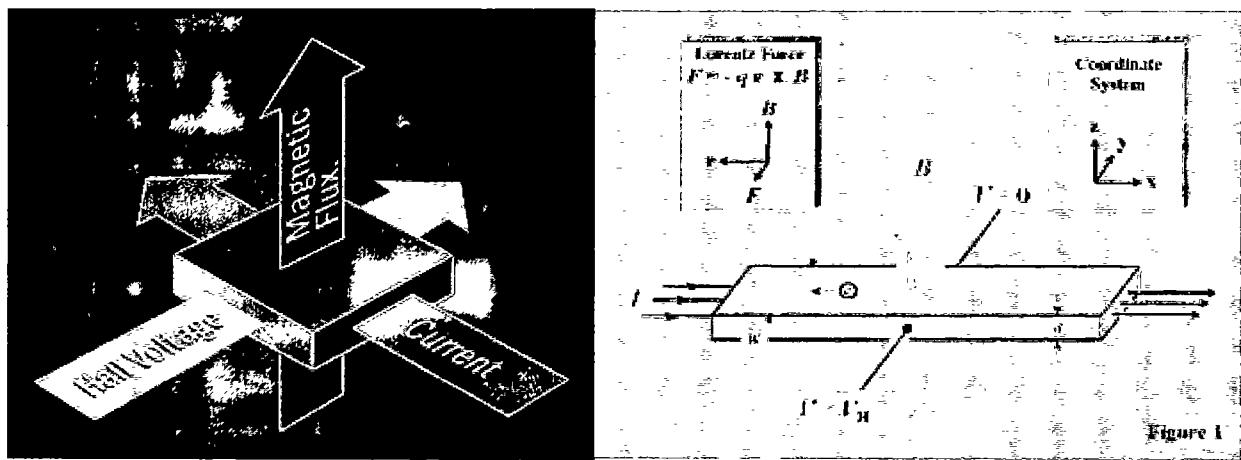

In 1879 Edwin Herbert Hall at John Hopkin University discovered the Hall Effect 18 years before the discovery of electron [45]. Behind the Hall Effect is the basic physical principle of Lorentz force which is composition of two forces, the electric and the magnetic force. When a magnetic force is applied at right angle to a current carrying wire/slab so a new force can be observed due to the combined effects of electric and magnetic force. This electromagnetic force is perpendicular to both these forces and known as a Lorentz force. The direction of Lorentz force may be in both normal so to find its direction the concept of right hand rule will be used. Mathematically we can write the Lorentz force as follows

$$\mathbf{F} = -q(\mathbf{E} + \mathbf{v} \times \mathbf{B}) \quad \dots \dots \dots \quad (1)$$

In the above equation  $q = (1.602 \times 10^{-19} \text{ C})$  is elementary charge on electron,  $E$  is the electric field,  $V$  is the charge carrier velocity and  $B$  is the magnetic field strength. For an n-type semiconductor as shown in Figure: 4.1 below:

Figure 4.1: (a) basic schematic of Hall Effect (b) Hall Effect for n-type semiconductor (special case)

Let us assume that a uniform current flowing along the x-axis and the magnetic force is applied perpendicular along the z direction so the electron drift towards the y direction due to the Lorentz forces causing the excess of electron toward one side of the sample. This excess charges produce a voltage known as Hall Voltage is its magnitude is:

$$V_H = IB/\text{and} \quad \dots \dots \dots \quad (2)$$

In equation 2 above  $d$  is sample thickness,  $B$  is magnetic field strength,  $q$  is charge on elementary particle, "n" is bulk density and  $I$  is the current. For a two dimension slab the term sheet density ( $n_s = nd$ ) will be used instead of bulk density and equation no 2 in terms of sheet density can be written as follows:

to calculate sheet density  $n_s$  we have to first find the Hall voltage and then by knowing all other parameters  $B$ ,  $I$ ,  $q$  the sheet density can easily be found. The Hall voltage may be negative or positive it depends upon the type of semiconductor. Normally for n-type the Hall voltage is negative while for p-type semiconductor it observed to be positive. Conventionally the sheet resistance of a semiconductor can be found by the Van der pauw technique and will be discussed in the next topic.

To find the sheet resistance first we must know the values of sheet density as well as the electron mobility. The equation for mobility is:

If thickness "d" of the slab is known so we can easily calculate the bulk density and resistivity as well.

### 4.3 The Van der Pauw method:

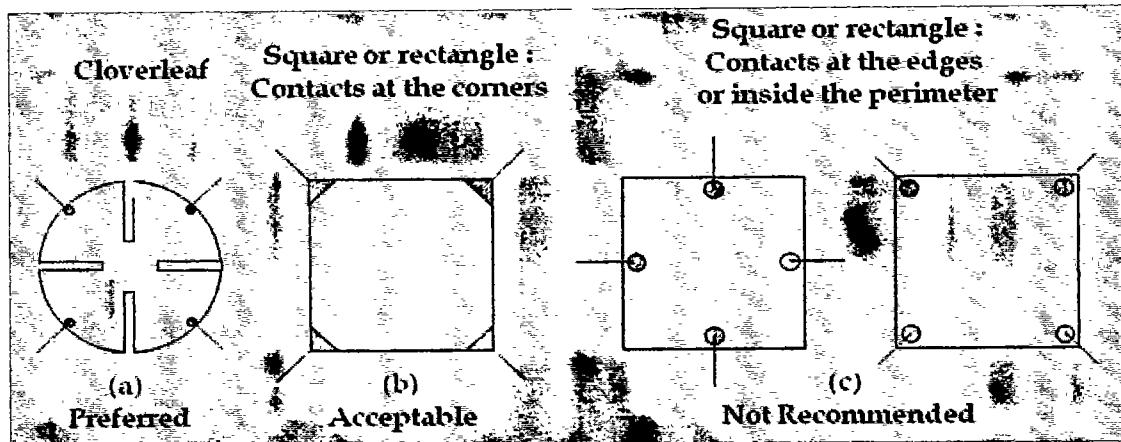

The Van der pauw method was first propounded by L.S. Van der pauw in 1958 [46] and commonly used to measure the Hall coefficient, resistivity and other properties of any 2D arbitrary shape sample. By this technique we can find the resistivity, doping type, carrier density and mobility of sample. Before using this technique there are some condition to be satisfied like the sample we are using for this technique should be perfectly flat with uniform thickness, next the sample should be isotropic and homogenous and contain no fracture defects or isolated holes, also the probe should be placed on the perimeter of the sample.

Possible sample geometries are shown in fig 4.2 below

Fig 4.2: possible sample geometries for Van der pauw technique.

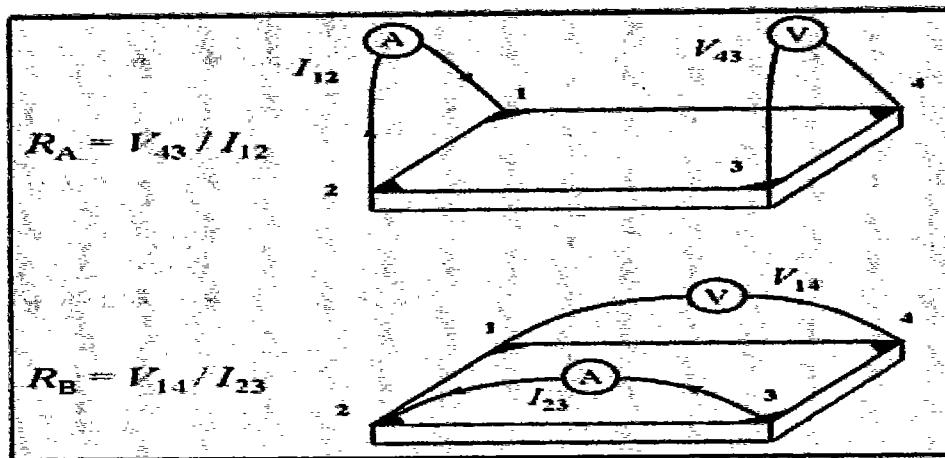

#### 4.3.1 Methodology:

To find the mobility and sheet density the Hall measurements and resistivity measurements are needed. From resistivity measurements we calculate the sheet resistance  $R_s$ . In Van der pauw we have two types of characteristics resistances known as the  $R_A$  and  $R_B$  with respect to the terminals shown in fig 4.3 on the next page. Both the resistances  $R_A$  and  $R_B$  according to the van der pauw equation have the following relation with the sheet resistance.

and can be solved for sheet resistance as follows:

Figure 4.2(b): The Van der pauw terminal setup for finding  $R_A$  and  $R_B$

The electrical resistivity of bulk can be calculated as:

To practically calculate the characteristics resistances  $R_A$  and  $R_B$  a dc current is pass through contact 1 and 2 and the voltage is measured across contact 3 and 4, next the current is passes through contact 2 and 3 and the voltage is measured across 1 and 4 shown in Figure 4.2 above.  $R_A$  and  $R_B$  can be calculated as:

By putting equation (8) in equation (6) we can find the sheet resistance  $R_s$ .

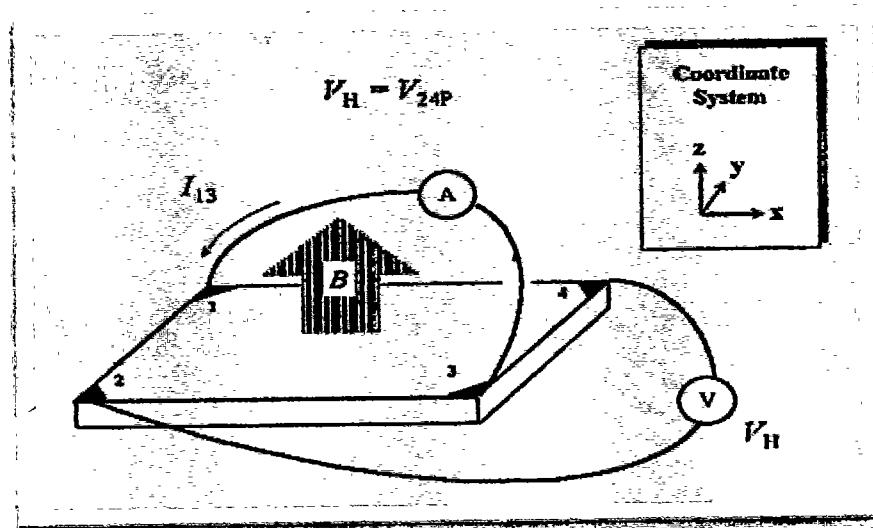

To find the sheet carrier density by using the van der pauw method we to need the Hall voltage so we have to perform the Hall effect measurements. In Hall Effect measurements we

have a constant magnetic field and a constant current while the voltage varies as the setup shown in Figure 4.3:

Figure 4.3: schematic of Hall measurements

As we see in Figure current is applied through contact 1 and 3 and the voltage  $V_H$  ( $= V_{24}$ ) is measured and now by applying the formula of equation (3) we can get the sheet carrier density  $n_s$ .

There are some precautions for Hall measurements to be kept in mind.

- (1) The contact must be ohmic and should be of precise size required for hall measurements.

- (2) The thickness of the sample uniform and also known

- (3) During experiments the photoelectric effect must be minimum because some materials are sensitive to light so the experiments must be carried out in dark room

- (4) Hall measurements needs uniform temperature because the non uniform temperature may create the thermomagnetic effect.

#### 4.4 Transmission Line Measurements:

The transmission line method/transfer length method is a technique to find the value of contact resistance between metal/semiconductor junction. As we see in the Van der pauw method that 4 metal contacts were deposited on each corner of the sample to measure the sheet resistance and it was also mentioned that the contact should be ohmic in nature to minimize the contact resistance. But still there were contact resistance but we neglect it because it was consider to be minimum but in case of device performance like transistor application in modern technology it the major herdle in grpahene transistors. So in this section of the thesis we are going to discuss the methods to find the contact resistance of graphene and metal juntion by the new method of transfer length method. There are other methods too as shown in Figure 4.4, but the TLM is known to be an industrial standered so we will focus the TLM only.

Figure 4.4: (a) Four-probe measurement, (b) transfer length technique (c) cross-bridge Kelvin technique [47]

#### 4.4.1 Methodology of TLM:

##### Step1: junction preparation:

The first step is to deposit the metal contacts by mean of any technology like thermal evaporation and pattern them in form of metal pads separated by a distance apart as shown below:

Figure 4.5: Metal pattern for TLM separated by a varying distance

The size of the pads must be the same but the distance after each pad must vary. After the formation of metal pads the annealing must be done so the metal may diffuse to form a junction with semiconductor or in our case is the graphene.

##### Step 2: Measurements:

In this step we have take the simple I-V readings to calculate the resistance between each pad. The method is very simple it can easily be done at the probe station or some other parameter analyzer. Resistance should be found by simple  $R=V/I$

### Step 3. Contact resistance calculation:

As shown in Figure 4.6 the resistance between any two pads can be consider as three resistor in series, one from metal to graphene/semiconductor, through the graphene, back to metal. Since as we mention before that the contact should be ohmic in nature so the polarity of the input voltage source produce no difference so the total resistance between each consecutive pads are:

Now we have to plot the resistance of the two pads vs the distance they apart from each other we get a graph like this shown in Figure 4.6.

Figure 4.6: plot between resistance and separation of 2 pads.

If the two pads are so close to each other that the distance between them becomes zero so according to equation (9) we can write as

$$R_t = 2R_{\text{pad}} \dots \quad (10)$$

From equation (10) we can easily find the contact resistance and by putting it in equation (9) we can calculate the resistivity of graphene/semiconductor.

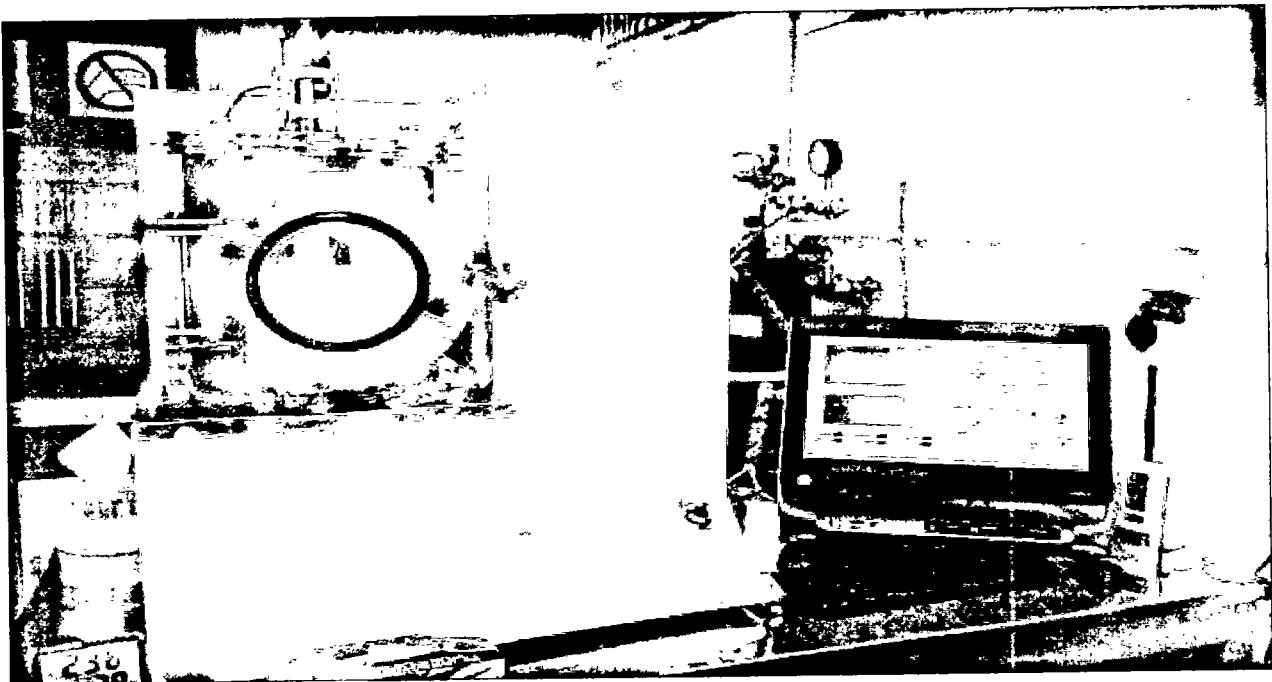

## 4.5 Equipments:

In this section of the thesis we are going to discuss about the equipments which we are used throughout our research. Each individual is listed by name as below

- (1) Nano-chip reliability grade hall effect system

- (2) Automatic system of materials electro-physical characterization

- (3) Thermal evaporator

- (4) Rapid thermal annealer

All these equipments mentioned above are present in working condition at (AEL) Advance Electronics Lab International Islamic University funded by the Islamic Development Bank. Now we are going to discuss each equipments one by one in detail and the role of each equipment in our research.

### 4.5.1 Nano-chip reliability grade Hall Effect System:

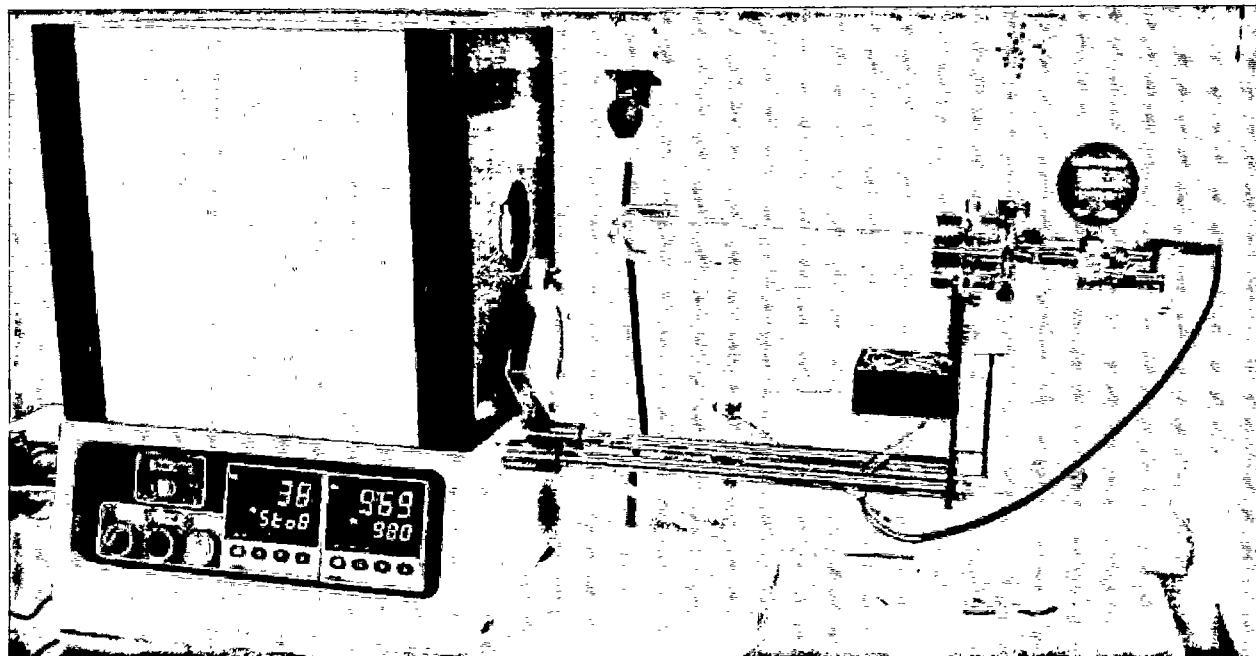

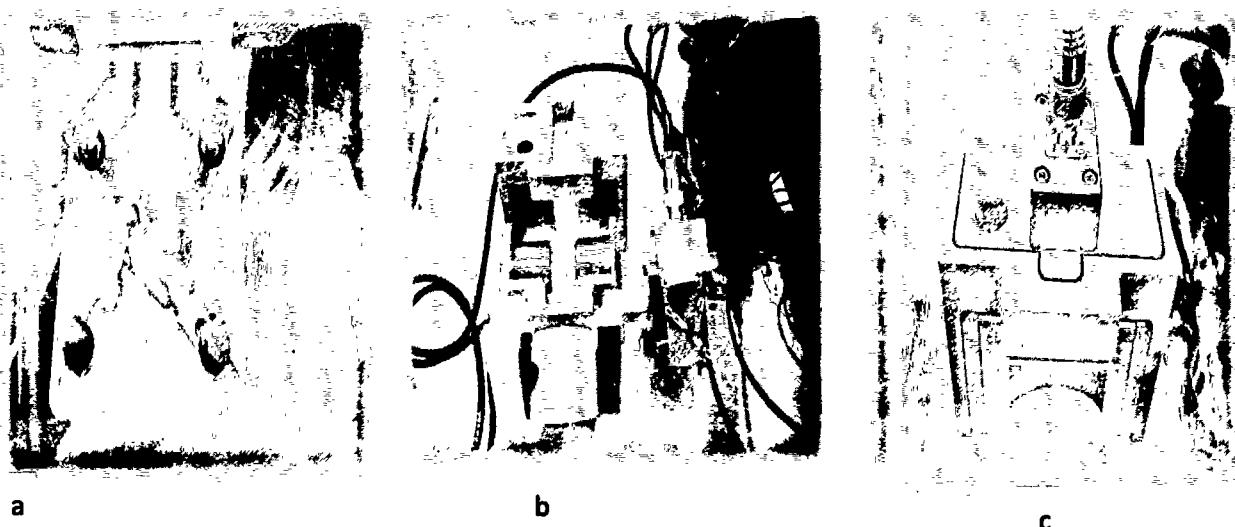

The basic principle behind the nano-chip reliability grade Hall Effect system is the theory of Hall Effect system or we can say here we practically exercise the Hall Effect theorem. Hall Effect system is completely discussed in the previous section of this chapter with detail. Here we are discussing the practical application of Hall Effect system. The nano-chip reliability grade Hall Effect system has the following units also shown in Figure 4.7:

|                         |                          |

|-------------------------|--------------------------|

| Accusation unit         | Sample Assembly          |

| Permanent Magnet        | Special grade axial wire |

| Liquid Nitrogen Chamber | Funnel                   |

Figure 4.7: The basic units of nano chip reliability grade hall effect system. The image is taken by the authority permission of Advance Electronic Lab International Islamic University Islamabad.

The nano-chip reliability grade Hall Effect system is a device probing technique and use the Van der pauw 4 point probing technique for sample preparation and characterization as explained before in details.

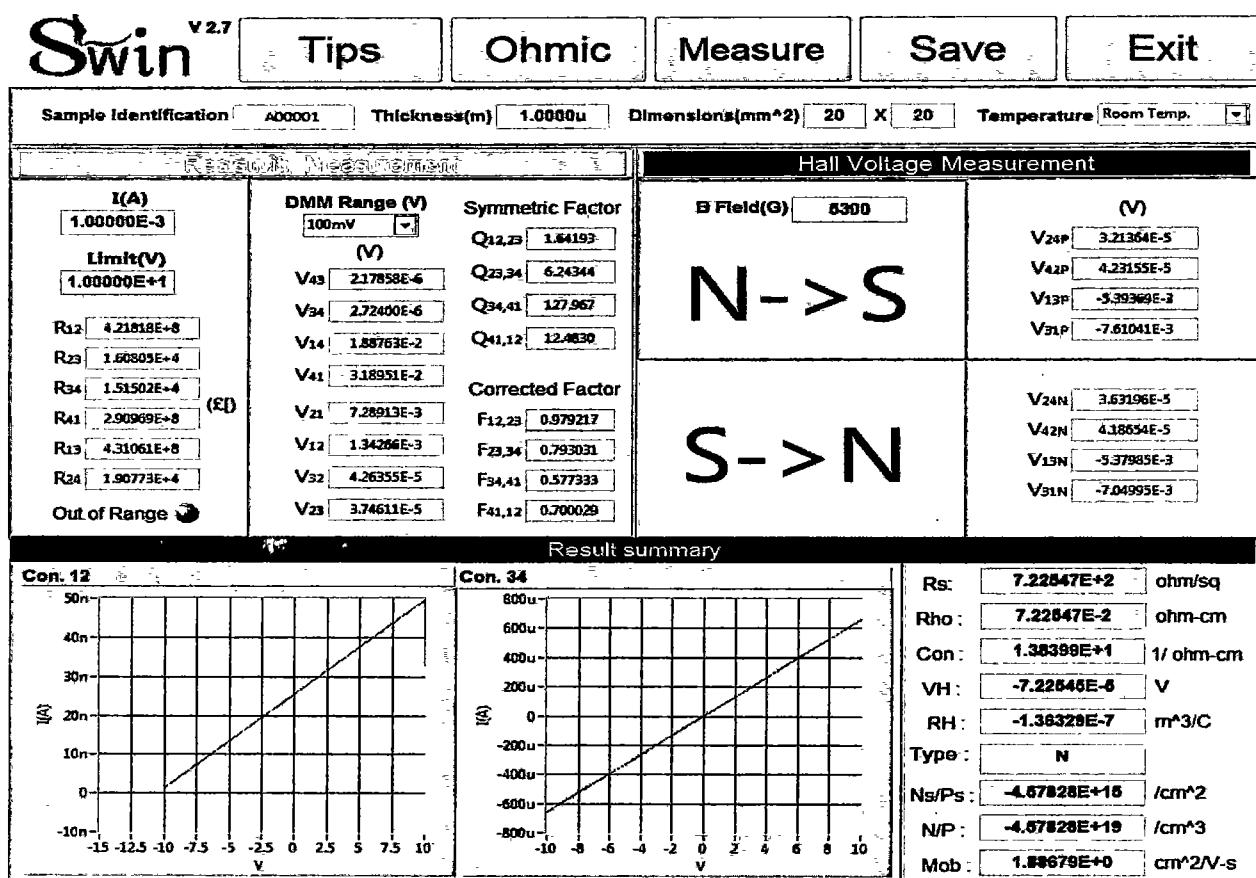

#### **4.5.2 Application & Specification:**

Application include a variety range of DC field measurements like wafer scale mobility as function of temperature and magnetic field, cryogenic and high temperature ranges during measurements, data acquisition and system level analysis by intuitive built in software and supports exportation of data for Hall multi carrier analysis which include (sheet resistance,

electrical resistivity, electrical conductivity, Hall voltage and Hall Coefficient, nature of the conductivity, bulk concentration and mobility).

The system specification is shown in table 4.1:

|                                     |                                                                               |

|-------------------------------------|-------------------------------------------------------------------------------|

| <b>Sample size</b>                  | 10mm x 10mm ~ 15mm x 15mm                                                     |

| <b>Operating temperature ranges</b> | Elevated, Ambient Room Temperature and cryogenic                              |

| <b>Materials measurements range</b> | Si, Ge, SiGe, SiC, GaAs, InGaAs, InP, GaN, ZnO, Graphene, Nano Particles etc. |

| <b>Magnetic Flux Density</b>        | 0.53 Tesla                                                                    |

| <b>Current Sensitivity</b>          | 2 nA                                                                          |

| <b>Input Voltage ranges</b>         | 1µV-300V                                                                      |

| <b>Carrier Density range</b>        | $10^7 - 10^{22} \text{ (cm}^{-3}\text{)}$                                     |

Table 4.1: Nano chip reliability grade Hall Effect system specification

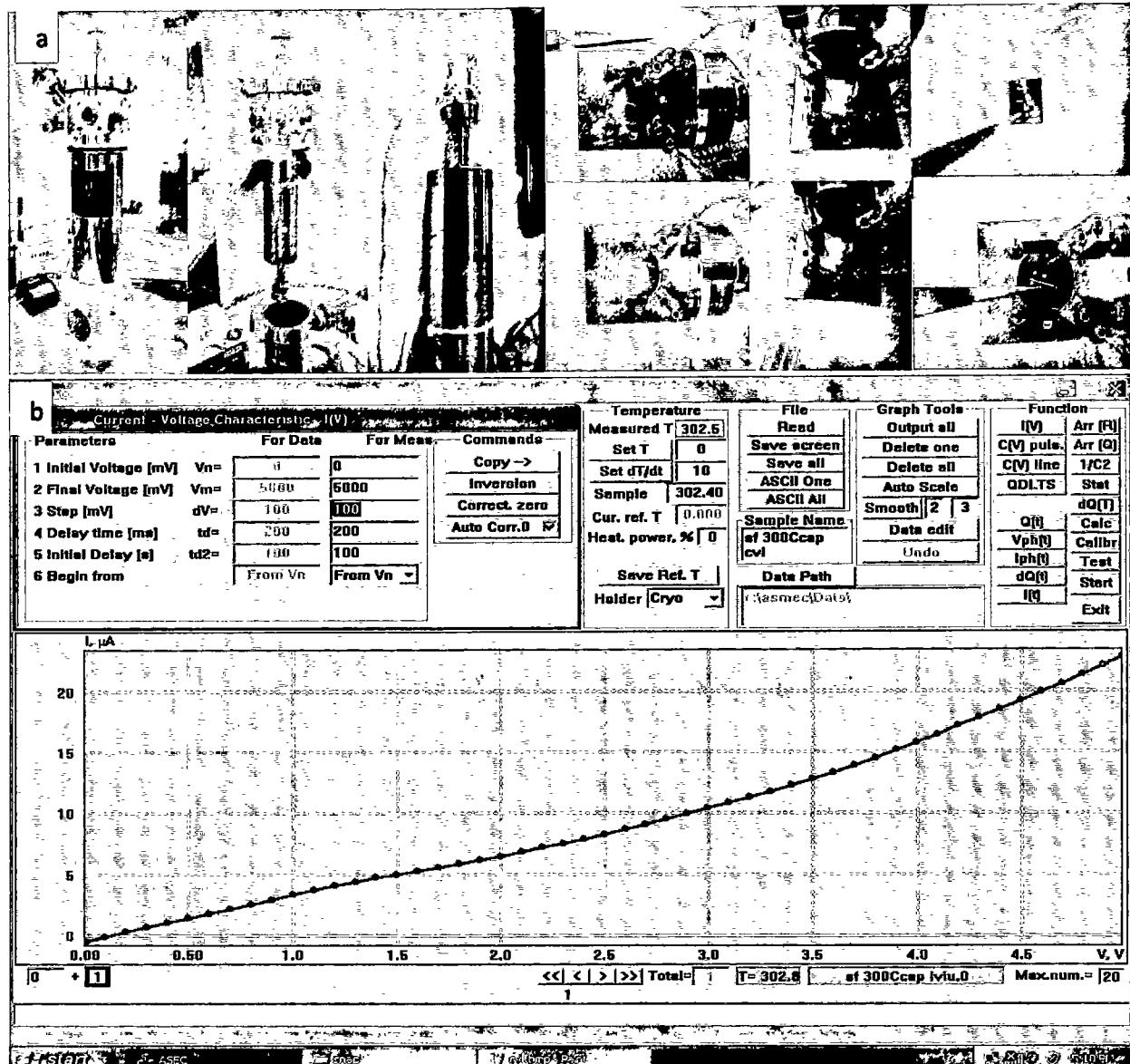

#### 4.5.3 Automatic System of Material Electro-Physical Characterization: