# **Simulation, Fabrication and Characterization of Ultra Shallow Junction in CMOS**

**By**

**REHANA MUSTAFA**

**(6-FBAS/PHDPHY/S10)**

**Department of Physics

Faculty of Basic and Applied Sciences

International Islamic University Islamabad**

Accession #: TH-14547 ④

PhD

621-38173

RES

- International Technology Roadmap of Semiconductors (ITRS)

- Electrical and Electronic Engineering

- Electronics

**SIMULATION, FORMATION AND

CHARACTERIZATION OF ULTRA SHALLOW

JUNCTION IN CMOS**

**By**

**REHANA MUSTAFA

(6-FBAS/PHDPHY/S10)**

**Supervisors**

**Prof. Dr. Ehsan Ullah Khan**

**Prof. Dr. Ahmed Shuja Syed**

**A THESIS IS SUBMITTED

FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

DEPARTMENT OF PHYSICS FACULTY OF BASIC

AND APPLIED SCIENCES INTERNATIONAL

ISLAMIC UNIVERSITY ISLAMABAD**

**DEPARTMENT OF PHYSICS

FACULTY OF BASIC AND APPLIED SCIENCES

INTERNATIONAL ISLAMIC UNIVERSITY,

ISLAMABAD PAKISTAN**

**Simulation, Formation and Characterization of Ultra Shallow

Junction in CMOS**

By

**REHANA MUSTAFA**

(Registration No. 6-FBAS/PHDPHY/S10)

A thesis is submitted to

**Department of Physics**

For the award of the degree of

**Doctor of Philosophy in Physics**

Signature

(Chairperson, Department of Physics)

**CHAIRMAN**

**DEPT. OF PHYSICS**

International Islamic University/

Islamabad

Signature

(Dean FBAS, IIUI, Islamabad)

**Department of Physics

Faculty of Basic and Applied Sciences

International Islamic University, Islamabad**

Date: 03/01/15

**Final Approval**

It is certified that the work presented in this thesis entitled "Simulation, Formation and Characterization of Ultra Shallow Junction in CMOS" submitted by Rehana Mustafa, Registration No. 6-FBAS/PHDPHY/S10 is of sufficient standard in scope and quality for the award of degree of PhD Physics from International Islamic University, Islamabad

**COMMITTEE**

26/1/15

Dean

Chairperson/Head of Department

External Examiner

Supervisors

Member

A thesis is submitted to

**Department of Physics**

International Islamic University Islamabad

As a partial fulfillment for the award of the degree of

**Doctor of Philosophy**

## **DECLARATION**

It is hereby declared that this thesis work, neither as a whole nor a part of it has been copied out from any source. Further, work presented in this dissertation has not been submitted in support of any application for any other degree or qualification to any other university or institute and is considerable under the plagiarism rules of Higher Education Commission (HEC) Pakistan.

**Rehana Mustafa**

**(6-FBAS/PHDPHY/S10)**

## **CERTIFICATE**

It is certified that Rehana Mustafa Registration No. 6-FBAS/PHDPHY/S10 has carried out the research work related to this thesis titled, "Simulation, Formation and Characterization of Ultra Shallow Junction in CMOS" under our supervision. This work fulfills all the requirements for the award of the doctor of philosophy.

**(Prof. Dr. Ahmed Shuja Syed)**

**(Prof. Dr. Ehsan Ullah Khan)**

## ACKNOWLEDGEMENT

All praise and glory to Allah almighty, the compassionate and the merciful, who granted me the ability to complete this dissertation. Although my Ph.D. research experience is one which will not soon be forgotten. The last three years have been characterized by often-times excruciating frustration, punctuated by moments of clarity. For all that however, it has been a period of commensurate rewards and enlightenment. In the course of this work, I am truly thankful and grateful to the many wonderful people I have had the honor of meeting, interacting with and learning from. First, I wish to thank my supervisors, Prof. Dr. Ehsan-Ullah Khan and Prof. Dr. Ahmad Shuja for their support, patience and kind guidance during my research work at the department of Physics, International Islamic University, Islamabad. I am indebted to Prof. Dr. Ahmad Shuja for affording me the opportunity to undertake such an edifying venture. This is to say nothing of his ceaseless support, direction and (at times most important) patience over the years of the project.

Dr. Arshad Saleem Bhatti and Dr. Anees-Ur-Rehman from department of physics COMSATS Institute of Information Technology are owed a deep debt of gratitude for their assistance with sample annealing, electrical characterization and structural characterization. For RBS measurements, I am also thankful to Dr. Khurram and Turab Ali from National Center for Physics (NCP) Islamabad Pakistan. I am also thankful to Dr. Shaista Shehzada for providing me access of Ellipsometer facility. I am really really thankful to chairman department of physics Dr. Waqar Adil Syed for resolving my departmental issues.

I am also really thankful to Higher Education Commission (HEC), government of Pakistan for providing me Indigenous scholarship to complete my PhD research work. I am also thankful to all of my group members for their cooperation and nice company.

I really appreciate and express my profound admiration to my father Haji Ghulam Mustafa, my mother Ghulam Fatimah, my brother Moazzam Mustafa and my sisters Munazzah Mustafa and Samrana Mustafa for providing physical and moral support during my whole PhD duration. I would essentially have not been able to achieve this noble goal without their help and kind behaviors. At last I am very thankful to my own family, my husband and children especially my children who suffered most during my whole PhD duration.

---

# **Simulation, Formation and Characterization of Ultra Shallow Junction in CMOS**

## Table of Contents

### Chapter No. 1      Introduction

|     |                            |   |

|-----|----------------------------|---|

| 1.1 | Introduction               | 1 |

| 1.2 | Scope of the Thesis        | 2 |

| 1.3 | Objectives of the Thesis   | 3 |

| 1.4 | Organization of the Thesis | 4 |

### Chapter No. 2      Background Theory

|           |                                                               |    |

|-----------|---------------------------------------------------------------|----|

| 2.1       | Description of Physical Phenomenon and Background Physics     | 5  |

| 2.1.1     | Shallow and Ultra Shallow Junctions                           | 5  |

| 2.1.2     | Simulation Techniques                                         | 6  |

| 2.1.2.1   | Simulators Used for Implantation Optimization (SRIM & SUSPRE) | 7  |

| 2.1.2.2   | Simulator used for Process Optimization (TCAD)                | 8  |

| 2.1.3     | Ion Implantation                                              | 8  |

| 2.1.3.1   | Ion Stopping and Range                                        | 9  |

| 2.1.3.2   | Implant Damage                                                | 11 |

| 2.1.4     | Annealing                                                     | 12 |

| 2.1.4.1   | Rapid Thermal Annealing (RTA)                                 | 14 |

| 2.1.4.2   | Furnace Annealing                                             | 16 |

| 2.1.5     | Theory of Electrical Characterization Techniques              | 17 |

| 2.1.5.1   | Hall Measurement System                                       | 17 |

| 2.1.5.1.1 | History of Hall Effect                                        | 18 |

| 2.1.5.1.2 | The Hall Effect and the Lorentz Force                         | 18 |

| 2.1.5.1.3 | The Van der Pauw Technique                                    | 20 |

| 2.1.5.2   | Semiconductor Characterization System Keithley's Model 4200   | 21 |

| 2.1.5.3   | CV System                                                     | 22 |

| 2.1.6     | Ellipsometry                                                  | 22 |

| 2.1.7     | X-Ray Diffraction                                             | 24 |

| 2.1.7.1   | Historical Background                                         | 24 |

| 2.1.7.2   | Bragg's Law                                                   | 25 |

| 2.1.7.3   | Kinematical Theory of X-Ray Diffraction                       | 26 |

| 2.1.8     | Rutherford Backscattering Spectroscopy (RBS)                  | 26 |

| 2.1.9     | Introduction of Grazing Incidence X-Ray Fluorescence (GIXRF)  | 28 |

|                                                        |                                                               |     |

|--------------------------------------------------------|---------------------------------------------------------------|-----|

| 2.1.10                                                 | Atomic Force Microscopy (AFM)                                 | 29  |

| <b>Chapter No. 3 Literature Review</b>                 |                                                               |     |

| 3.1                                                    | History of CMOS                                               | 31  |

| 3.2                                                    | Trends in Ultra Shallow Junction (USJ) Devices                | 37  |

| <b>Chapter No. 4 Experimental</b>                      |                                                               | 40  |

| 4.1                                                    | Simulation Techniques                                         | 40  |

| 4.1.1                                                  | Stopping and Range of Ions in Matter                          | 40  |

| 4.1.2                                                  | Technology Computer-Aided Design                              | 42  |

| 4.2                                                    | Experimental Ion Implantation                                 | 43  |

| 4.2.1                                                  | Ion Implanter                                                 | 45  |

| 4.3                                                    | Annealing Techniques                                          |     |

| 4.3.1                                                  | Rapid Thermal Annealing (RTA) and Furnace Annealing           | 46  |

| 4.4                                                    | Electrical Characterization Technique                         | 51  |

| 4.4.1                                                  | The Van Der Pauw Technique                                    | 51  |

| 4.4.2                                                  | Semiconductor Characterization System Keithley Model 4200     | 53  |

| 4.4.3                                                  | CV Measurements Technique                                     | 54  |

| 4.5                                                    | Setup and Measurements of Ellipsometry                        | 56  |

| 4.6                                                    | X-Ray Diffraction Measurement                                 | 60  |

| 4.7                                                    | Rutherford Back Scattering Setup and Measurements             | 62  |

| 4.8                                                    | Grazing Incidence X-Ray Fluorescence setup and Measurements   | 65  |

| 4.9                                                    | Atomic Force Microscopy (AFM)                                 | 69  |

| <b>Chapter No. 5 Results, Discussions and Analysis</b> |                                                               |     |

| 5.1                                                    | Analysis of Simulated Results                                 | 72  |

| 5.2                                                    | Description of Electrical Characterization                    | 76  |

| 5.3                                                    | Analysis of Ellipsometric Measurements                        | 82  |

| 5.3.1                                                  | One Layer Model for the Measurement of thickness              | 82  |

| 5.3.2                                                  | Formula Derivation for Thickness Measurement                  | 83  |

| 5.3.3                                                  | Measurement Analysis                                          | 85  |

| 5.4                                                    | Analysis of RBS Results                                       | 93  |

| 5.5                                                    | Results and Discussions of X-Ray Diffraction                  | 102 |

| 5.6                                                    | Analysis of Grazing Incidence X-Ray Fluorescence Measurements | 111 |

| 5.7                                                    | Roughness Measurements by AFM                                 | 113 |

| 5.8                                                    | Discussion and Analysis of B implanted N-Type Silicon         | 117 |

|                      |                                          |     |

|----------------------|------------------------------------------|-----|

| <b>Chapter No. 6</b> | <b>Conclusions and Future Directions</b> | 130 |

| 6.1                  | Conclusions                              | 130 |

| 6.2                  | Recommendations for future Work          | 131 |

|                      | References                               | 132 |

## List of Figures

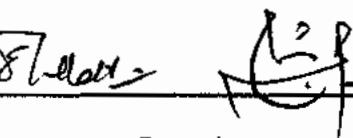

**Figure 2.1** Relative amount of nuclear and electronic stopping power as a function of ion velocity.

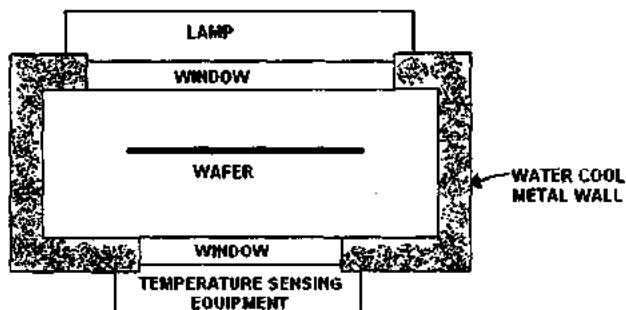

**Figure 2.2** A Generic RTP system (Ying, D. Y. 1997).

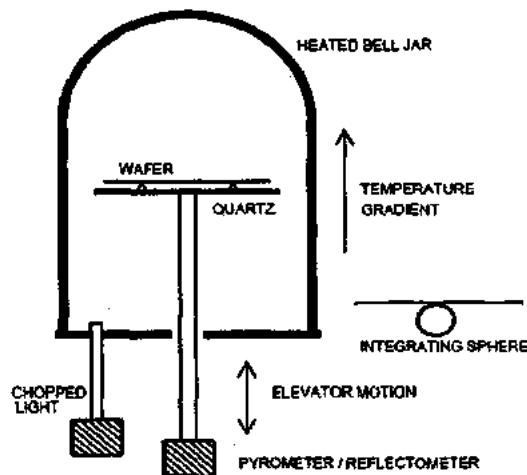

**Figure 2.3** Furnace bell jar method, emissivity corrected pyrometer uses reflectometers relative amount of nuclear and electronic stopping power.

**Figure 2.3** Furnace bell jar method, emissivity corrected pyrometer uses reflectometers with in suite chopped light and ex-suite integrating sphere.

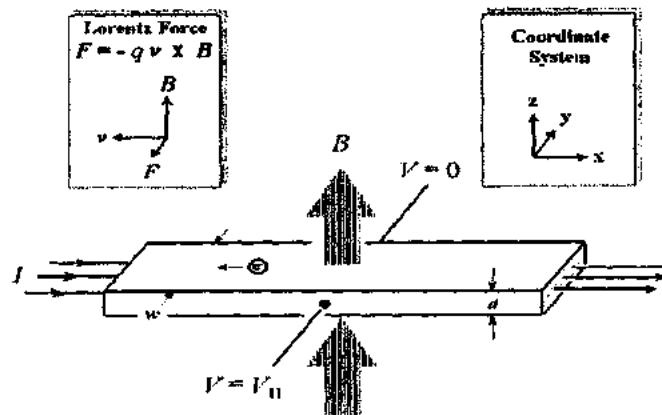

**Figure 2.4** Schematic of the Hall Effect in a long, thin bar of a semiconductor with four ohmic contacts. The direction of the magnetic field  $B$  is along  $-z$ -axis and the sample has a finite thickness  $d$ .

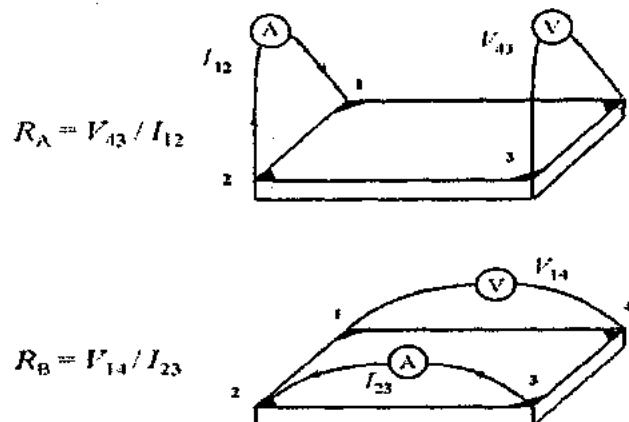

**Figure 2.5** Schematic of the Van der Pauw configuration used in the determination of the two characteristic resistances  $R_A$  and  $R_B$ .

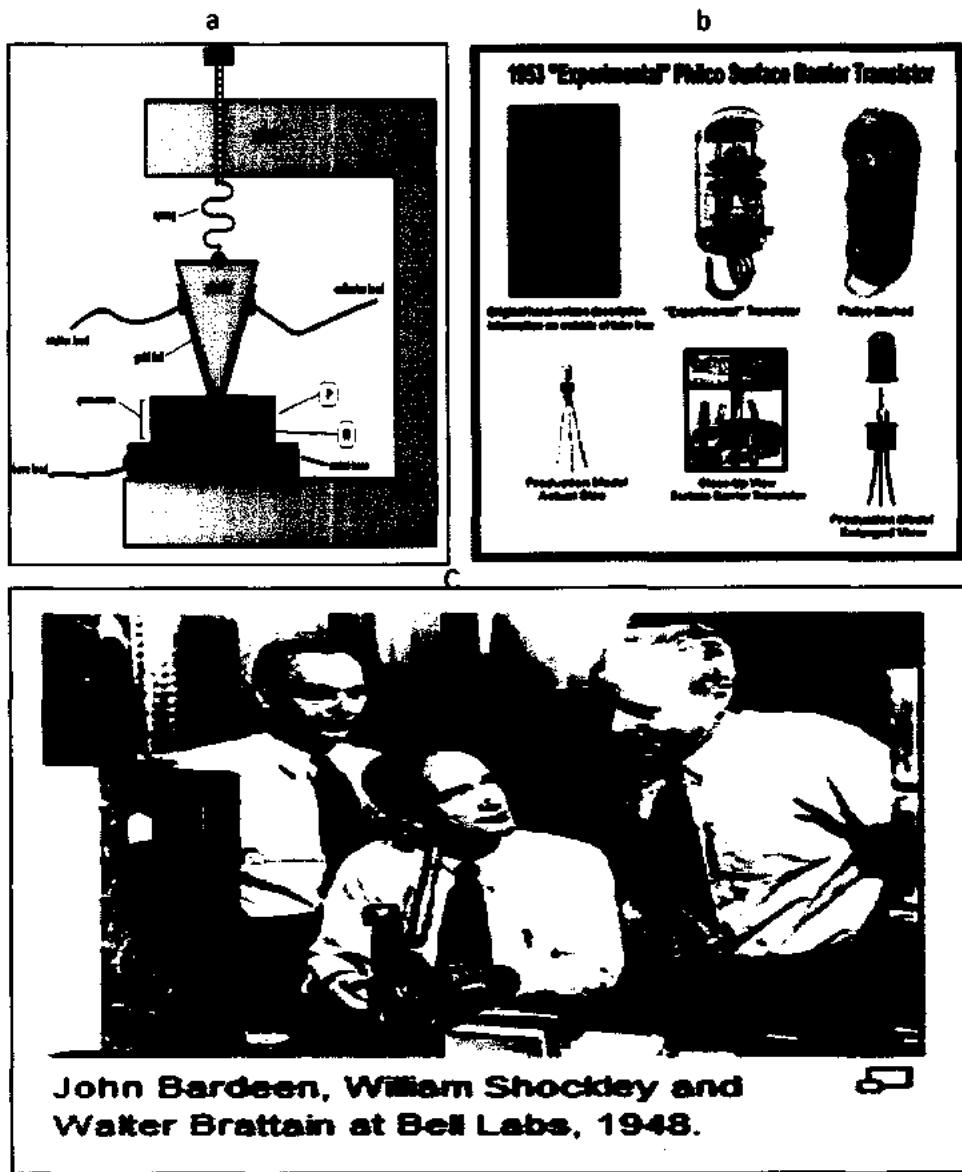

**Figure 3.1** (a) An early model of a transistor, (b) Experimental philco surface barrier transistor. © First point contact transistor introduced in Bell Labs.

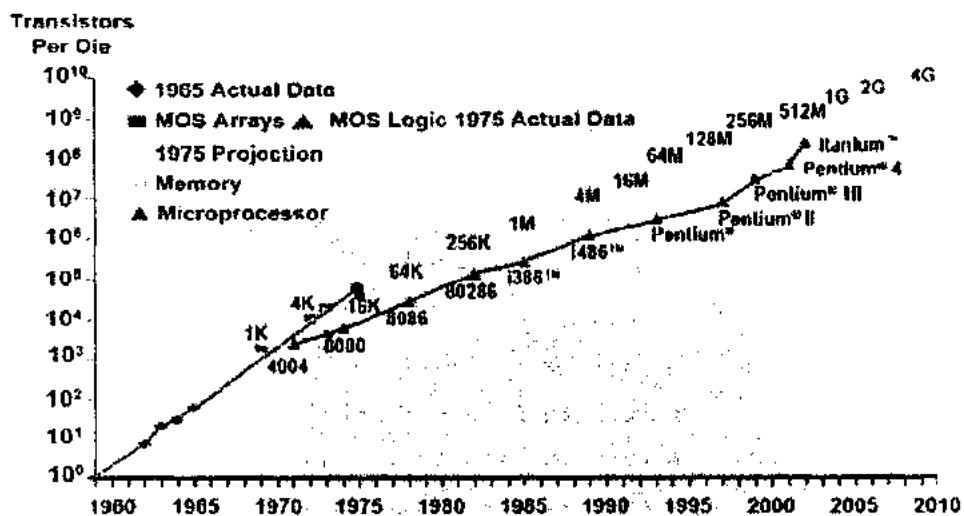

**Figure 3.2** Moore's law of scaling, the number of transistors on a chip has been increasing exponentially.

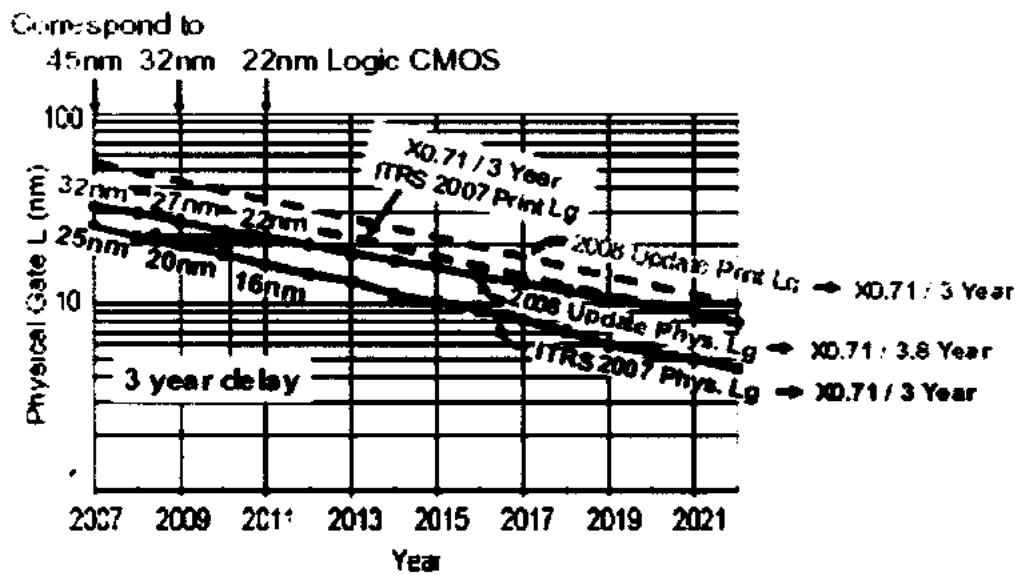

**Figure 3.3** Year by year deduction in gate length according to ITRS roadmap

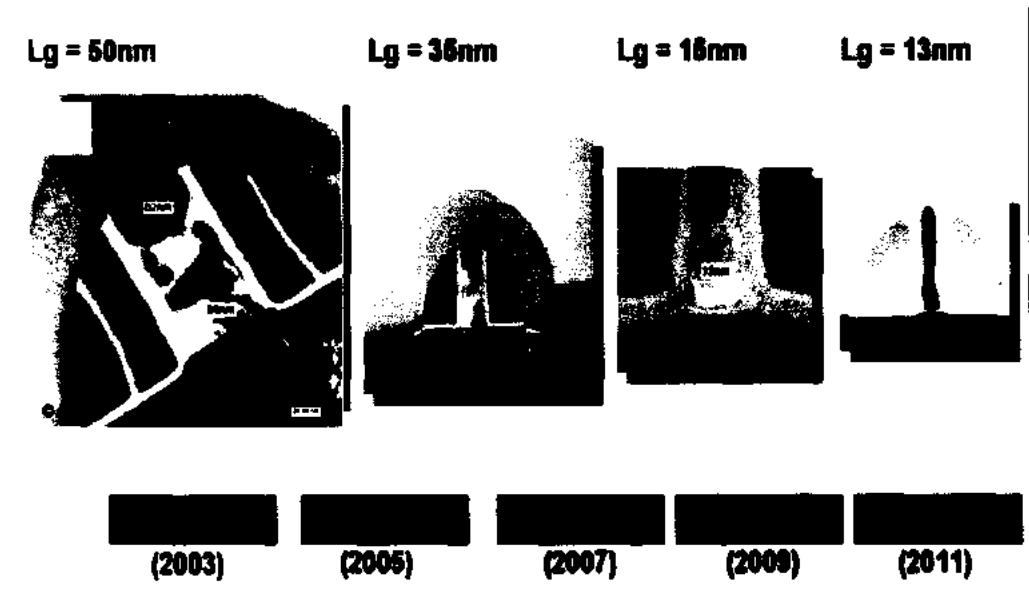

**Figure 3.4** Developmental stages of transistor.

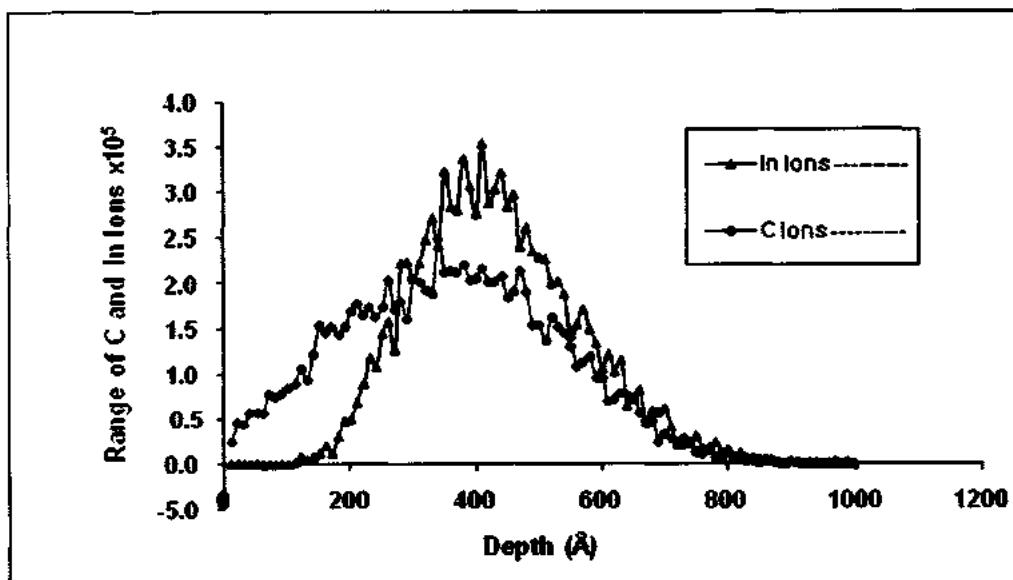

**Figure 4.1** Results of SRIM simulation showing range of In and C in Si.

**Figure 4.2** Results of SRIM simulation showing defects generated in Si due to In and C implantation.

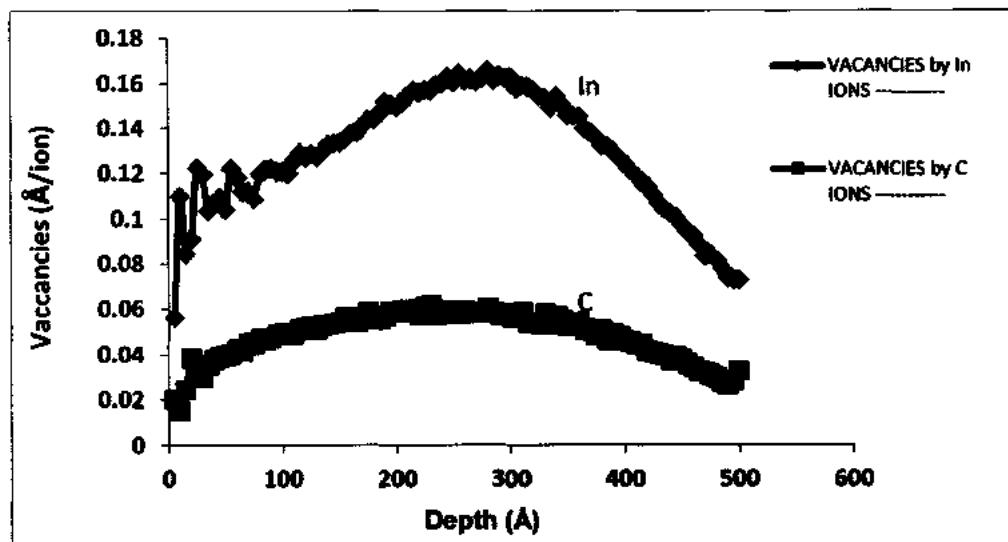

**Figure 4.3** Radiation damage distributions, resulting from a 70 keV In implantation and 10 keV C co-implantation in Si. Along x-axis the depth is in micron and along y-axis defects are in log scale.

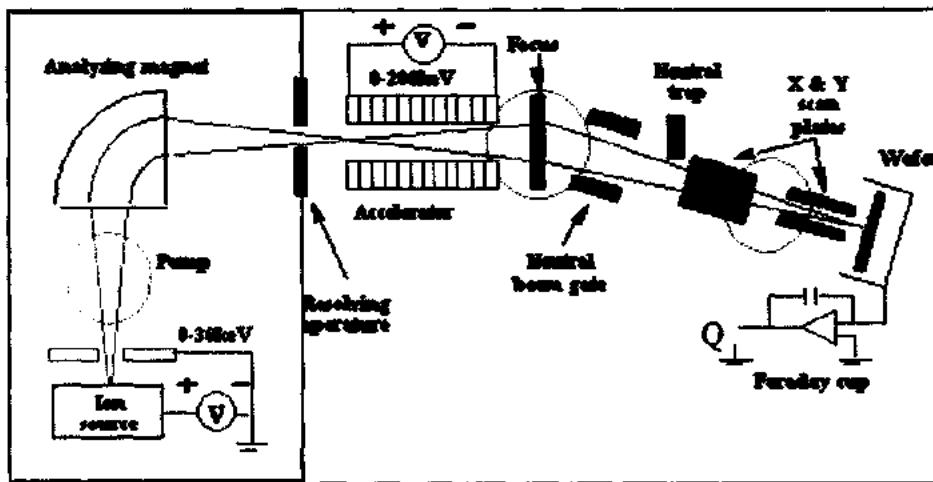

**Figure 4.4** A typical ion implanter.

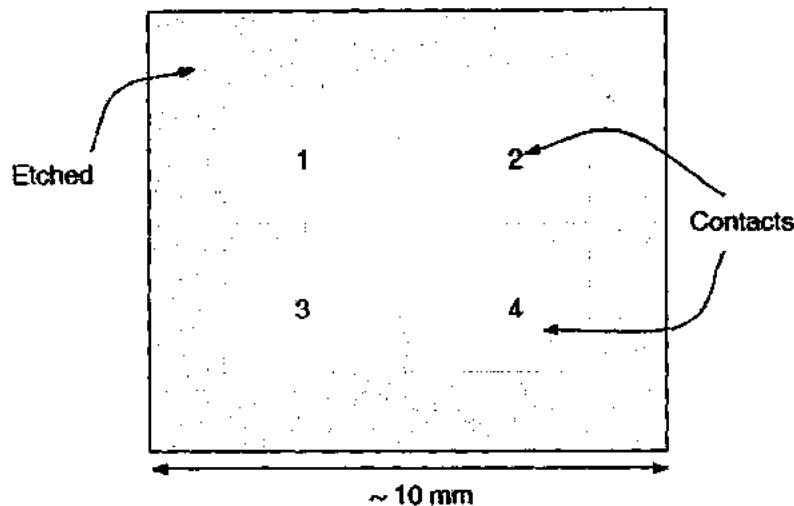

**Figure 4.5** Cloverleaf pattern used to fulfill the criteria of Van der Pauw measurements.

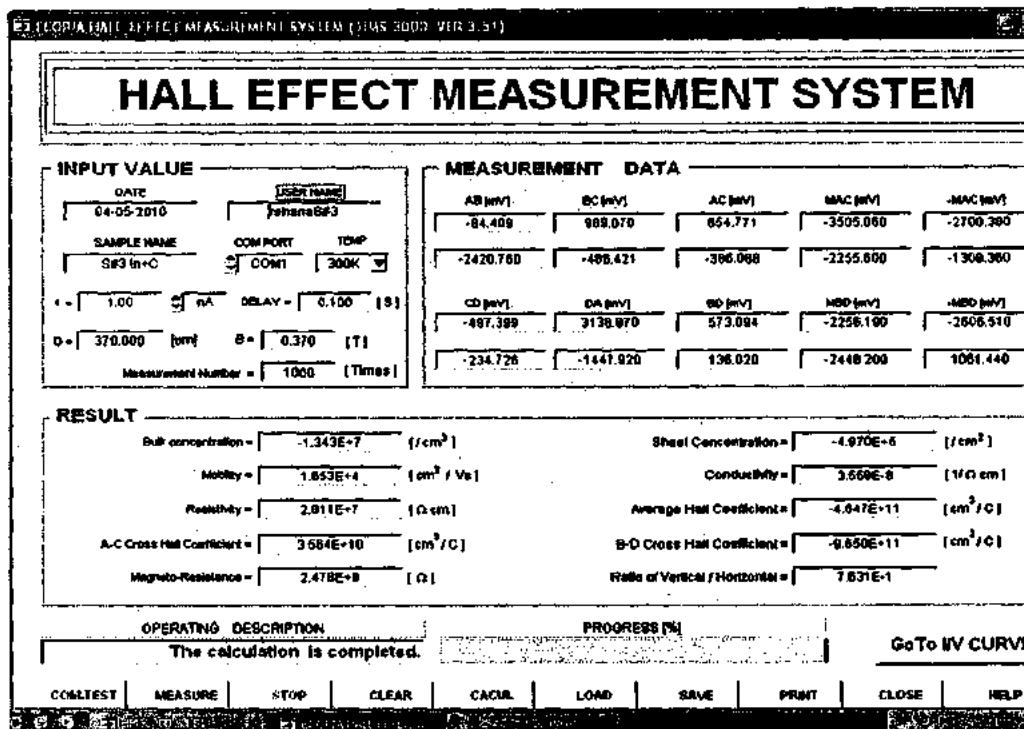

**Figure 4.6** Data sheet obtained from Hall Measurement System HMS3000 for as-implanted In+C co-implanted Si substrate.

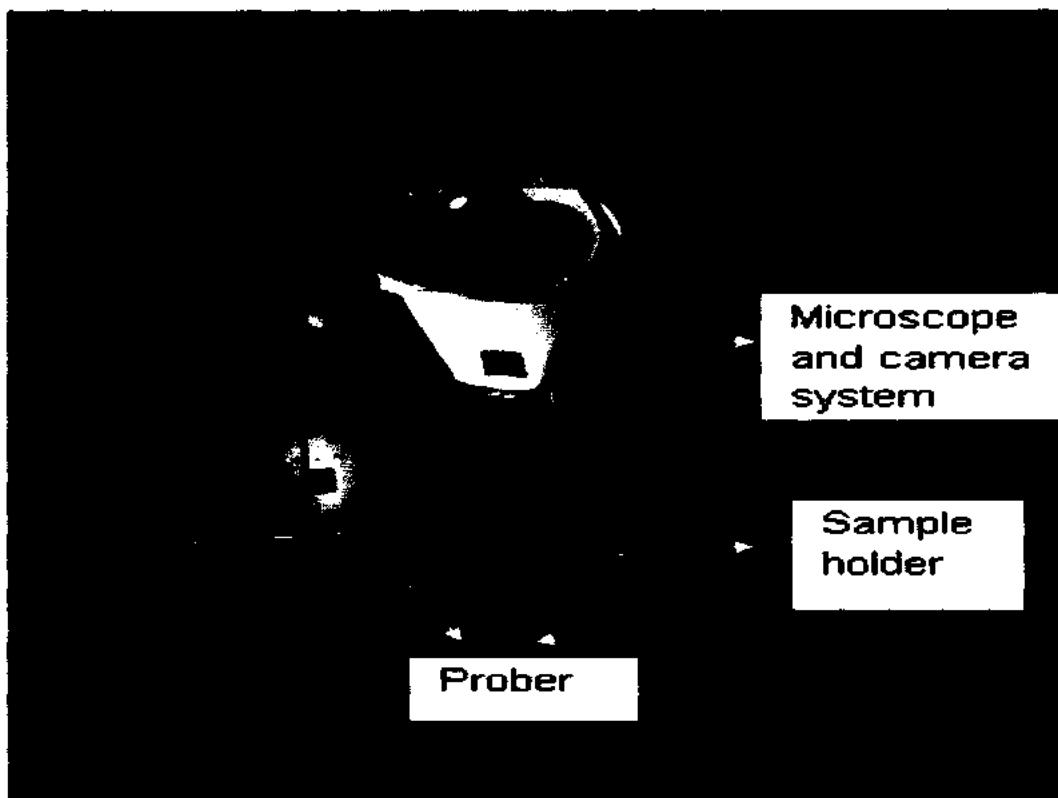

**Figure 4.7** Probe station used for I-V & C-V measurements

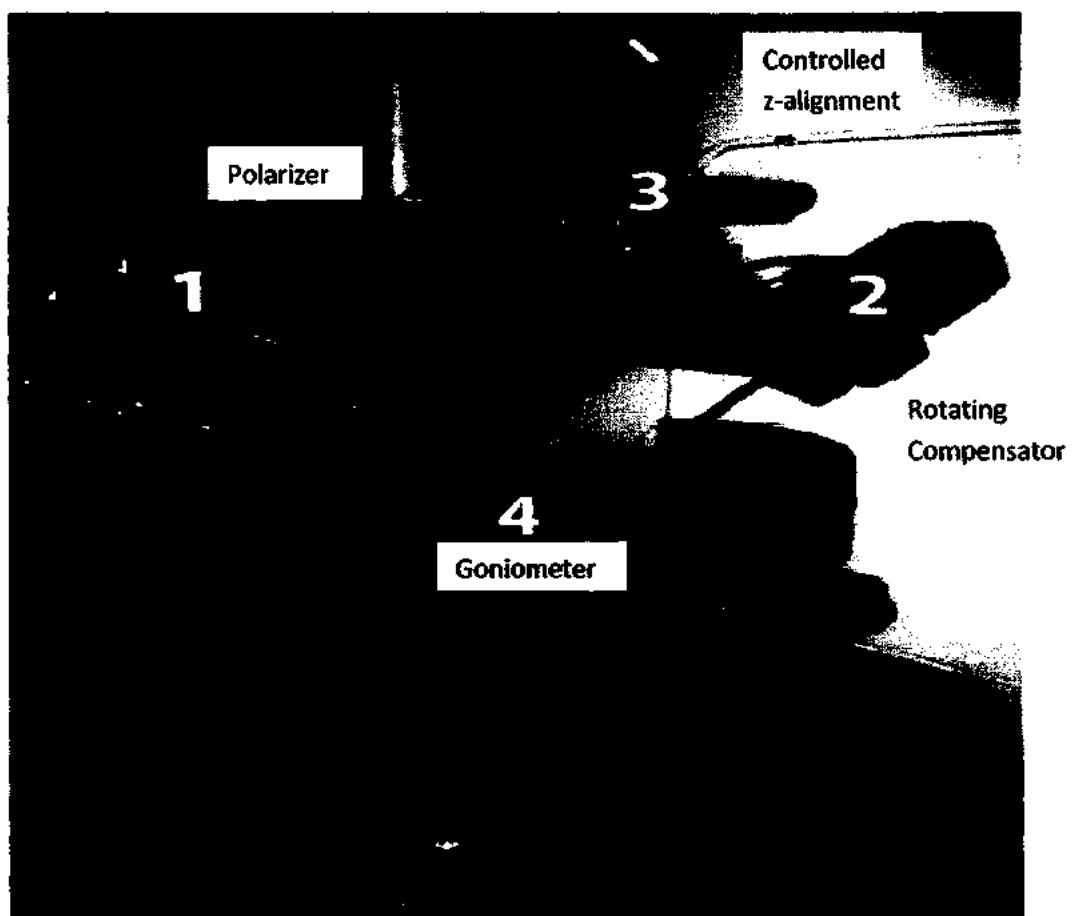

**Figure 4.8** M-2000Vi multichannel ellipsometers mounted on an automated stage.

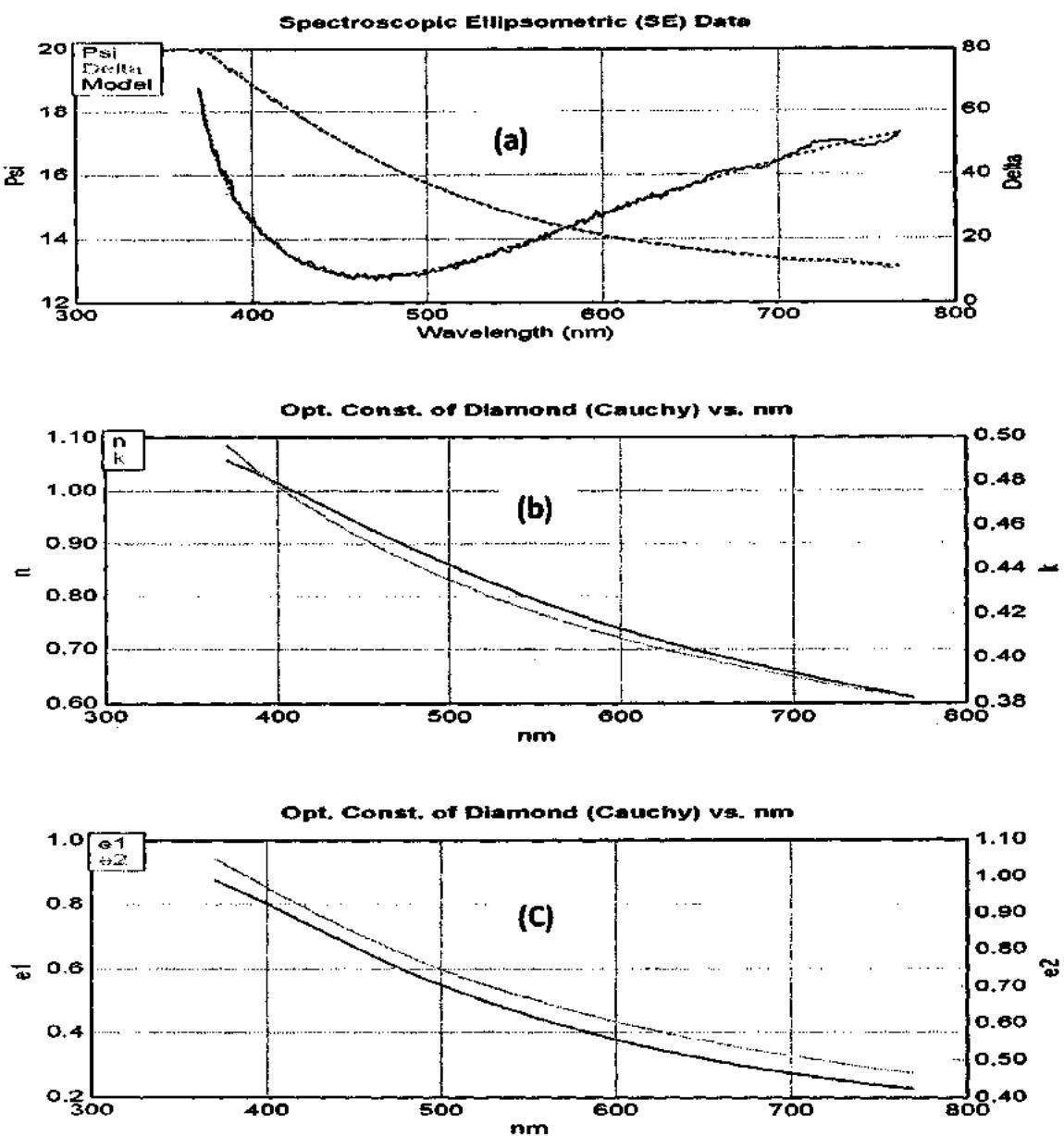

**Figure 4.9** Ellipsometric results showing (a) Psi and delta versus wavelength (b). Real and imaginary parts of refractive index versus wavelength (c) Real and Imaginary part of Dielectric function for as implanted In+C co-implanted Si substrate.

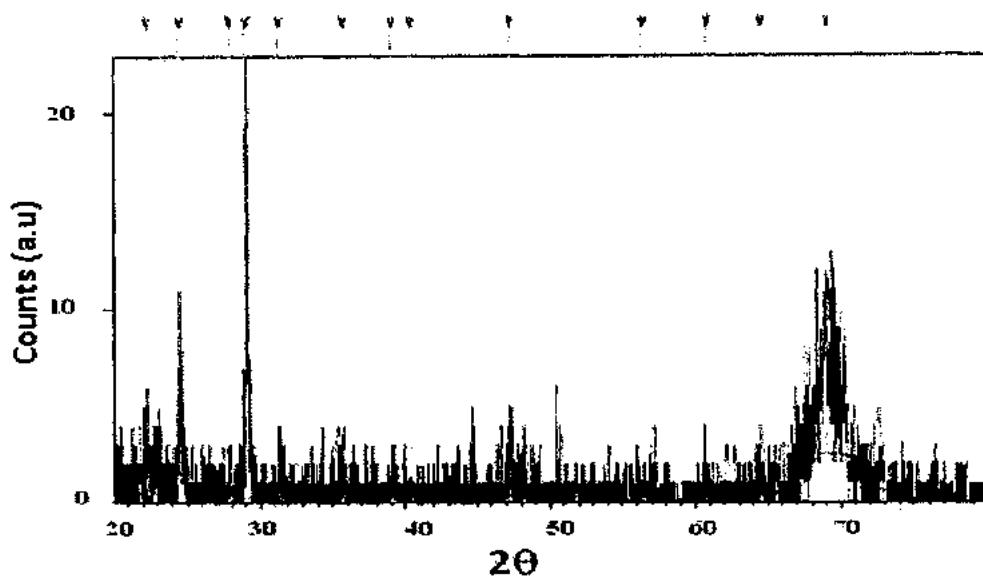

**Figure 4.10** XRD spectrum obtained for In+C co-implanted p-type Si substrate.

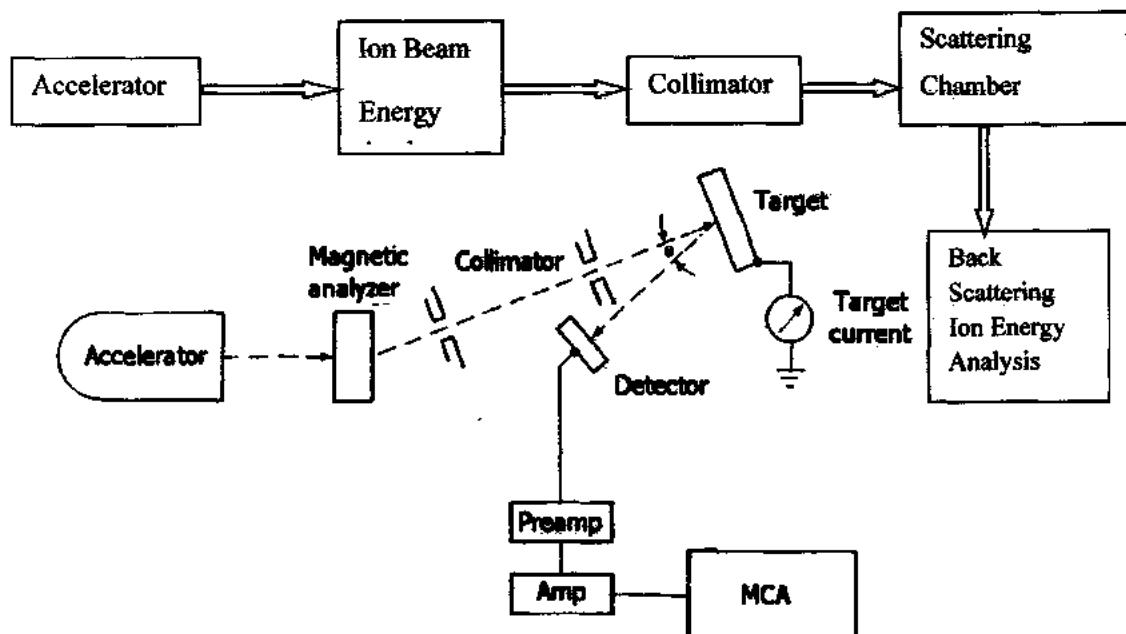

**Figure 4.11(a)** Illustration of accelerator in NCP. (b) Schematic of accelerator used for Rutherford Back Scattering Spectrometry.

**Figure 4.12** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing a comparison of as implanted and annealed results of RBS yield. The Si, C and In peaks are identified.

**Figure 4.13** GIXRF spectrum recorded for In+C co-implanted n-type silicon substrate and B implanted n-type Si substrate.

**Figure 4.14** Endstation GIXRF.

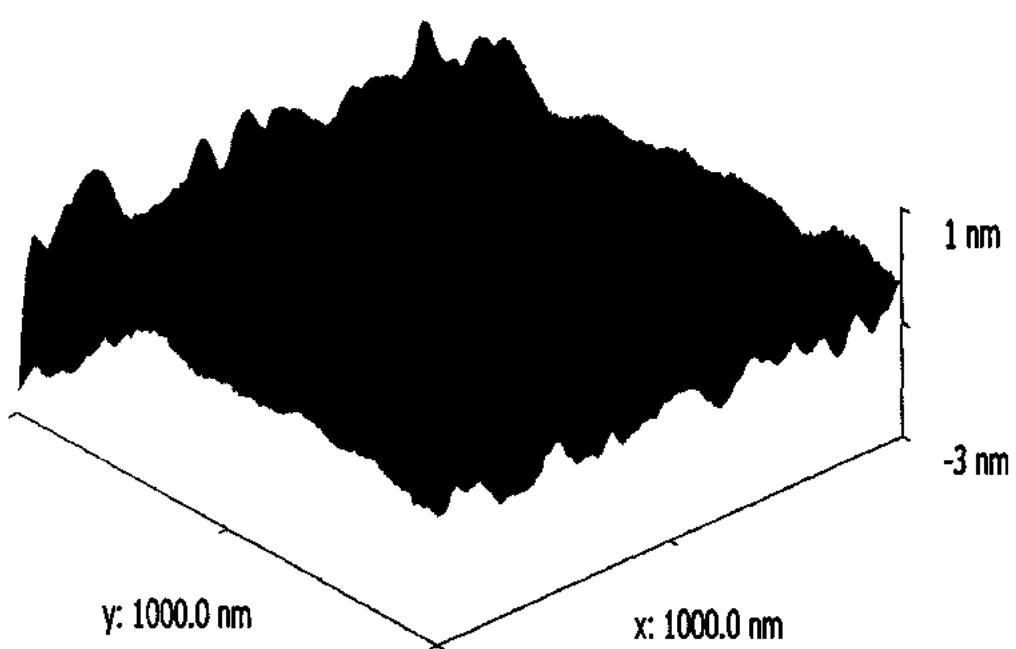

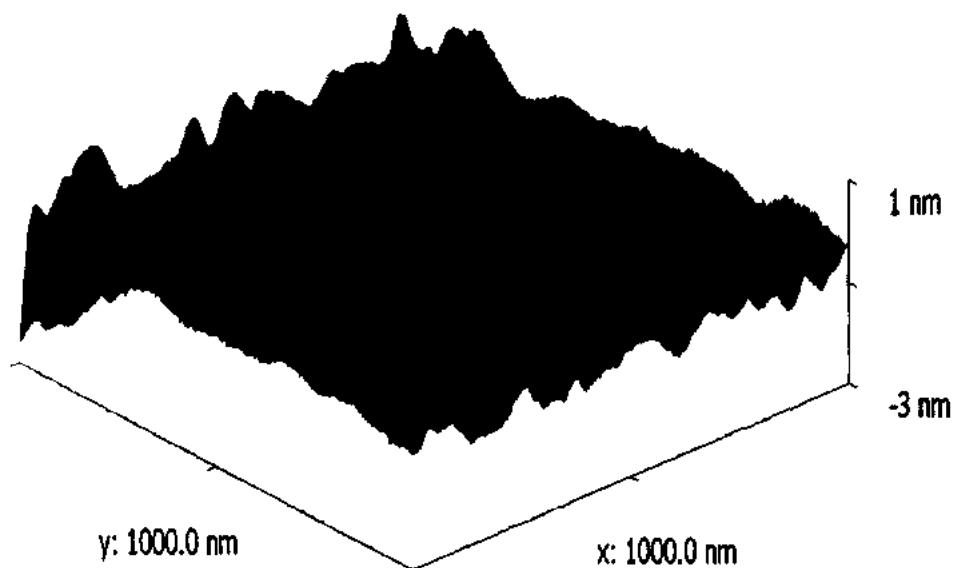

**Figure 4.15** Atomic Force Microscopic topographical view of the In+C co-implanted Si Substrate before annealing showing extent of roughness and uniformity of the deposited indium and carbon co-implants. The presence of impurity concentration of boron and phosphorous at different depths is also visible as background structural information. This three dimensional view shows negligible degradation of the morphology of the surface after the devised and processed implant strategy.

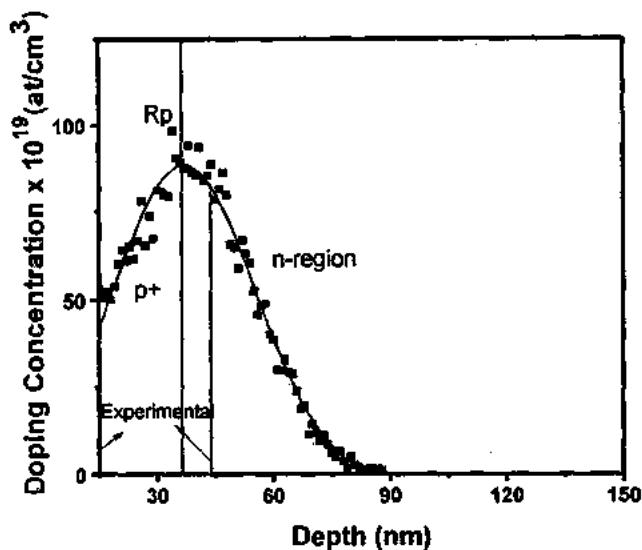

**Figure 5.1:** Simulated positions of the combined implanted indium and carbon atoms showing atomic concentration profile at different depths in silicon substrate. The n-type Si substrate is implanted with indium and carbon ions at 70 keV and 10 keV, respectively with respective doses of  $5.7 \times 10^{14}$  ions  $\text{cm}^{-2}$  and  $3.4 \times 10^{15}$  ions  $\text{cm}^{-2}$ . The simulations were carried out by SRIM-2011 code. The vertical line shows the projected range. The experimental results show that the position of the junction moves from 17 to 43 nm due to variation in annealing temperature.

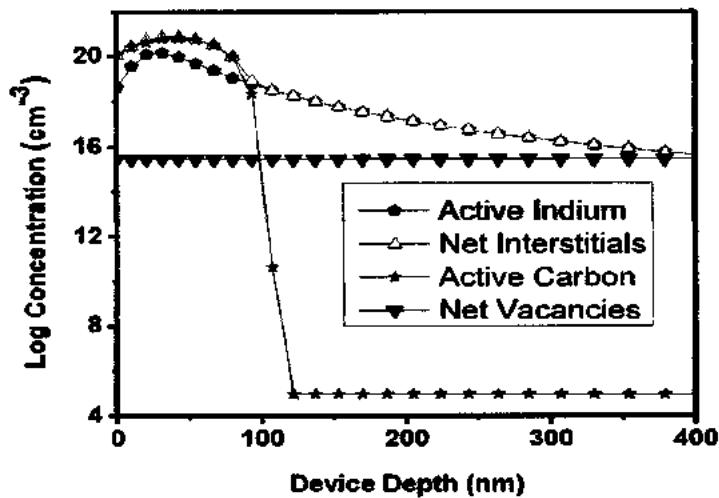

**Figure 5.2:** Graph showing number of interstitial atom, active indium, active carbon and net vacancies in silicon after post implant annealing at 600°C as representative temperature. These curves are simulated in device structure modeled by TCAD SILVACO.

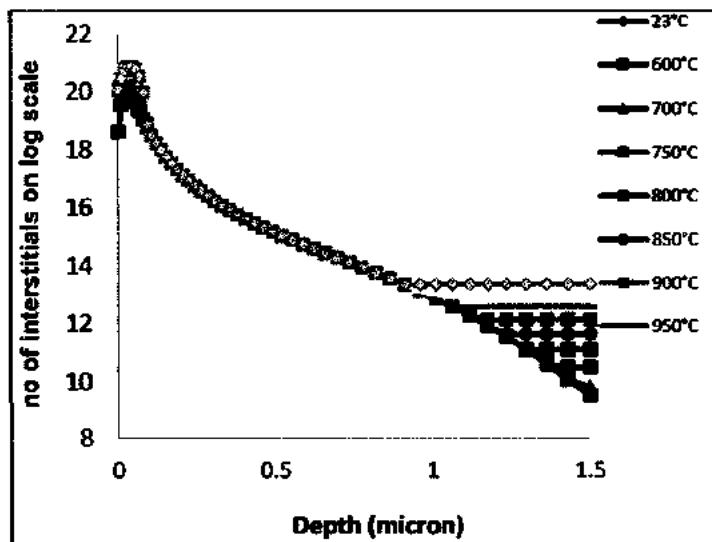

**Figure 5.3:** Behavior of interstitials of In and C in Si substrate between annealing regime room temperature to 1100°C.

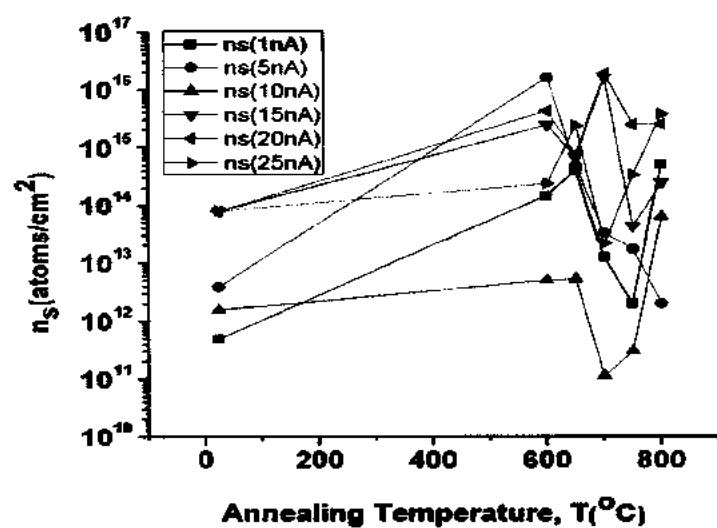

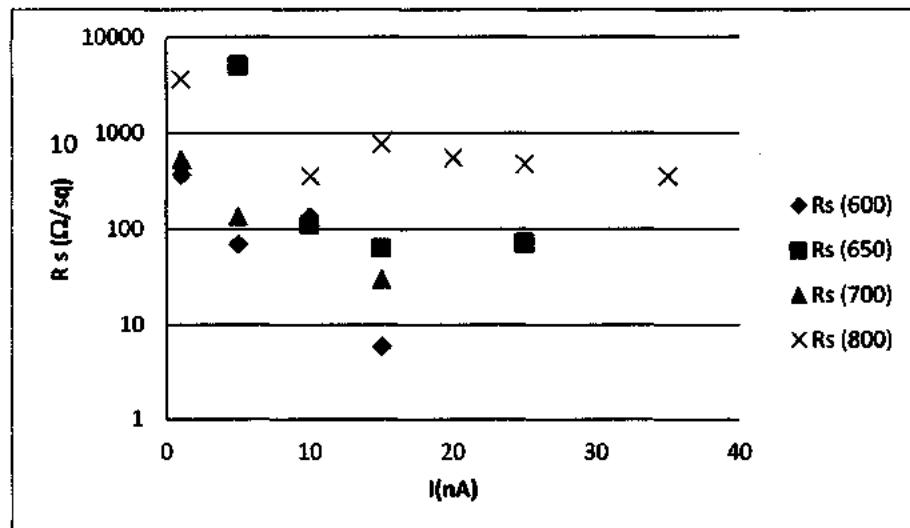

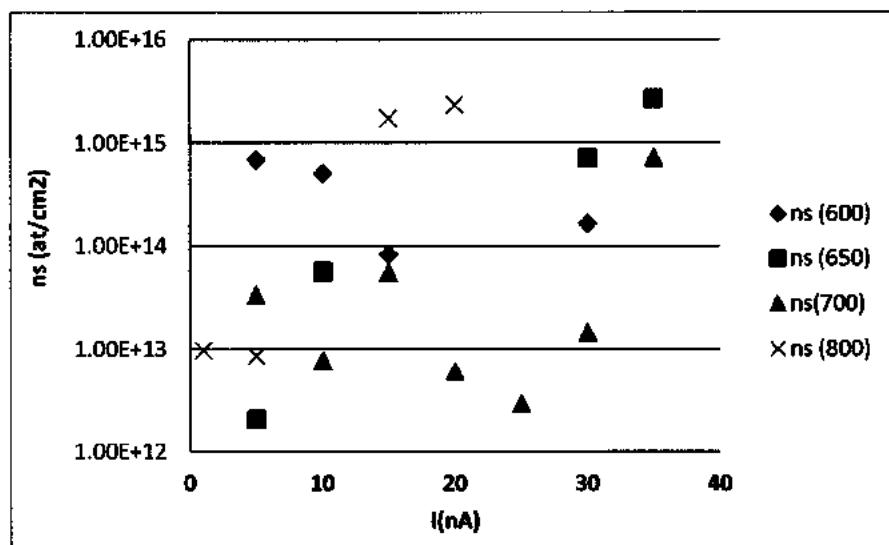

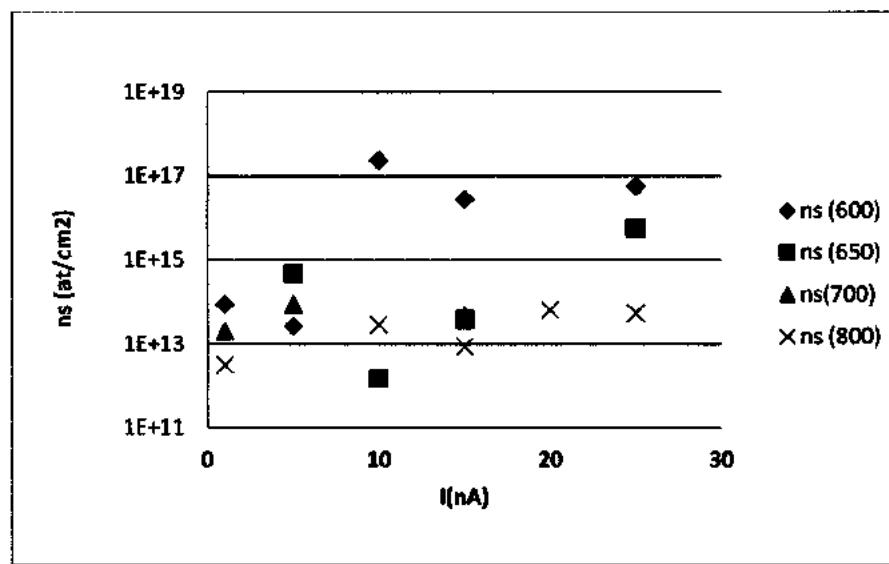

**Figure 5.4:** Plots showing variation of retained sheet carrier concentration with respect to annealing temperatures at different current ranges for In+C co-implanted n-type silicon substrate again the data plotted here is obtained from Hall measurement System HMS3000.

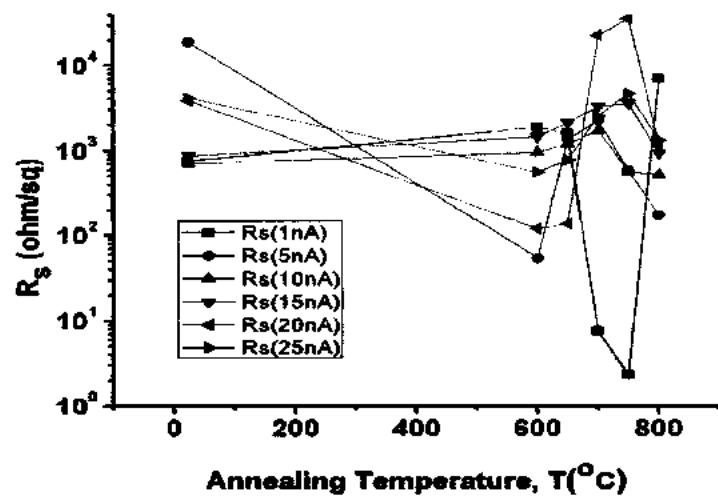

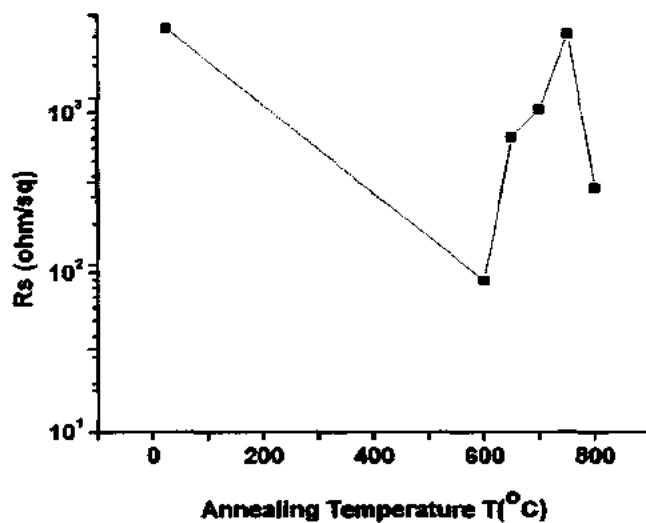

**Figure 5.5:** Variation of sheet resistance obtained from Hall measurement System, for In+C co-implanted n-type silicon substrate against annealing temperatures from 600°C -800°C. The values plotted here are averaged against the data obtained after repeated measurements for each sample to assure the reliability and tolerance.

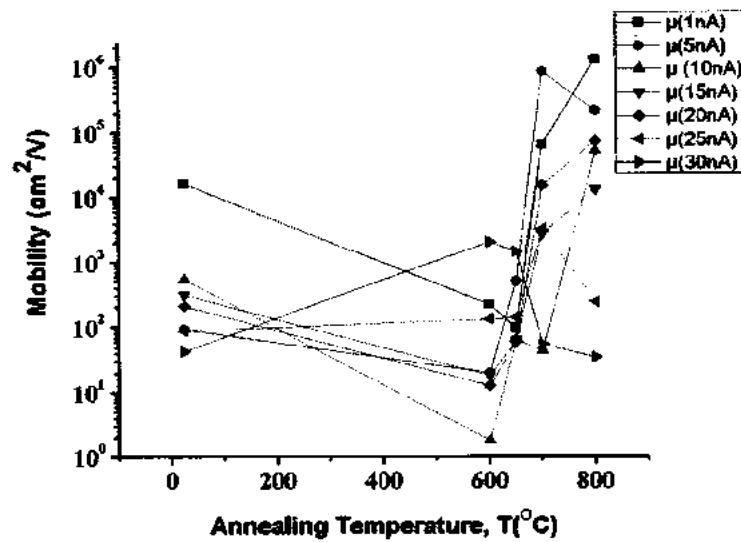

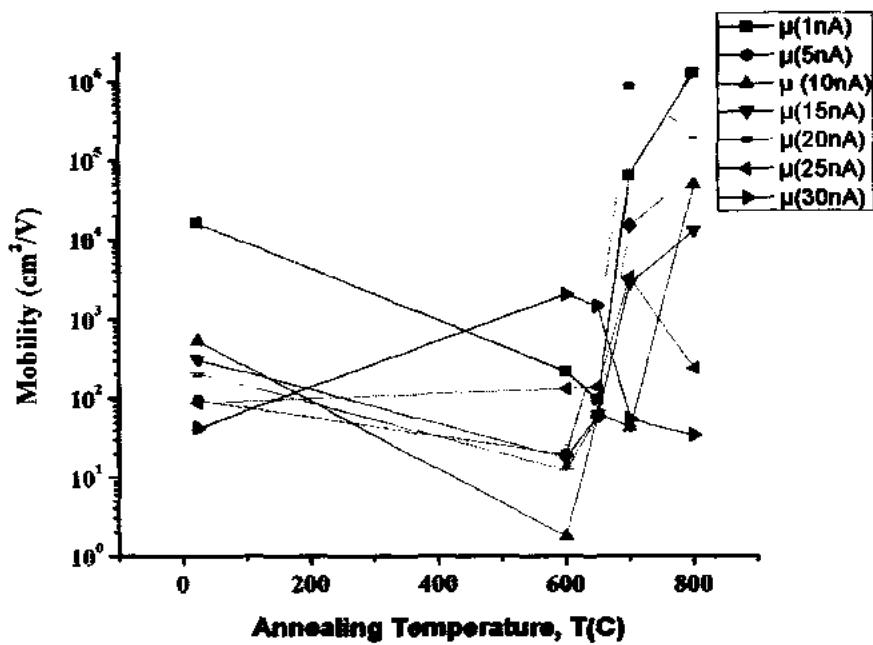

**Figure 5.6:** Plots showing variation of carrier mobility with respect to different annealing temperatures at current range from 1 nA-30 nA for In+C co-implanted n-type silicon substrate. Again, the data plotted here is obtained from Hall measurement System HMS 3000.

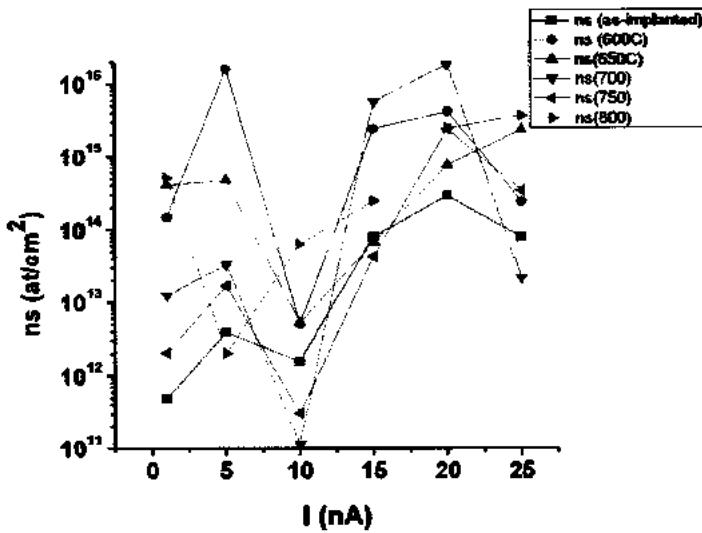

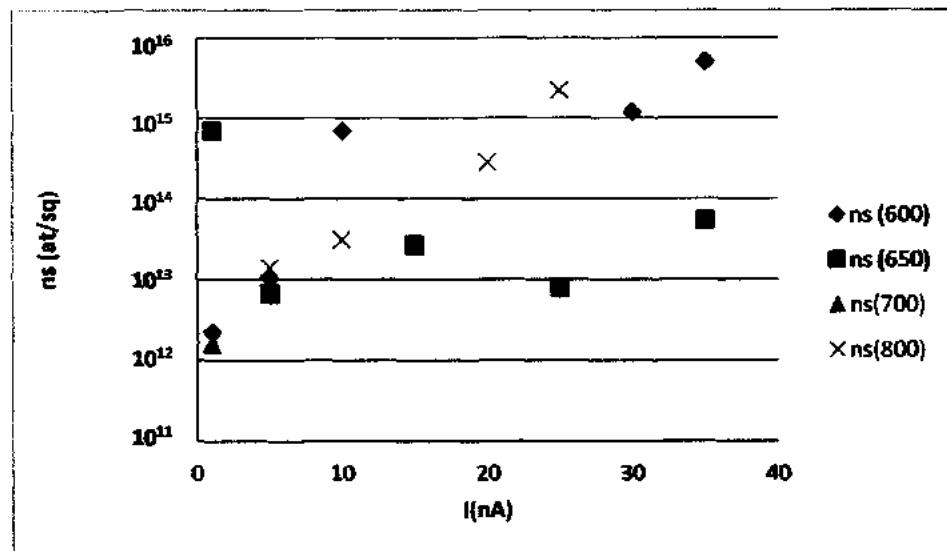

**Figure 5.7:** Plots showing variation of retained sheet carrier concentration with respect to current ranges from 1 nA-25 nA for In+C co-implanted n-type silicon substrate at different annealing temperatures. Again, the data plotted here is obtained from Hall measurement System HMS 3000.

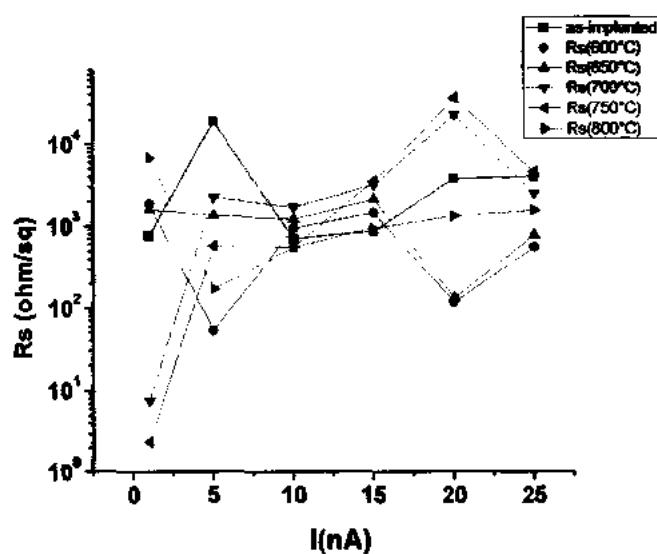

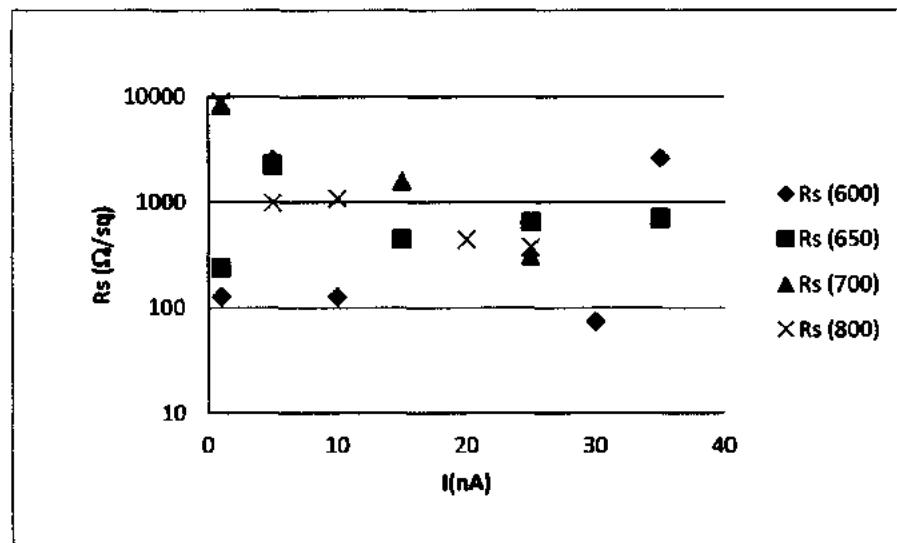

**Figure 5.8:** Variation of sheet resistance, obtained from Hall measurement System, for In+C co-implanted n-type silicon substrate against current ranges 1 nA-30 nA at different annealing temperatures. The values plotted here are averaged against the data obtained after repeated measurements for each sample to assure the reliability and tolerance.

**Figure 5.9:** Variation of sheet resistance obtained from Keithley 4200 IV/CV system, for In+C co-implanted n-type silicon substrate against post annealing temperatures from 600°C-800°C. The values plotted here are averaged against the data obtained after repeated measurements for each sample to assure the reliability and tolerance.

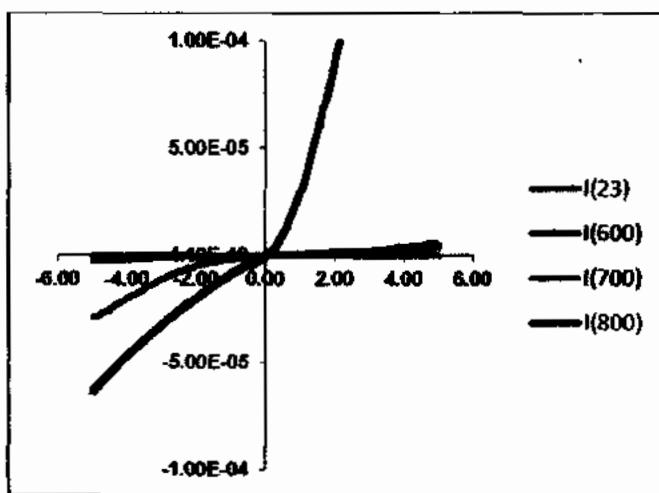

**Figure 5.10:** Variation of current I (mA) with respect to voltage V(volts), obtained from Keithley 4200 IV/CV system, for In+C co-implanted n-type silicon substrate for annealing temperatures from 600°C-800°C. The values plotted here are averaged against the data obtained after repeated measurements for each sample to assure the reliability and tolerance.

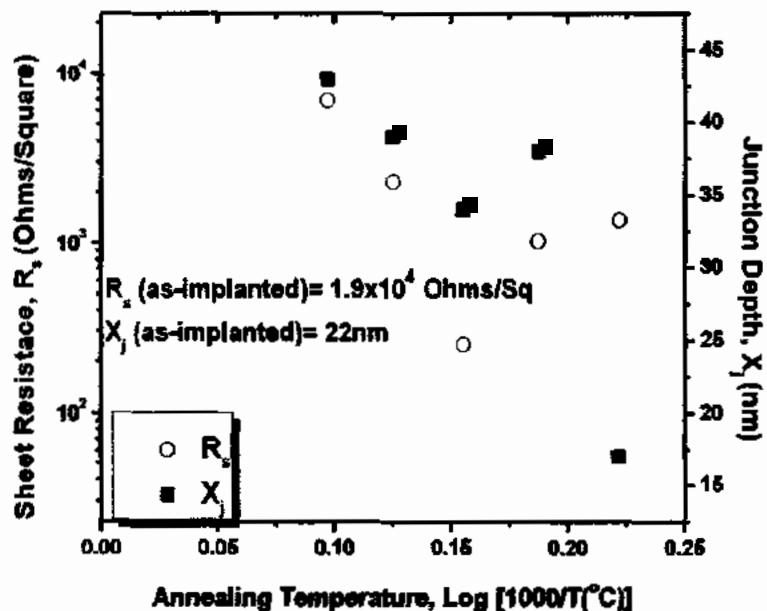

**Figure 5.11:** Variation of sheet resistance and junction depth (Xj), obtained from Hall measurement System, Keithley 4200 and CV measurement system for In+C co-

implanted n-type silicon substrate against different annealing temperatures. The values plotted here are averaged against the data obtained after repeated measurements by three different techniques for each sample to assure the reliability and tolerance.

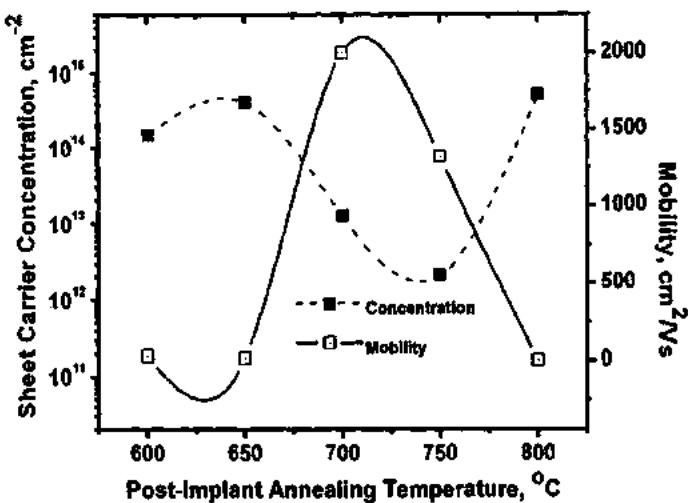

**Figure 5.12:** Two plots showing variation of retained sheet carrier concentration and carrier mobility with respect to different annealing temperatures. Again, the data plotted here are average values obtained by three different techniques.

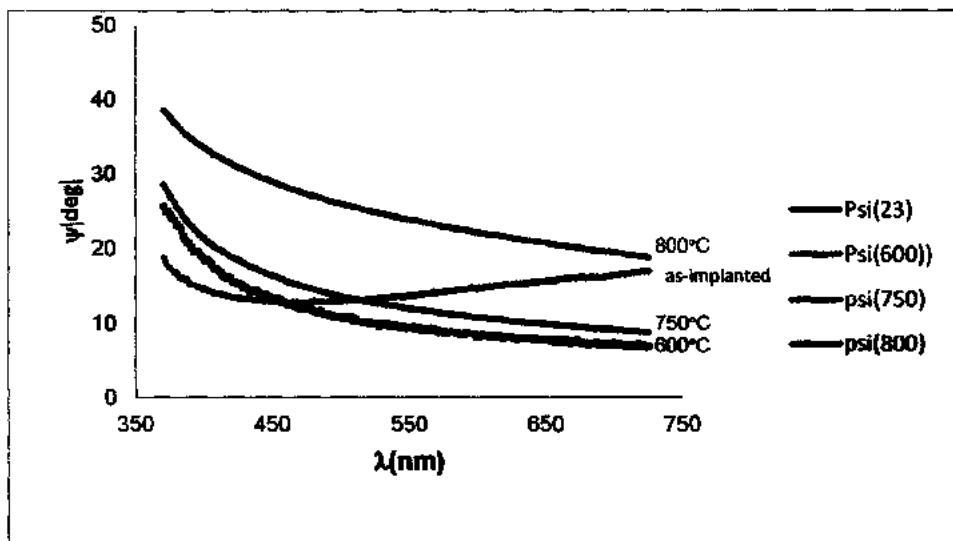

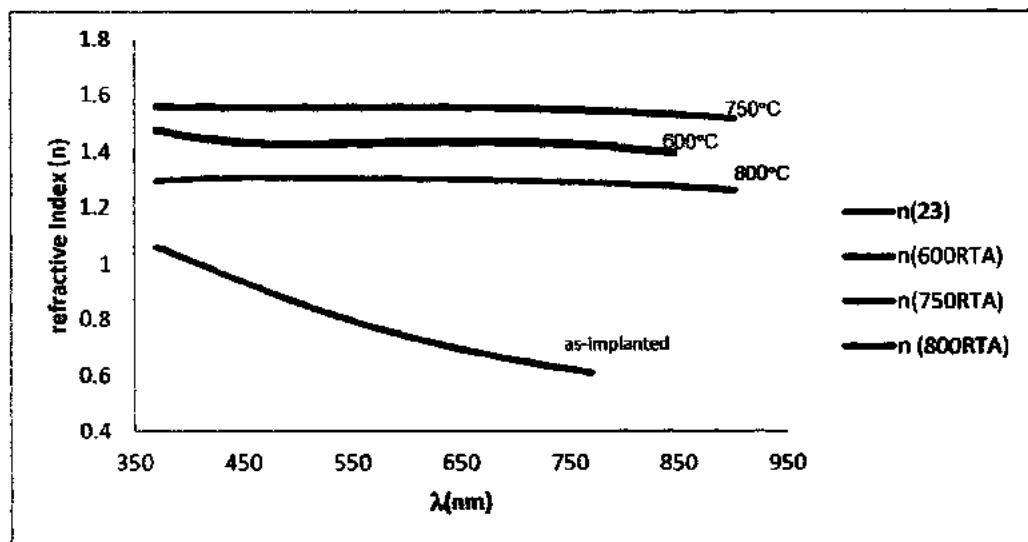

**Figure 5.13:** Ellipsometric Psi ( $\psi$ ) spectra at 70° angle of incidence for as-implanted and RTA annealed In+C co-implanted Si substrate.

**Figure 5.14:** Ellipsometric delta ( $\Delta$ ) spectra for 70° angle of incidence for RTA annealed In+C co-implanted Si substrate.

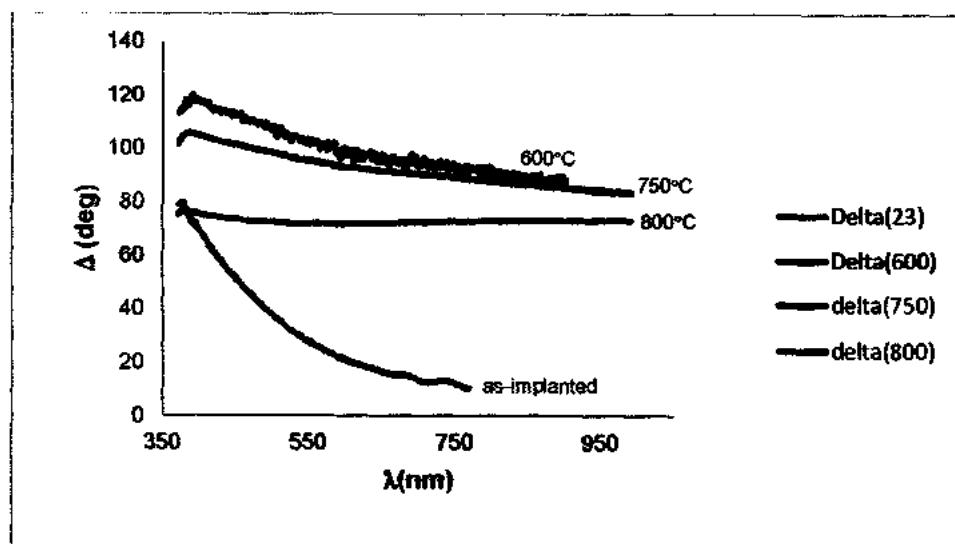

**Figure 5.15:** Effect of temperature ellipsometric Psi ( $\psi$ ) spectra and ellipsometric delta ( $\Delta$ ) spectra at 70° angle of incidence for RTA annealed In+C co-implanted Si substrate.

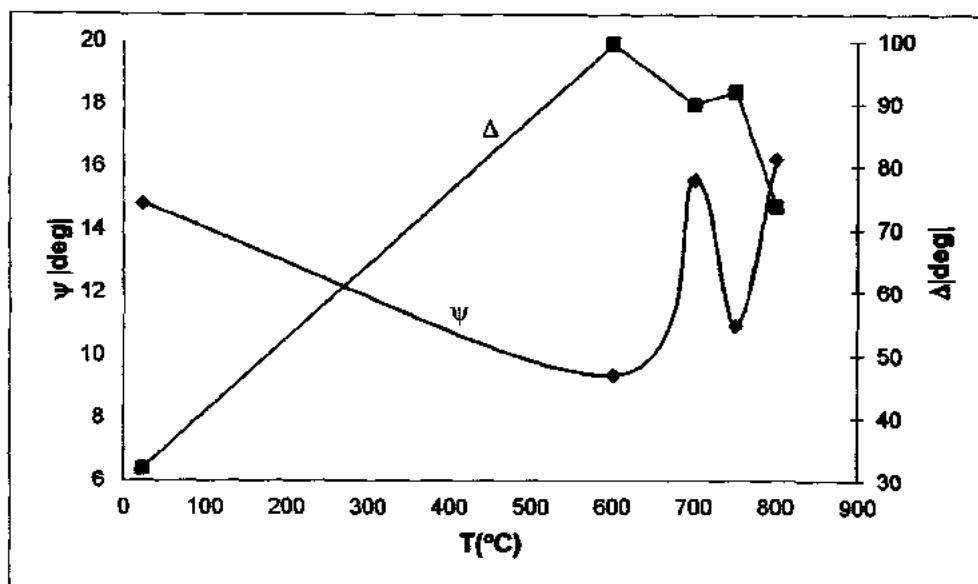

**Figure 5.16:** Refractive index versus wavelength, this figure shows the variation of refractive index with respect to wavelength at different temperature. The data shows that uniformity or periodicity exist between these temperature ranges.

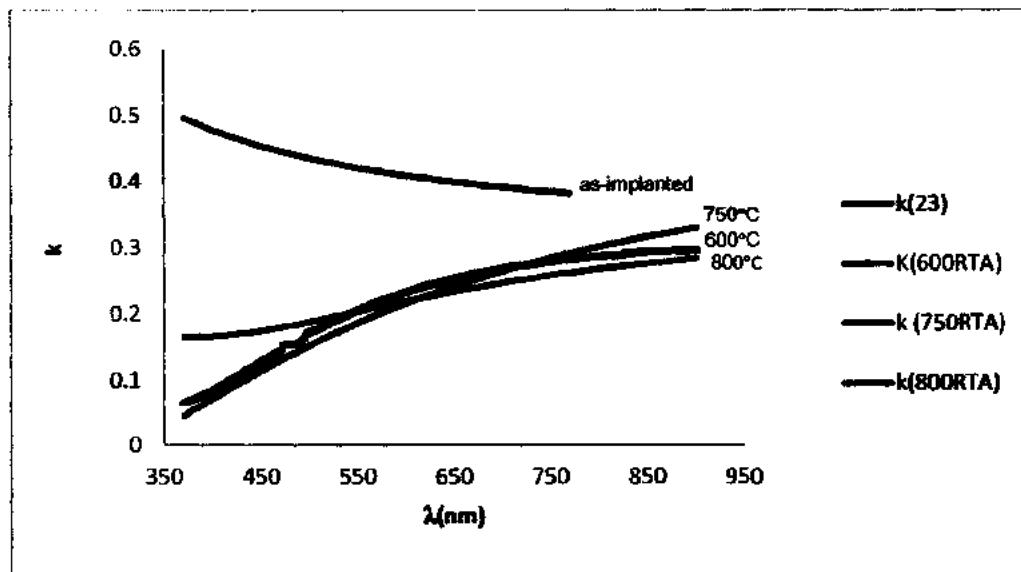

**Figure 5.17:** This figure shows the variation of imaginary part of refractive index with respect to wavelength for both as implanted and annealed In+C co-implanted Si-substrate.

**Figure 5.18:** This figure shows the variation of real part of refractive index with respect to wavelength for both as implanted and annealed In+C co-implanted Si-substrate.

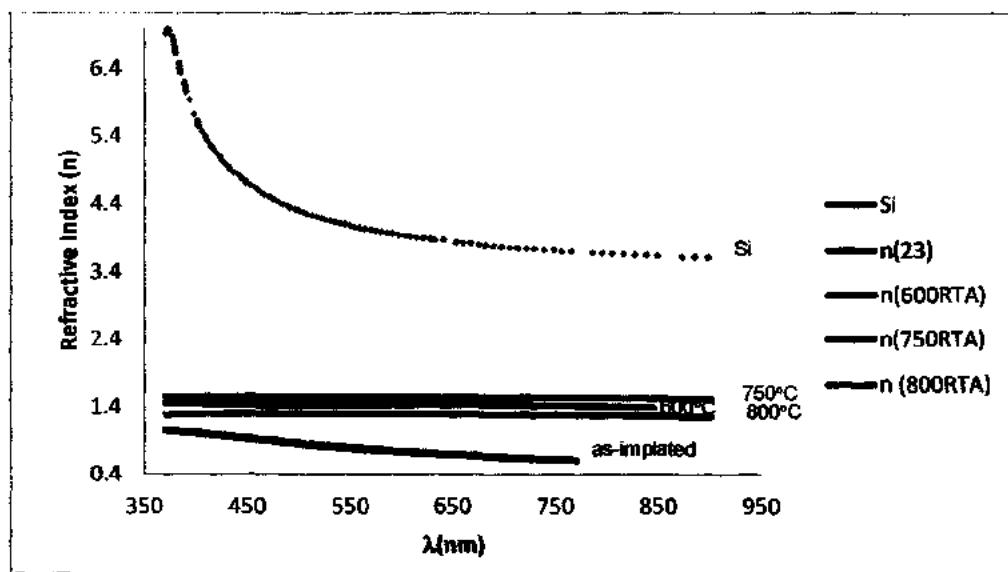

**Figure 5.19:** Ellipsometric spectra at 70° degree angle of incidence for both as-implanted and RTA annealed In+C co-implanted Si substrate. Average values of  $n$  and  $k$  are taken at different annealing temperatures.

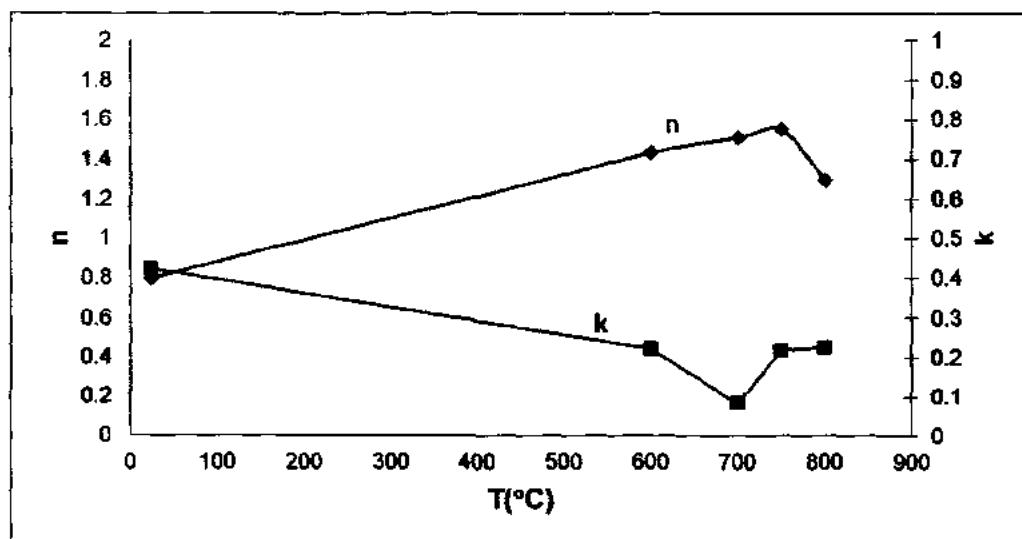

**Figure 5.20:** Real part of the dielectric function for In+C co-implanted n-type silicon substrate at different annealing temperatures.

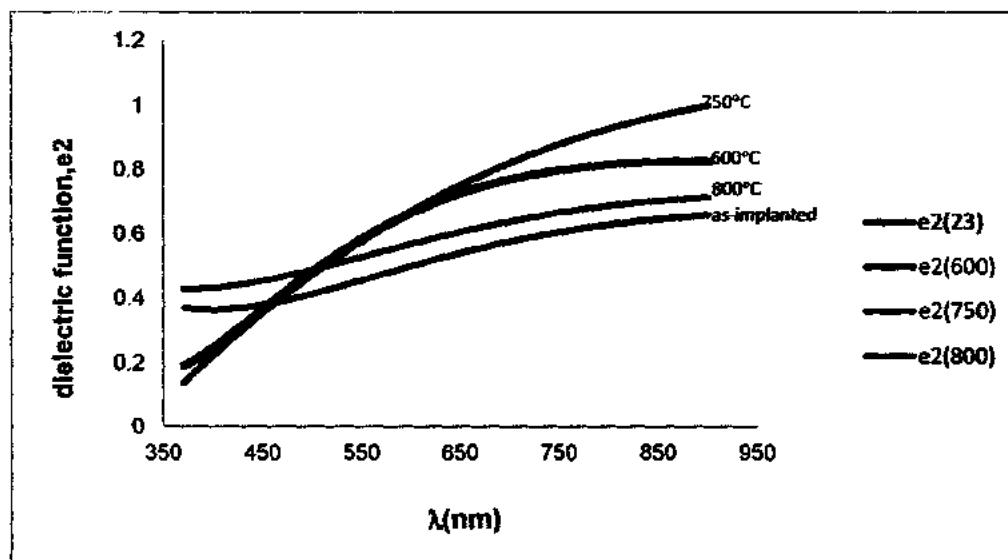

**Figure 5.21:** Imaginary part of the dielectric function for In+C co-implanted n-type silicon substrate at different annealing temperatures.

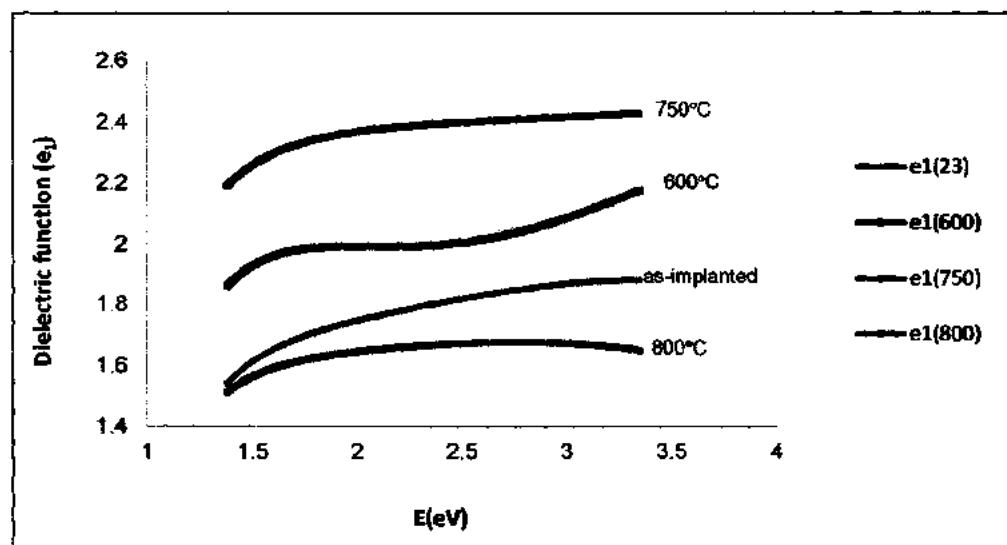

**Figure 5.22:** Effect of annealing temperature on real part ( $\epsilon_1$ ) and imaginary parts ( $\epsilon_2$ ) of In+C co-implanted n-type silicon substrate.

**Figure 5.23:** The figure shows the variation of absorption coefficient with respect to wavelength for silicon, as-implanted In+C co-implanted n-type silicon and annealed In+C co-implanted silicon substrate.

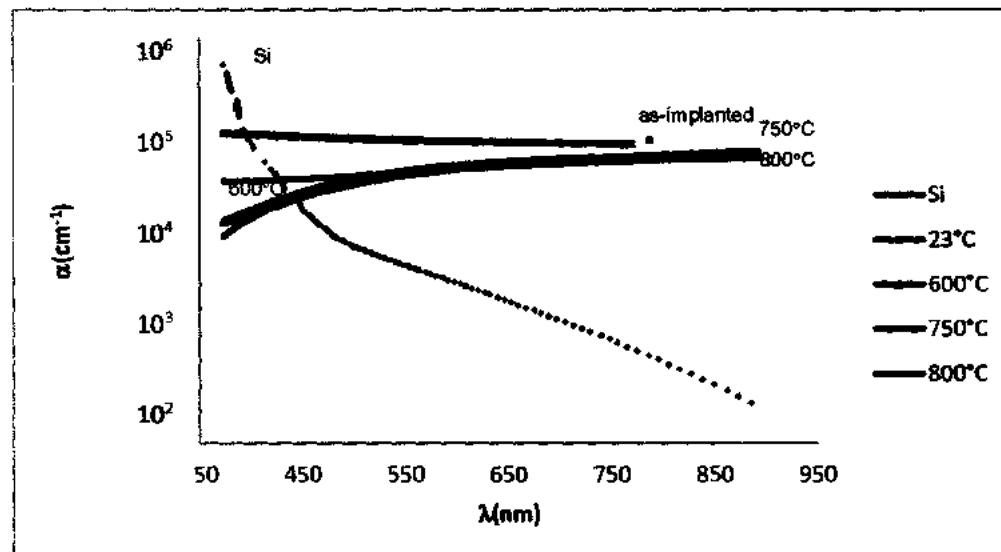

**Figure 5.24:** Effect of annealing temperature on absorption coefficient.

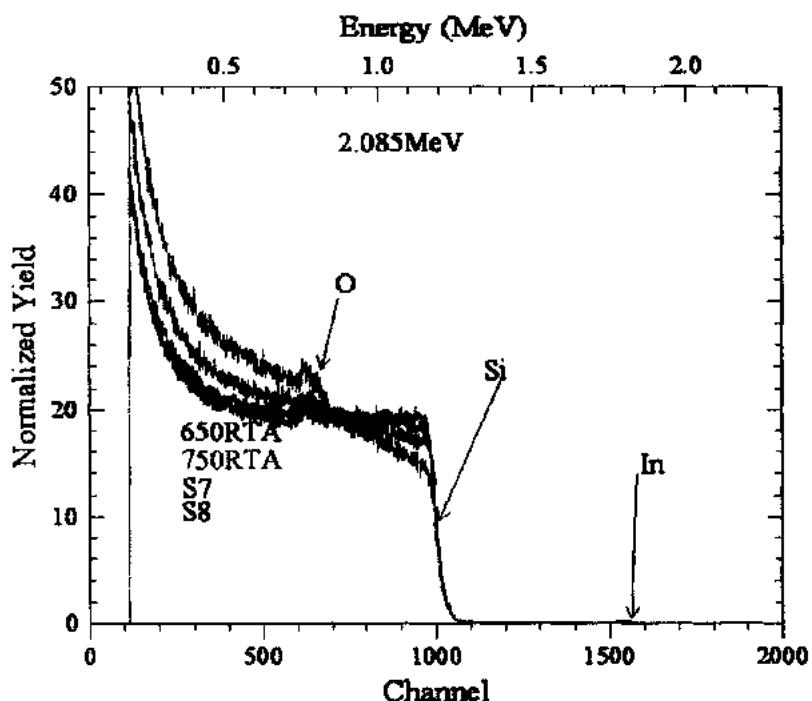

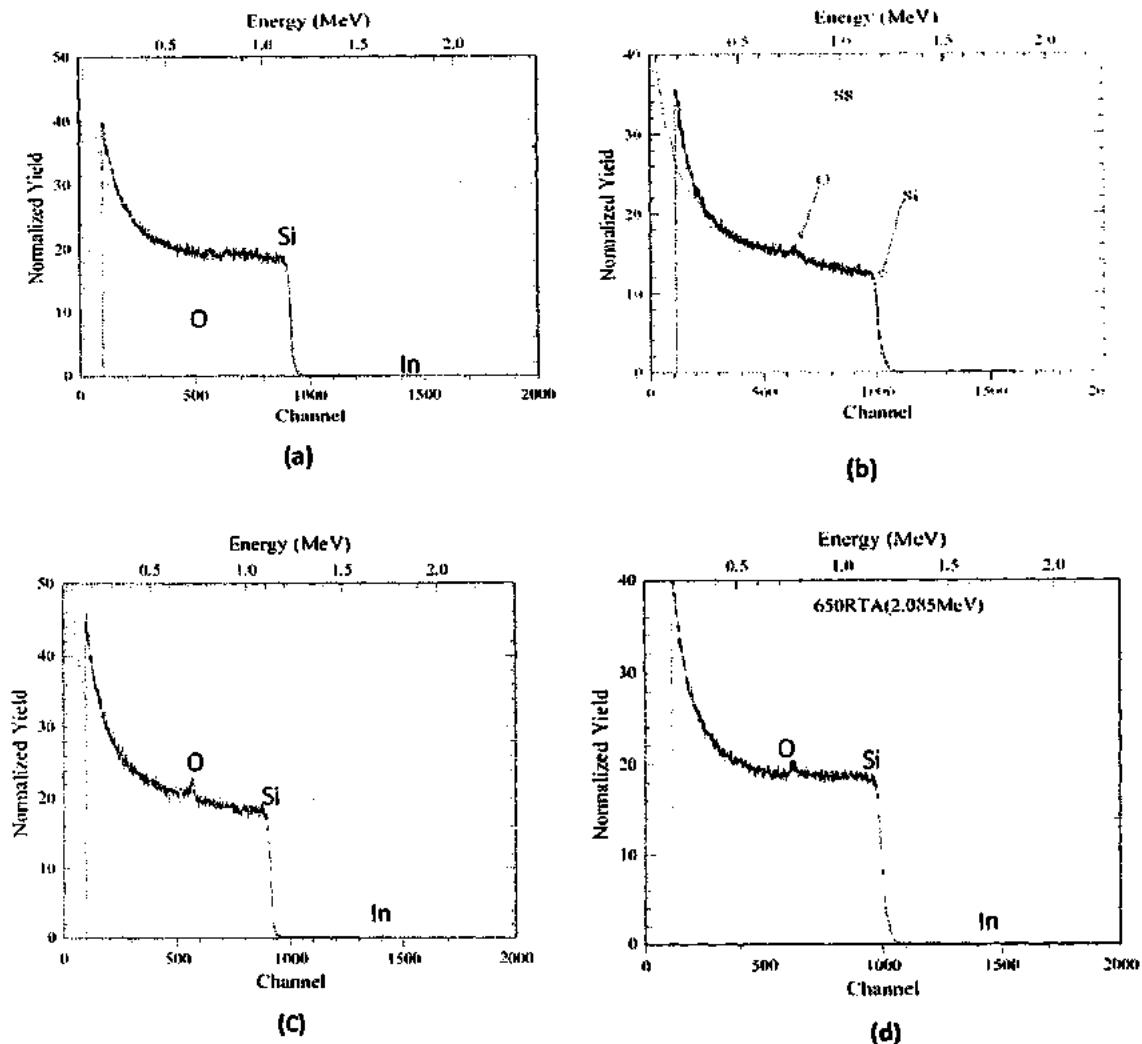

**Figure 5.25:** Rutherford Back Scattering Spectrum recorded for  $\text{He}^{++}$  ions of energy 2.085 MeV incident on the In+C co-implanted n-type Si substrate showing results of RBS yields of as implant. The C, Si and In peaks are also identified.

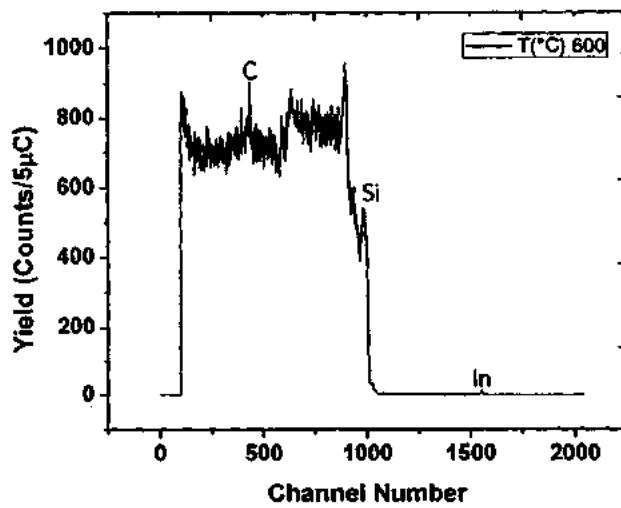

**Figure 5.26:** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing results of RBS yields of samples annealed at 600°C. The C, Si and In peaks are also identified

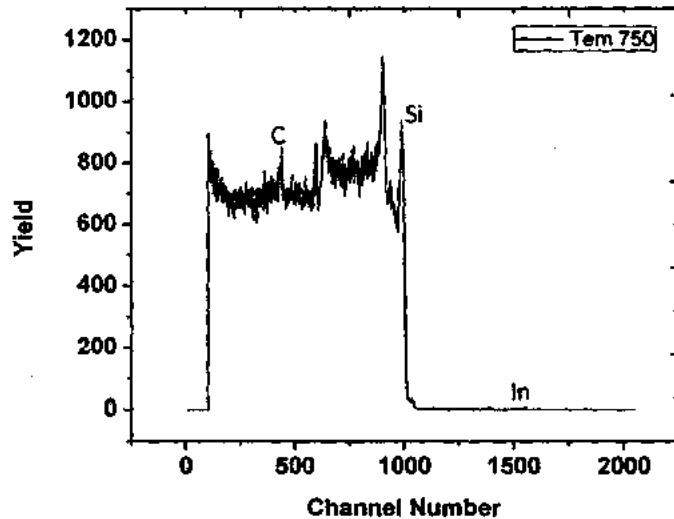

**Figure 5.27:** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing results of RBS yields of samples annealed at 750°C. The C, Si and In peaks are also identified.

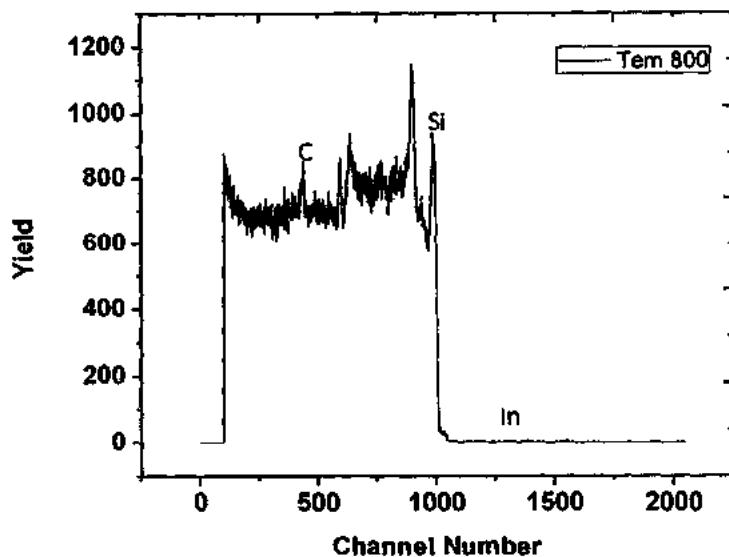

**Figure 5.28:** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing results of RBS yields of samples annealed at 800°C. The C, Si and In peaks are also identified.

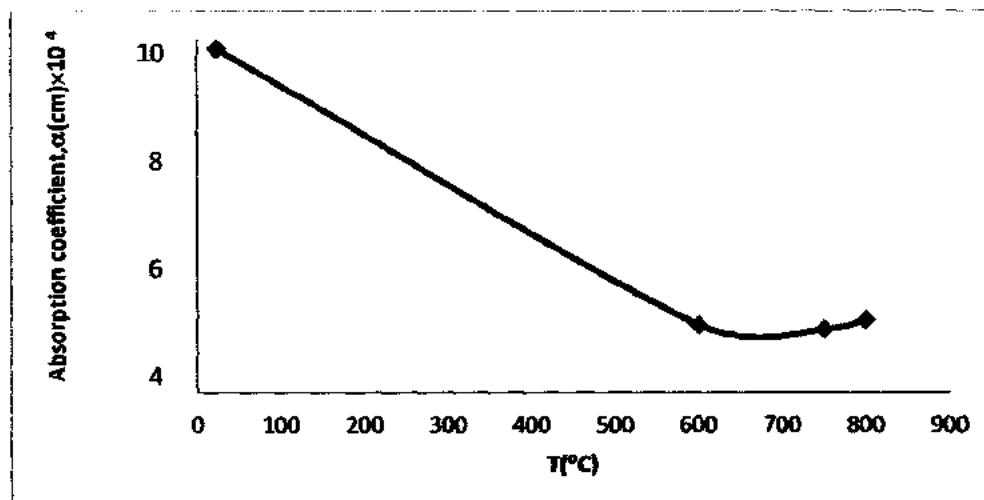

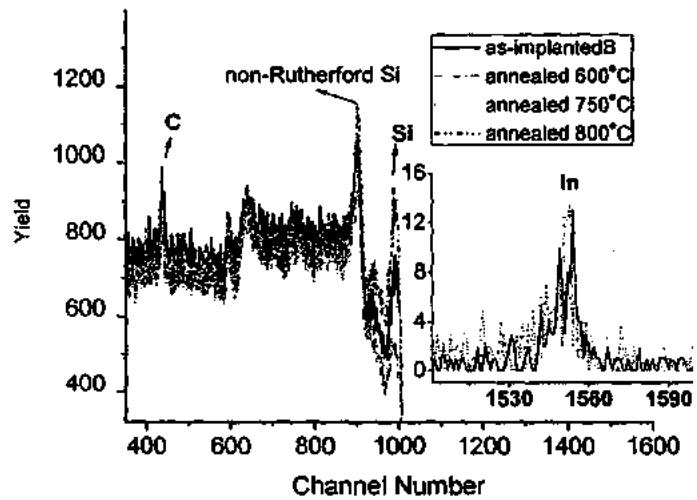

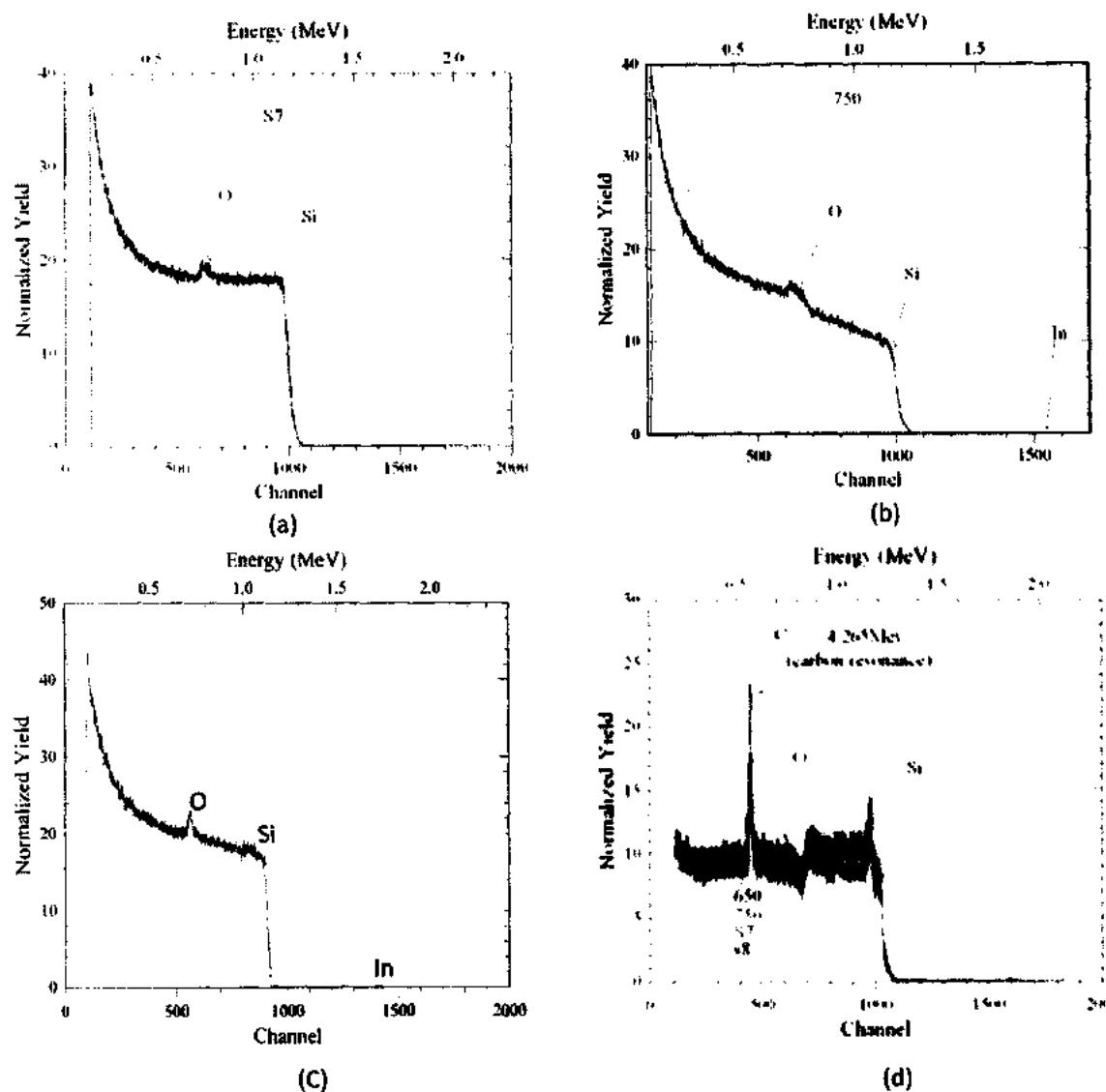

**Figure 5.29:** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing a comparison of as implanted and annealed results of RBS yields. The C, Si and In peaks are also identified.

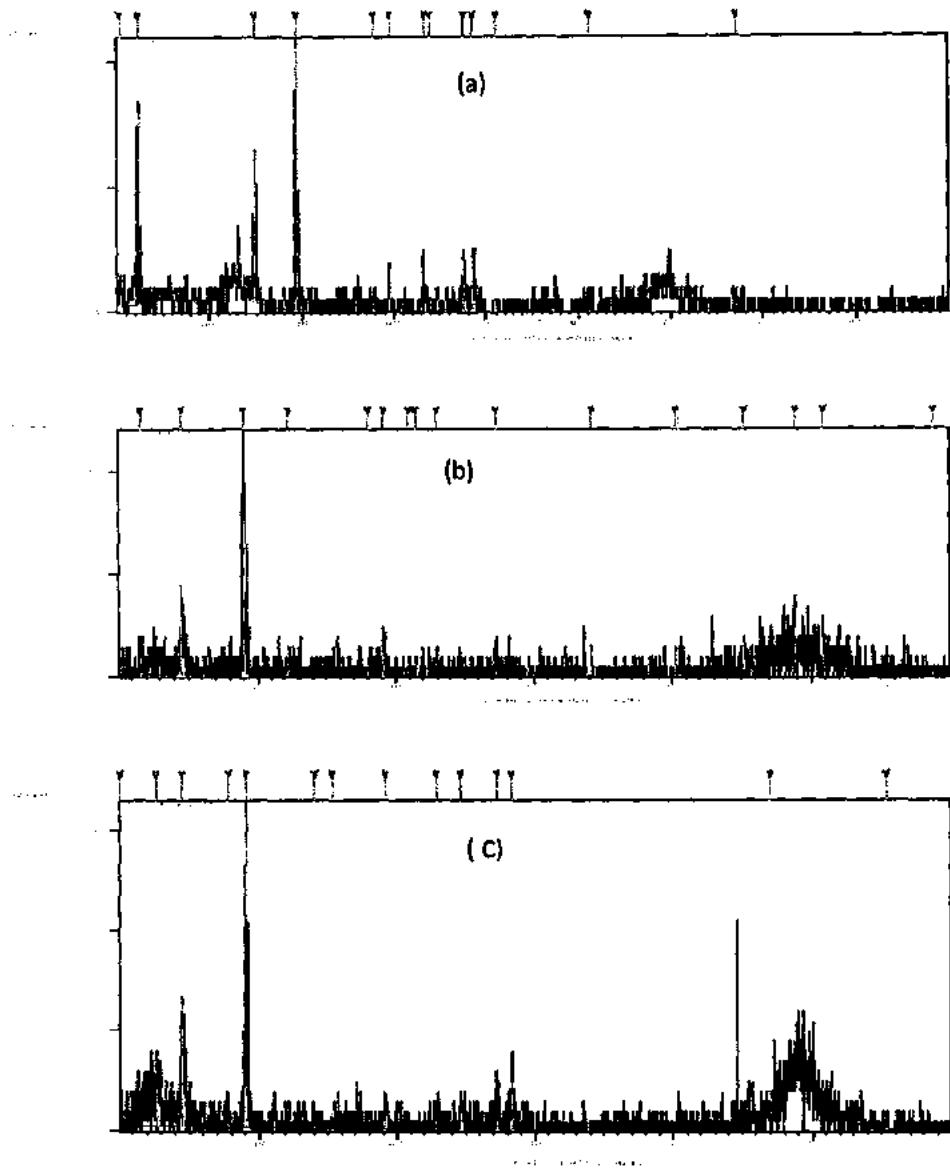

**Figure 5.30:** RBS spectrum recorded for  $\text{He}^{++}$  ions (2.085 MeV) incident on the In+C co-implanted n-type Si substrate showing a comparison of as implanted and annealed results of RBS yields. The C, Si and In peaks are also identified. (a) and (b) RBS Spectrum of as-implanted In+C co-implanted silicon substrate (C) In+C co-implanted Si substrate post annealed at 600°C for 60 sec (d) In+C co-implanted Si substrate post annealed at 650°C for 60 sec.

**Figure 5.31:** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing a comparison of as implanted and annealed results of RBS yields. The C, Si and In peaks are also identified. (a) In+C co-implanted Si substrate annealed at 700°C. (b) In+C co-implanted silicon substrate 750°C for 60 sec. (C) In+C co-implanted Si substrate post annealed at 800°C for 60 sec (d) In+C co-implanted Si substrate for un-annealed and post annealed at 600, 650 and 750°C for 60 sec at 4.26 MeV  $\text{He}^{++}$  beam energy.

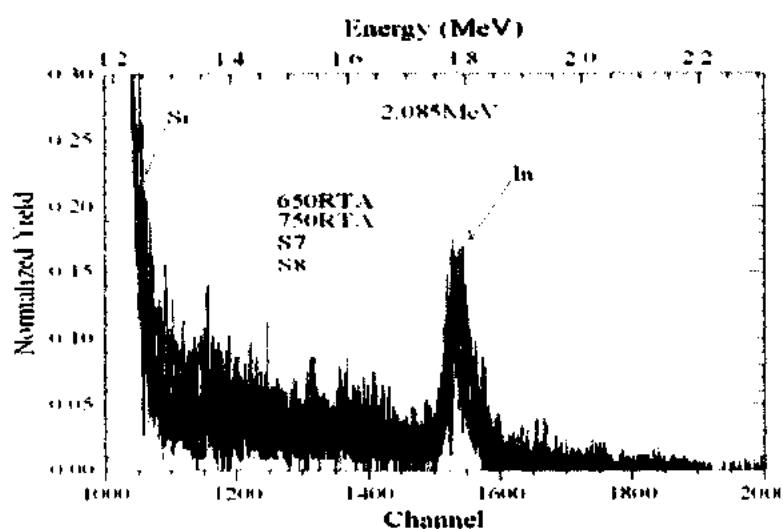

**Figure 5.32:** RBS spectrum recorded for  $\text{He}^{++}$  ions incident on the In+C co-implanted n-type Si substrate showing a comparison of as implanted and annealed (600, 750 and 800°C) results of RBS yields for indium (In) peaks.

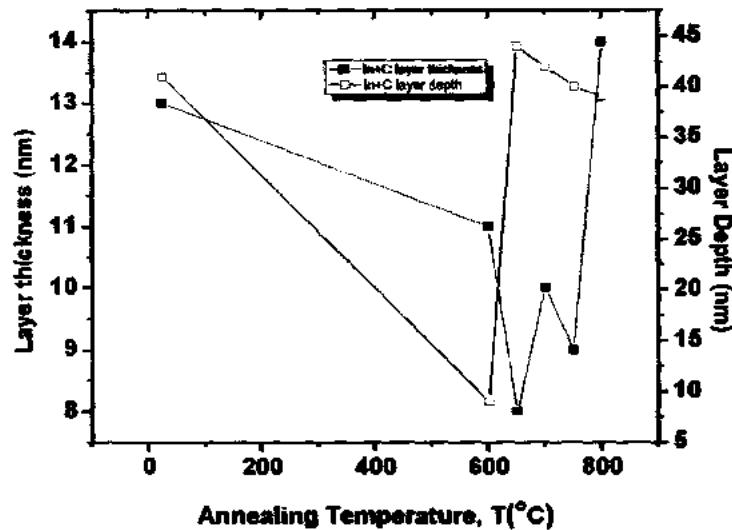

**Figure 5.33:** Variation of ultra shallow junction layer thickness and layer depth in substrate with respect to annealing temperature. Results obtained from Rutherford Back Scattering Spectrometry for In+C co-implanted n-type Si substrate.

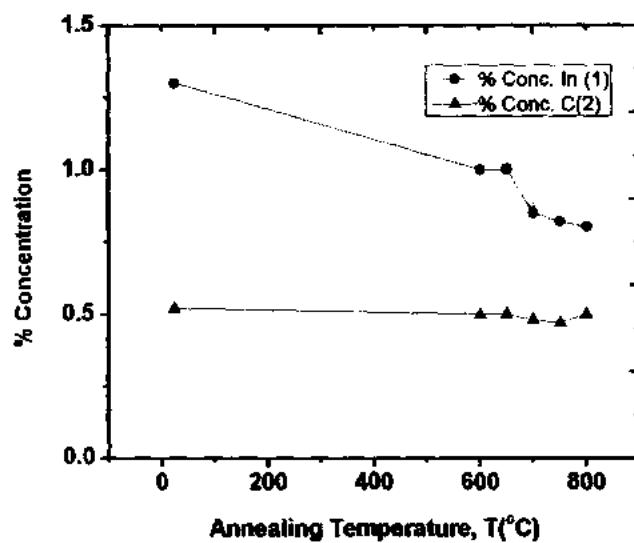

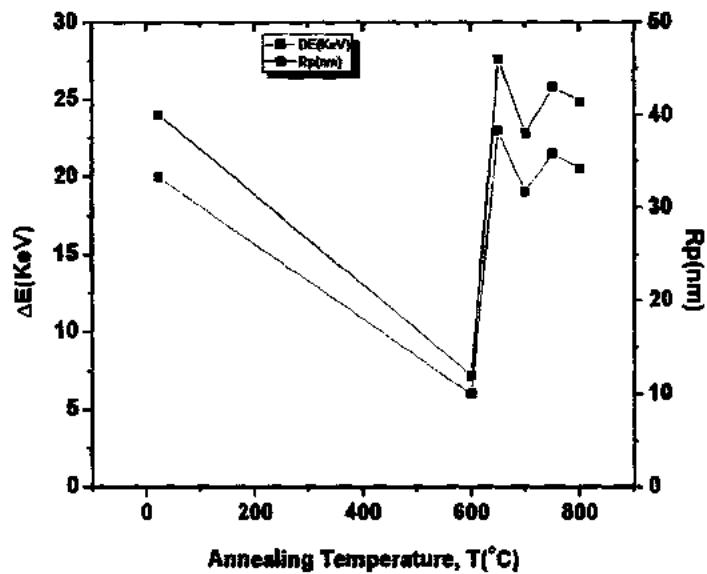

**Figure 5.34:** % Variation of dopant concentration of indium and carbon with respect to annealing temperature for In+C co-implanted n-type Si substrate.

**Figure 5.35:** Variation of projected range ( $R_p$ ) and shift in energy ( $\Delta E$ ) with respect to annealing temperature for In+C co-implanted n-type Si substrate.

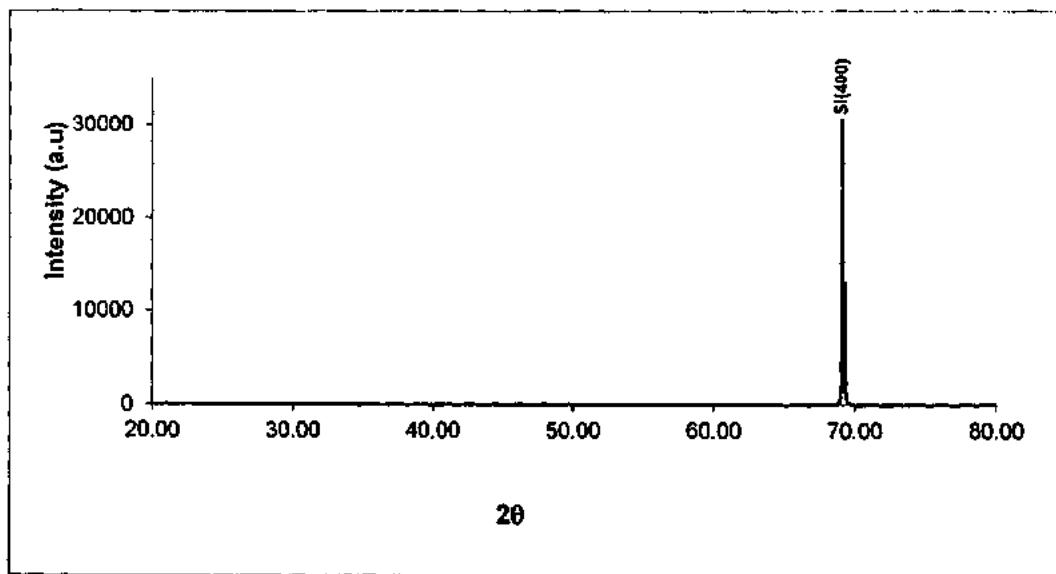

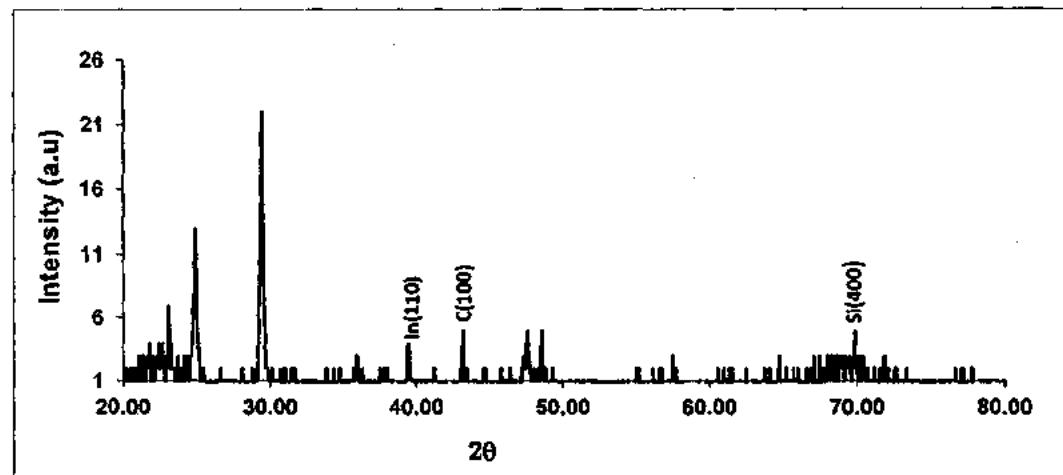

**Figure 5.36:** XRD Spectrum of as-implanted In+C co-implanted n-type Si substrate.

**Figure 5.37:** XRD Spectrum of as-implanted In+C co-implanted n-type Si substrate at high resolution.

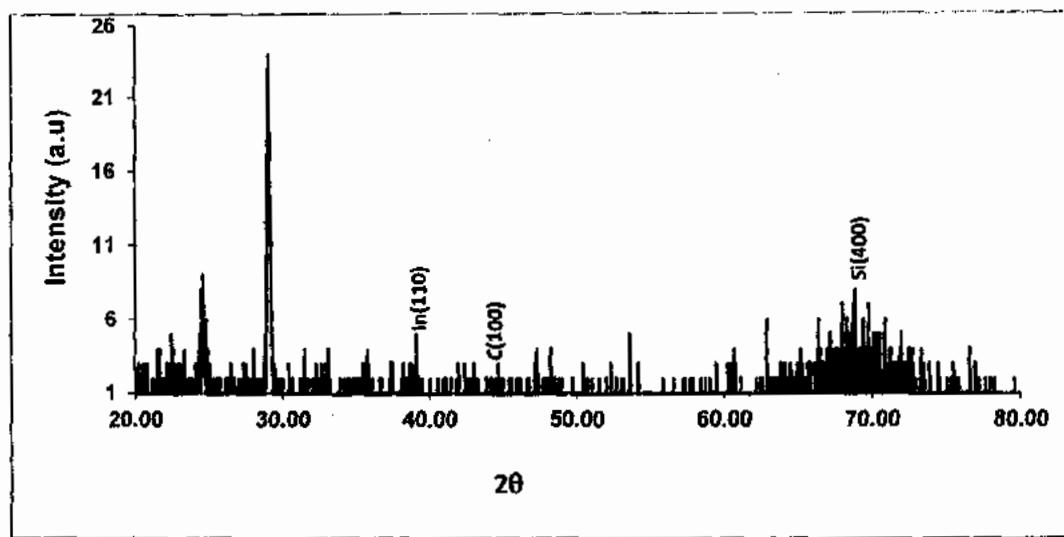

**Figure 5.38:** XRD Spectrum of In+C co-implanted n-type Si substrate. RTA post annealed at 600°C.

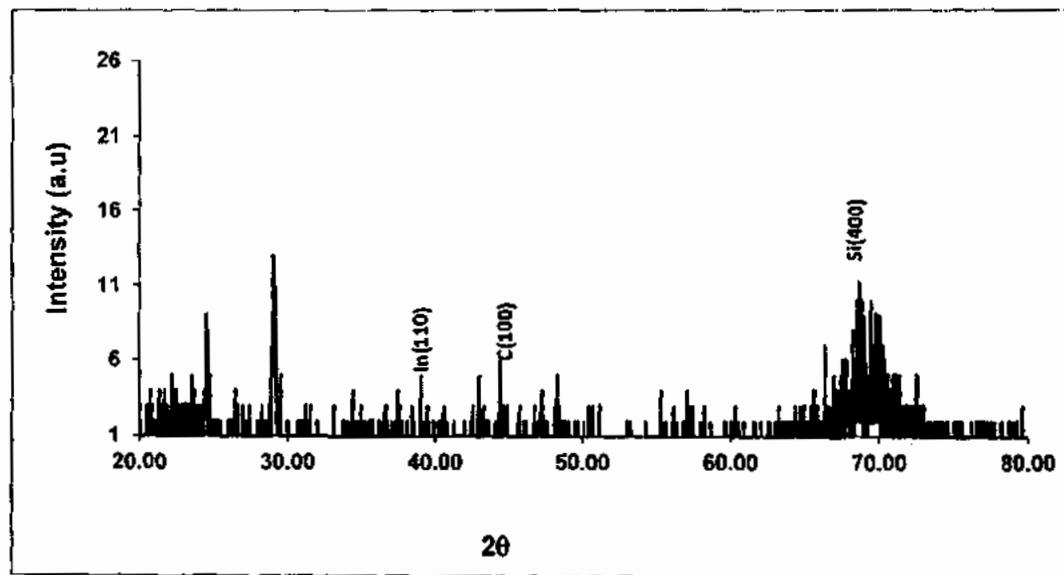

**Figure 5.39:** XRD Spectrum of In+C co-implanted n-type Si substrate. RTA post annealed at 700°C.

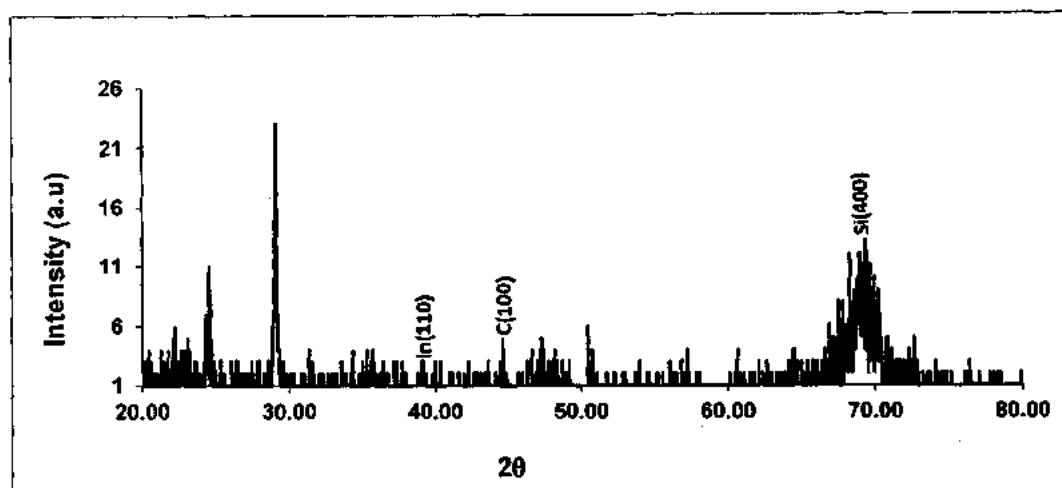

**Figure 5.40:** XRD Spectrum of In+C co-implanted n-type Si substrate. RTA post annealed at 750°C.

**Figure 5.41:** XRD Spectrum of In+C co-implanted n-type Si substrate. RTA post annealed at 800°C.

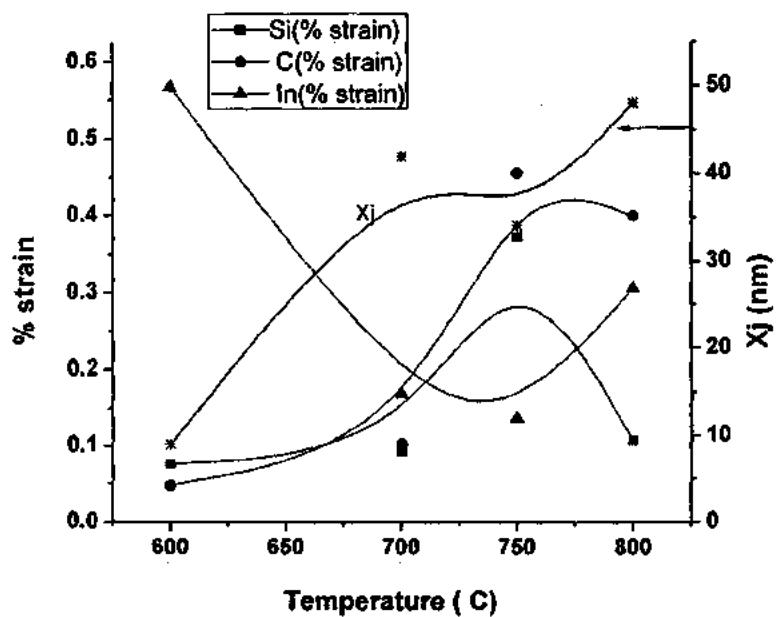

**Figure 5.42:** Variation of percent change in strain obtained from XRD( X,Pert) as a result of In+C co-implantation in n-type Si (100) substrate with respect to annealing temperature ranging from 600°C to 800°C. and junction depth obtained from different techniques produced previously are also plotted to co-relate the results.

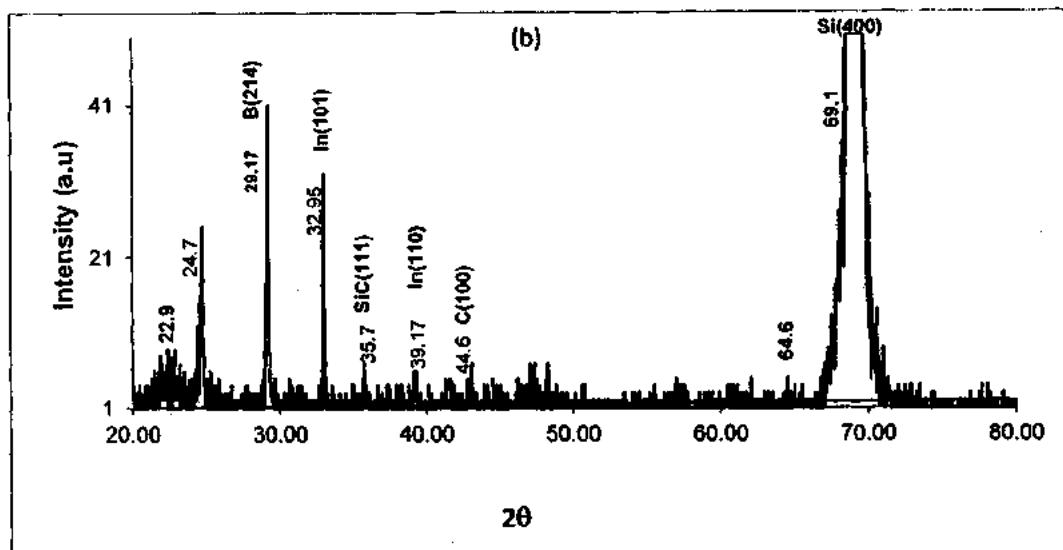

**Figure 5.43:** XRD machine as obtained for In+C co implanted n-type silicon substrate for (a) as-implanted (b) RTA post-annealed at 600°C. (c) RTA post-annealed at 700°C.

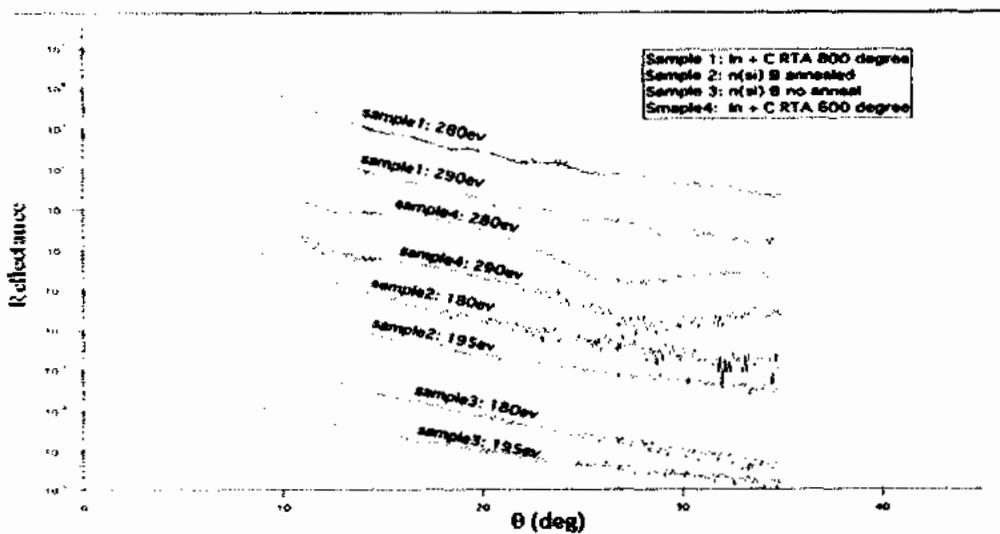

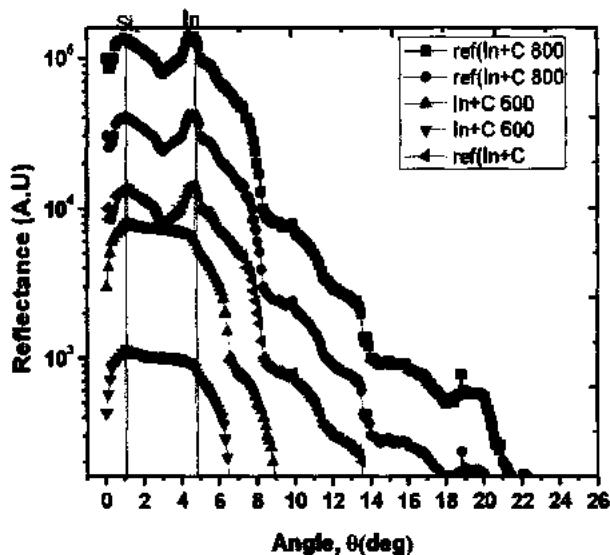

**Figure 5.44:** Shows the experimental GIXRF data and the calculated angular dependence of the fluorescence intensity for the In+C co-implanted silicon substrate.

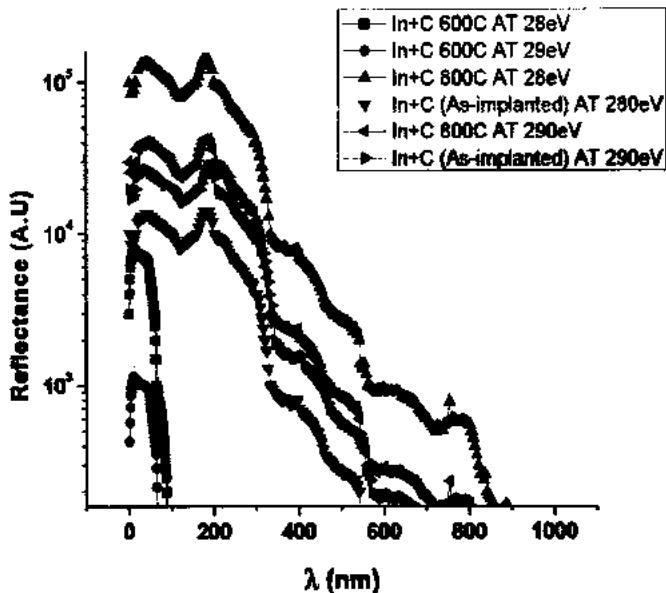

**Figure 5.45:** The experimental GIXRF data shows the fluorescence intensity of In+C co-implanted silicon samples (both as-implanted and annealed) with respect to wavelength.

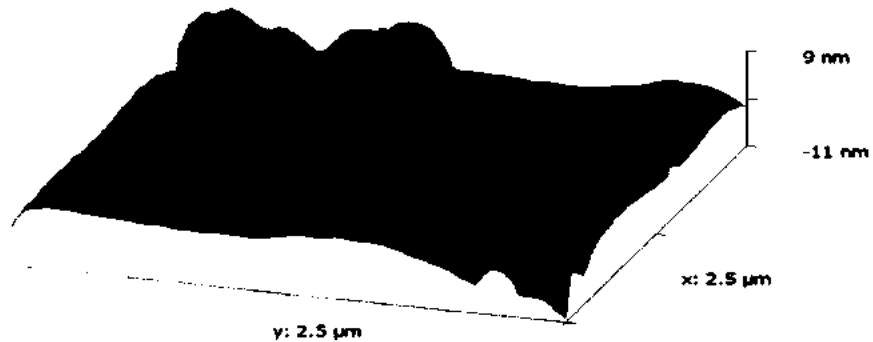

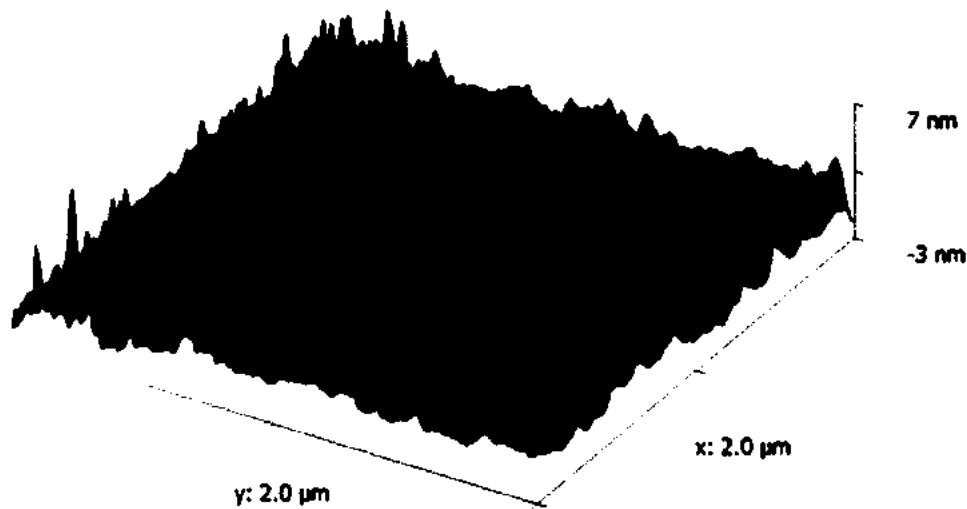

**Figure 5.46:** Atomic Force Microscopic topographical view of the In+C co-implanted Si Substrate before annealing showing extent of roughness and uniformity of the deposited indium and carbon co-implants. This three dimensional view shows negligible degradation of the morphology of the surface after the devised and processed implant strategy for effective utilization in the formation and integration of CMOS ultra- shallow junction.

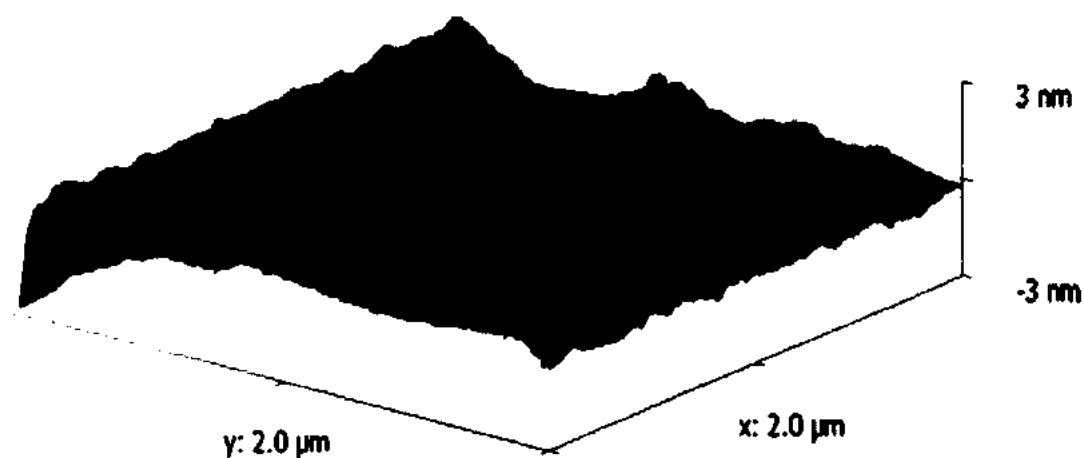

**Figure 5.47:** Atomic Force Microscopic topographical view of the In+C co-implanted Si Substrate RTA annealed at 600°C showing extent of roughness and uniformity of the deposited indium and carbon co-implants.

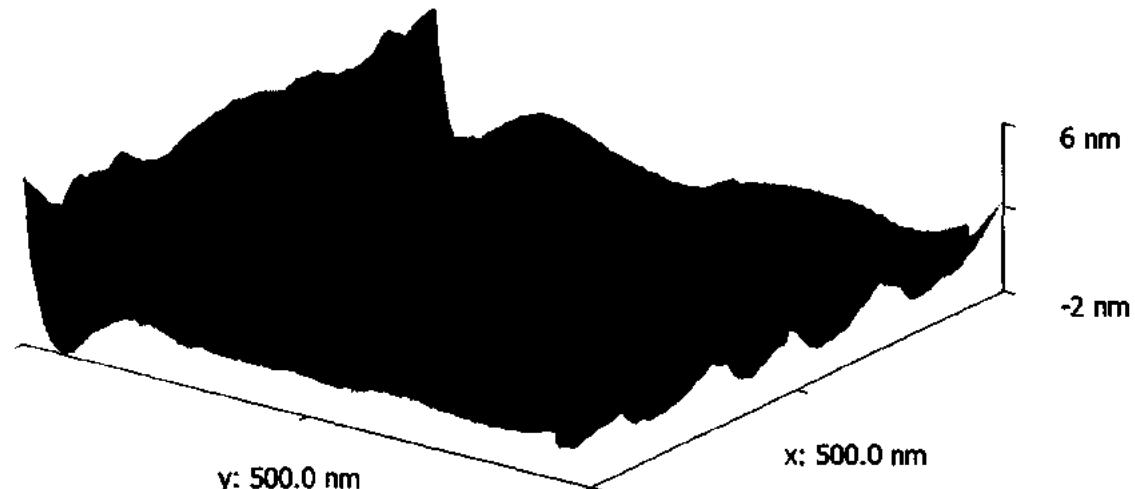

**Figure 5.48:** Atomic Force Microscopic topographical view of the In+C co-implanted Si Substrate RTA annealed at 700°C showing extent of roughness and uniformity of the deposited indium and carbon co-implants.

**Figure 5.49:** Atomic Force Microscopic topographical view of the In+C co-implanted Si Substrate RTA annealed at 750°C showing extent of roughness and uniformity of the deposited indium and carbon co-implants.

**Figure 5.50:** Atomic Force Microscopic topographical view of the In+C co-implanted Si Substrate RTA annealed at 800°C showing extent of roughness and uniformity of the deposited indium and carbon co-implants.

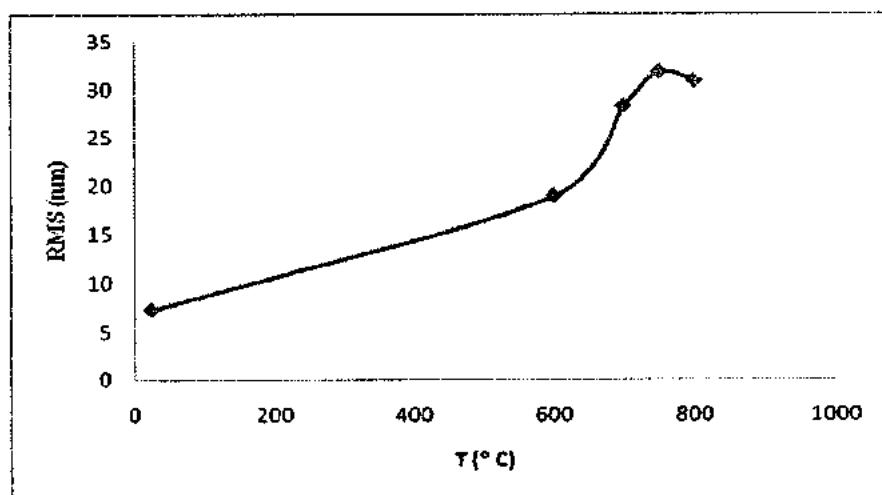

**Figure 5.51:** Variation of surface roughness amplitude parameters as a function of annealing temperature for In+C co-implanted silicon substrates.

**Figure 5.52:** Simulated positions of the 30 keV boron implanted n-type silicon substrate. Simulations carried out by computer code SRIM.

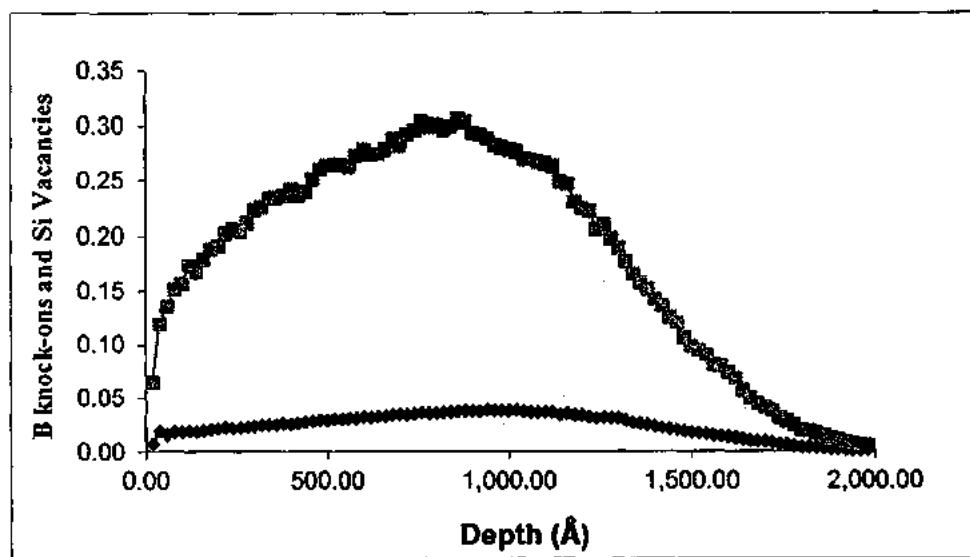

**Figure 5.53:** TRIM simulation results showing defects generated due to implantation of boron (30 keV) in n-type Si-substrate. The high end defect profile exists outside the area of interest.

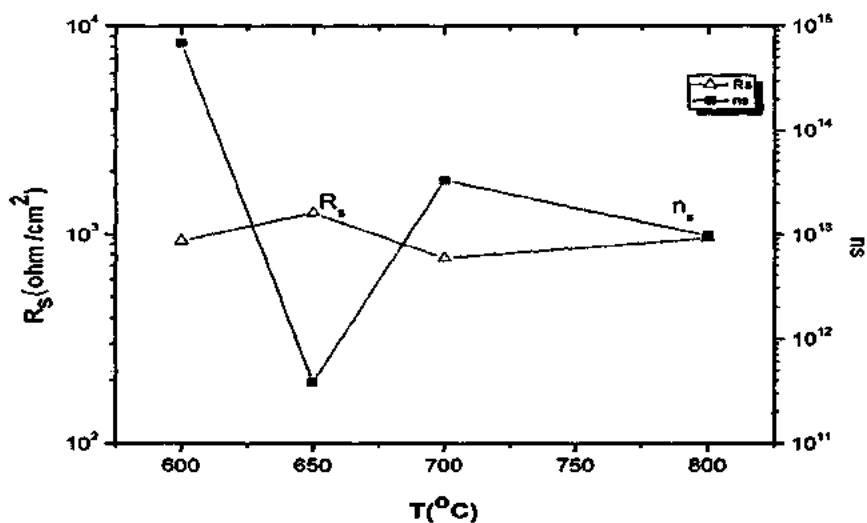

**Figure 5.54:** Effect of annealing g temperature on sheet resistance and sheet carrier concentration for the 30 keV boron implanted n-type silicon (sample#1).

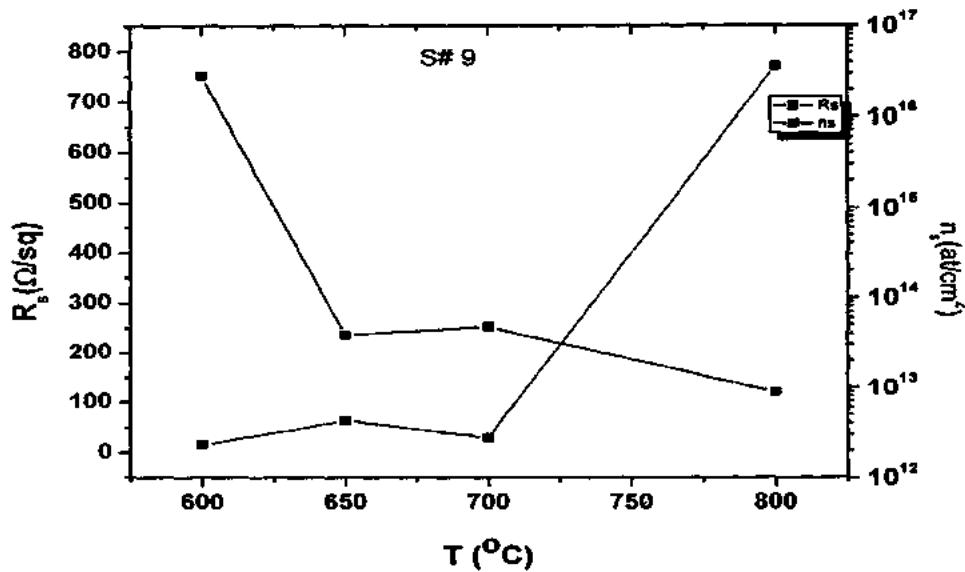

**Figure 5.55:** Effect of annealing temperature on sheet resistance and sheet carrier concentration for the 30 keV boron implanted n-type silicon (sample#9).

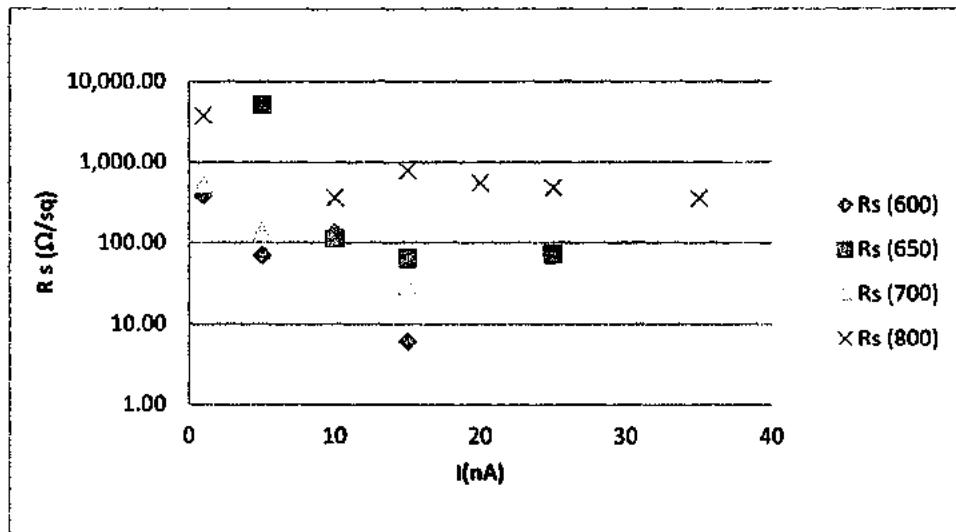

**Figure 5.57:** Effect of applied current on sheet resistance of 30 keV B implanted n-type silicon (sample#1) annealed between temperature regime 600°C-800°C.

**Figure 5.58:** Effect of applied current on sheet resistance of 30 keV B implanted n-type silicon (sample#9) annealed between temperature regime 600°C-800°C.

**Figure 5.59:** Effect of applied current on sheet carrier concentration for 30 keV B implanted n-type silicon (sample#14) annealed between temperature regime 600°C-800°C.

**Figure 5.60:** Effect of applied current on sheet carrier concentration for 30 keV B implanted n-type silicon (sample#9) annealed between temperature regime 600°C-800°C.

**Figure 5.61:** Effect of applied current on sheet carrier concentration for 30 keV B implanted n-type silicon (sample#1) annealed between temperature regime 600°C-800°C.

**Figure 5.62:** Effect of applied current on mobility for 30 keV B implanted n-type silicon (sample#1) annealed between temperature regime 600°C-800°C.

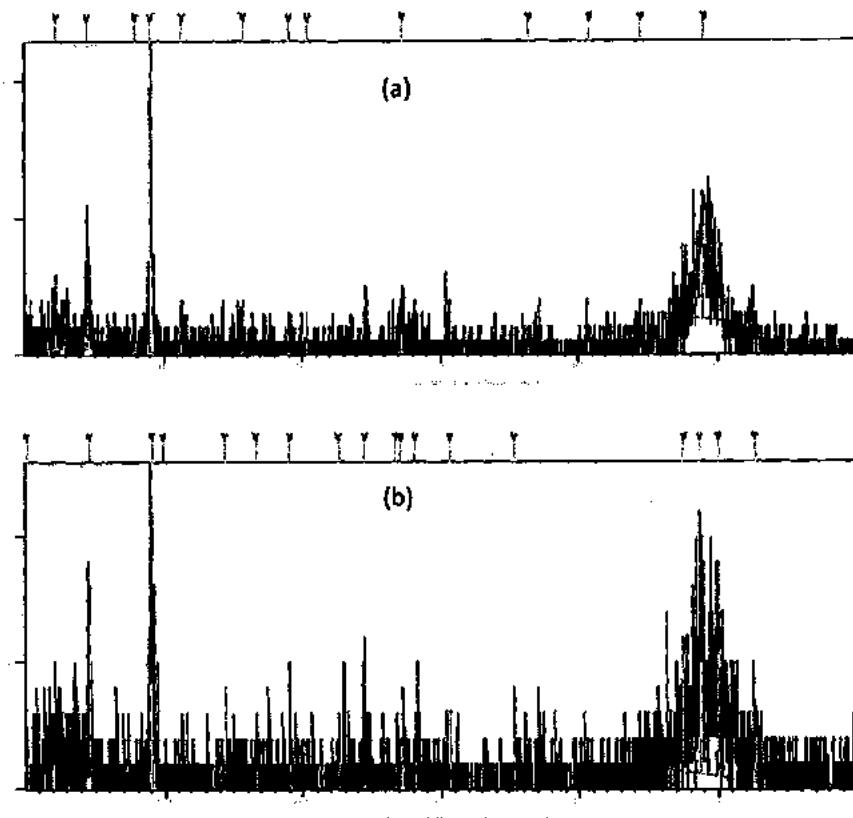

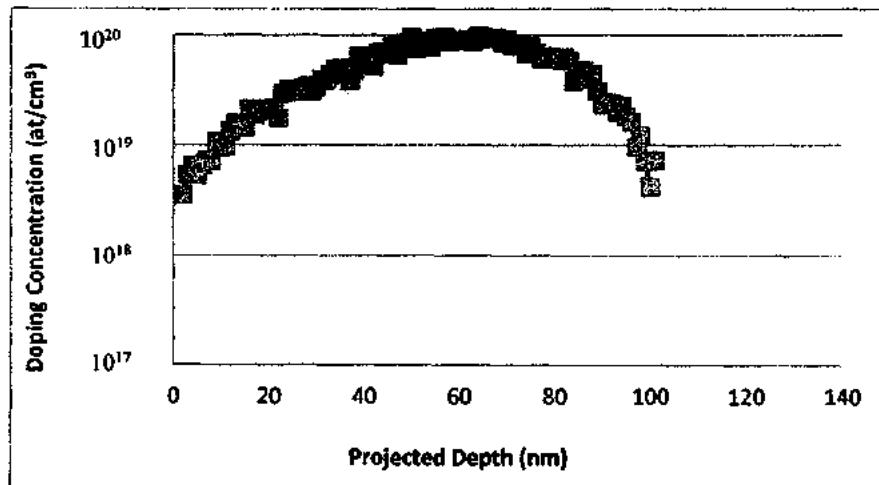

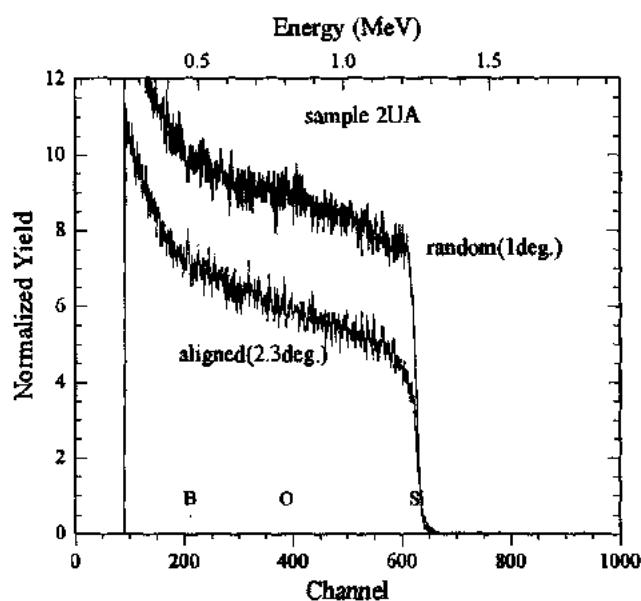

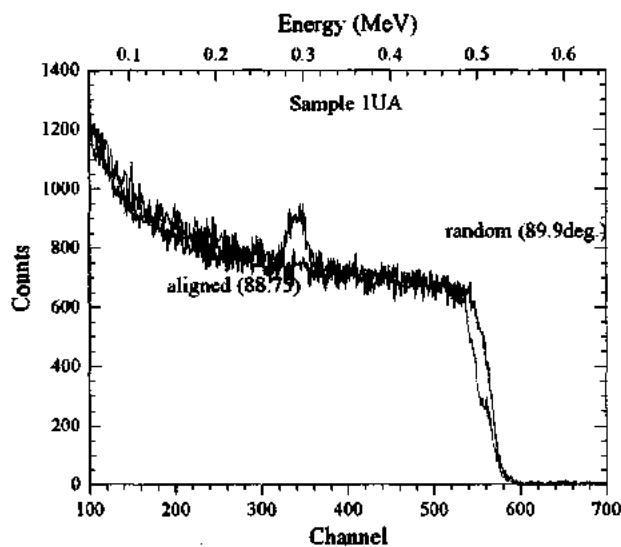

**Figure 5.63:** RBS channeling spectra of born implanted n-type silicon with a dose of  $1\times10^{15}$  at/cm<sup>2</sup> and energy 30 keV (sample#2 as-implanted). The samples are aligned with the (100) channel.

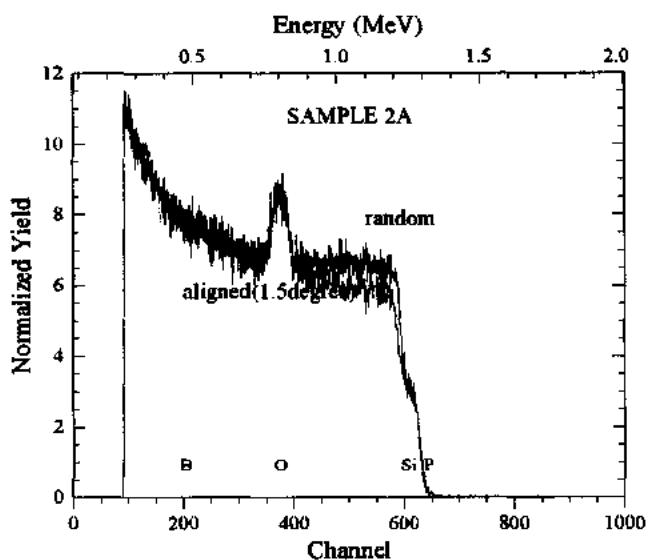

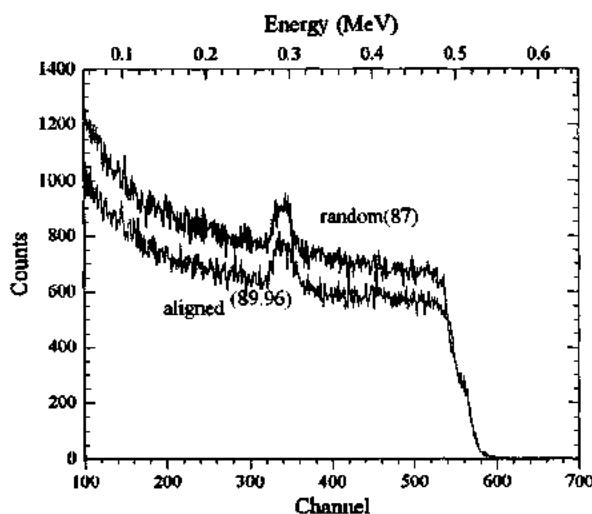

**Figure 5.64:** RBS spectra n-type silicon implanted with a born dose of  $1\times10^{15}$  at/cm<sup>2</sup> and energy 30 keV and annealed at 1050°C (sample#2). The samples are aligned with the (100) channel

**Figure 5.65:** RBS spectra n-type silicon implanted with a born dose of  $1\times10^{15}$  at/cm<sup>2</sup> and energy 30 keV (sample#1 as-implanted). The samples are aligned with the (100) channel.

**Figure 5.66:** RBS spectra n-type silicon implanted with a born dose of  $1\times10^{15}$  at/cm<sup>2</sup> and energy 30 keV and annealed at 1050°C (Sample#1). The samples are aligned with the (100) channel.

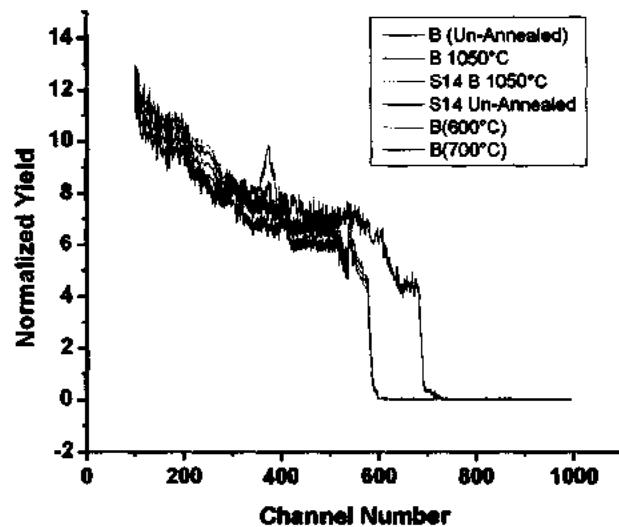

**Figure 5.67:** Comparative normalized yield spectra for n-type silicon implanted with a born dose of  $1\times10^{15}$  at/cm<sup>2</sup> and energy 30 keV for both as-implanted and annealed samples. The samples are aligned with the (100) channel.

## LIST OF TABLES

**Table 3.1:** Review of parameters related to USJ for boron in silicon.

**Table 4.1:** Breakdown of In+C co-implanted Si samples.

**Table 4.2:** Breakdown of B implanted n-type silicon substrate.

**Table 4.3:** Shows d-spacing, FWHM and relative intensities.

**Table 4.4:** Parameters set for GIXRF measurements.

**Table 5.1:** Shows the results obtained from RBS measurements.

**Table 5.2:** Data obtained from XRD measurements.

**Table 5.3:** Data table of junction depths obtained from CV measurement system.

**Table 5.4:** Concentration and back scattered energy of impurity atoms (B) in 30 keV boron implanted n-type silicon.

## Abstract

CMOS being heart of today's electronic industry has been under rigorous research and development. International Technology Roadmap of Semiconductors (ITRS) is placing stringent process requirement in order to meet the issues in scaling of these devices as well as predicting the future of Moore's law. Ultra-shallow Junction (USJ) formation is getting critical both in terms of physical dimensions and consequent device characteristics exhibited once the protocol is adopted in CMOS or Transistor-based nano-scale architecture. We have performed a range of experiments on doped Silicon substrates and created a processing strategy to form USJs in nano-devices having physical dimensions ranging from 10 and 60 nm in several cases. A systematic study of their pre- and post-process simulation on trade-off simulators has been carried out. Structural, optical, electrical and surface characteristics of variety of these pre- and post-processed devices have also been performed and presented in order to provide a realistic assessment on the direct and indirect junction depths, their stability and possible usage in industry.

## **Chapter No. 1**

### **1.1 Introduction**

Complementary Metal Oxide Semiconductor (CMOS) is the most widely used integrated circuit design. It is found in almost every electronic product from hand held devices to mainframes. CMOS uses PMOS and NMOS transistors wired together in a balanced fashion that causes less power to be used than NMOS or PMOS transistors by themselves [1]. CMOS and bipolar transistors are used in combination for many applications. In semiconductor materials and devices, region in which two materials featuring distinctly different electrical properties are in contact is called a junction; e.g. p-n junction and metal-semiconductor junction (contact). Depth (measured from the surface) of the plane in p-n junction at which concentration of acceptors is equal to the concentration of donors is called junction depth. In either P or N-type substrate if the dopant elements attain deep locations in the substrate, then the junction formed will be deep but if these dopant atoms remain near the surface of the substrate than the junction formed will be called a shallow junction. According to ITRS roadmap, transistors with ultra shallow junction are essential requirement for getting high speed devices (gigahertz) [1, 2, 3].

The depth of these junctions is usually controlled by controlling energy of the implanted ions and setting of appropriate RTA annealing temperatures. By scaling down CMOS its performance can be improved in terms of power dissipation and switching time and it has a remarkable feature that as it becomes smaller it also becomes cheaper, faster and enable more functions per unit area of a silicon chip. As a result it becomes able to provide superior performance at reduced cost per function.

The main focus of the thesis is to simulate and fabricate the ongoing protocol to form nano-scale ultra shallow junctions in standard silicon CMOS. These ongoing protocols are the processing sequence (implantation followed by the annealing) already calibrated and matured to the industrial requirements. We have re-visited several such protocols and simulated the established scheme on more than one

modified computer code and verified existence of junction at different annealing temperatures.

The research in this work becomes relevant and commercially viable particularly for post-implant annealed ultra shallow junction protocols. None of the simulation packages currently in use at global fabrication facilities for the batch production of CMOS devices, which incorporates the effects of in-situ annealing (beam heating) during the implantation process as well as the dynamic annealing to electrically activate the junctions. Therefore, it becomes important to look into the modeled data loosely and compare it with the post-annealed schedules. The effect of damage production and subsequent annealing out relatively at high degree thermal treatment is crucial to take into account whenever a new protocol is being established. We have performed and compared these results in order to model and estimate the extent of accuracy in newly developed protocols for USJ formation in nano CMOS devices.

Main parameter that are kept in mind throughout this research work are; (a) To have an abrupt junction, Formation of these junction at minimal reduced depth. (b) To achieve minimum sheet resistivity. (c) To have maximum dopant activation in the selected area.

## **1.2 Scope of the Thesis**

This research involves the fabrication and characterization of ultra-shallow p<sup>+</sup>/n junctions for ultra-large scale integration technologies. For the formation of ultra-shallow junctions, silicon substrates were first preamorphized by Si<sup>+</sup>. Indium and carbons are than co-implanted by using low energy ion implantation and in second set boron ions were then implanted using ultra-low energy ion implantation in n-type silicon. Both types of samples were than post annealed between temperature regimes 600-800°C. The ultra-shallow junctions were mainly characterized using, Hall Measurement System, Keithley 4200, CV Measurement System, Ellipsometry, Rutherford backscattering spectrometry (RBS), Grazing Incidence X-Ray Fluorescence (GIXRF), XRD and Atomic Force Microscopy to study the impact of implantation energy and post annealing temperature on dopant depth, electrical

### **1.3 Objectives of the Thesis**

The primary goal of this thesis is to achieve highly doped and electrically activated ultra shallow junctions (USJs) with suppressed sheet resistance at different annealing temperatures by using low thermal budget RTA. To achieve the primary goal of this work, the studies will be carried out in different sections associated with their own specific objectives described as follows:

1. In order to find out the resultant range and damage profile in the Si due to Indium and Carbon ions, we performed rigorous simulations with various ion energies at different incident angles' using a computer code Stopping and Range of Ions in Matter for the present work. Further, Silvaco TCAD code was used to predict the distribution of defects in the Si substrate due to the carefully chosen ion implant schedules. These simulations constitute the central part of the research work, because very careful parameter optimization is required to study the process sequence to fabricate ultra-shallow junctions.

2. Samples were fabricated on the basis of these simulation results.

3. Samples activation and junction formation was checked for further processing.

4. Only those samples were further processed in which junction was established and electrically activated.

5. To determine the effect of ramp-up rates on dopant redistribution, samples were post annealed (RTA) between temperature regimes 600-800°C.

6. We have investigated for both pre- and post-annealing process to create a processing strategy for potential applications in nano-devices. For this purpose as-implanted and post annealed samples were than characterized to study the effects of annealing temperature on dopant profile (junction depth, sheet resistance, mobility, absorption coefficient, refractive index, strain and surface morphology) with those obtained before and after annealing temperature.

7. The formation of junction and its depth is verified by different techniques.

**1.4 Organization of the Thesis**

The organization of the thesis is highlighted as below;

**Chapter 1** covers some introductory information pertaining to the subject matter of this study. **Chapter 2** describes necessary background of the simulation and experimental tools used for the synthesis and characterization of the samples. **Chapter 3** provides the comprehensive Literature Review on the subject while the experimental details are provided in **Chapter 4**. **Chapter 5** contains results and discussions and analysis of these results. **Chapter 6** This chapter summarizes the major results and findings, and provides conclusions based on these findings in the light of the objectives of this research. Recommendations for further experimental work are also given.

**Chapter No. 2****2.1 Description of Physical Phenomenon and background Physics****2.1.1 Shallow and Ultra Shallow Junctions**

CMSO (Complementary Metal Oxide Semiconductor Field Effect Transistor) is the semiconductor technology used in the transistor that are manufactured into most of today's computer microchips. Semiconductors are made of silicon and germanium, material which "sort of" conduct electricity, but not enthusiastically. Areas of these material that are "doped" by adding impurities become full-scale conductors of either extra electron with a negative charge (n-type transistors) or of positive charge carriers (p-type transistor) [1,2]. A CMOS semiconductor uses both NMOS (negative polarity) and PMOS (positive polarity) circuits. In CMOS technology, both kinds of transistor are used in a complementary way to form a current gate that forms an effective means of electrical control. CMOS transistors use almost no power when not needed. This makes them particularly attractive for use in battery-powered devices, such as portable computer. Personal computers also contain a small amount of battery-powered CMOS memory to hold the date, time and system setup parameters. As the current direction changes more rapidly, however, the transistors become hot. In integrated circuit technology, millions of instruction can be executed in a single second [2].

A CMOS based chips has impurities added to it, a process called "doping", such allows the chip to store an electrical charge called capacitance. In order to control the electrical currents needed, the capacitance must be discharged and recharged which takes time and causes the transistors on the chip to heat up. This production of heat, limits the speed at which microchips can operate. For this reason microchips have poor yield rates. SOI microchips are not doped with impurities, which eliminates such of the capacitance and allows an SOI microchip to operate faster and cooler and it was found that for this silicon oxide film is perfect enough that it bonds with the pure crystal silicon layer [3].

The word junction is used in solid state electronics is a common region comes in mind that is situated between n and p-type materials and due to this junction, depletion region is formed. It is achieved by having either p or n type substrate and doping it with opposite species. If the dopant elements attain deep location in the substrate, then the junction formed will be in that corresponding depth. But if these dopant atoms remain near the surface of substrate, then junction will also be formed, but this type of junction will be known as shallow junction. A junction just below the surface of the substrate will be known as Ultra shallow junction (USJ). But in all aspects depth should be maintained to such extend that there should be no effects of it on device operation due to some unavoidable parameters. Also as devices are having USJs, their dimensions are reducing which means less consumption of power and more advantage in technology. Device should have minimum sheet resistivity, thus providing ease for carriers to flow in device; there should be sufficient number of active dopant carrier in the device to support the flow of the charge. The junction is called abrupt junction when the concentration of the dopants is constant on both sides of the junction and changes instantly at the junction [4].

### **2.1.2 Simulation Techniques**

During the last decade, numerical modeling of the semiconductor fabrication process has increasingly become an important design and development tool in semiconductor technology. Development of a new or improved semiconductor device runs through a number of distinctive phases. In the first phase there is the initial design of the new device including the first setup of the fabrication process. Mostly options from already well-established processes and technologies are taken to form the initial new process. After this first design the process undergoes an optimization loop.

There by the process is tuned and improved to reach the specification and device characteristics. Finally, the process is ready for manufacturing, where impacts of manufacturing changes on performance and yield calculation are taken under investigation. In all these phases' simulation tools can play a crucial role for the reduction of the cycle time for device prototypes. A modern integrated circuit (IC) process consists of several hundreds of single process steps. The goal of process

simulation should now be the full characterization of the most critical parts by means of numerical simulation tools [5].

Apart from being valuable in development and optimization of IC fabrication process, process simulation are necessary to predict accurate impurity profiles for subsequent use in device simulator programs. With the decreasing scale of the device dimensions there is growing demand for process simulator that account for multi-dimensional effects and accommodate more realistically the physical behavior during process of the device. The process models have to fulfill the requirement on accuracy, reproducibility, and predictability even in the development phase, because of the large manufacturing chain. From the process simulation point of view there are still process steps, such as cleaning, which need not be simulated, because their influence on subsequent process steps is insignificant or can be included in the next process step. The simulation task for process simulation can be reduced to the critical structural and impurity related process steps [6]. To model the experimental results, the process simulators used in this research are described below.

#### **2.1.2.1 Simulators used for implantation optimization (SRIM & SUSPRE)**

Two international simulation packages (computer codes), naming industrially trade-off IBM's Stopping & Range of Ion in Matter (SRIM) and Surrey Ion Beam Center's "Surrey University Sputter Profile Resolution from Energy" (SUSPRE) introduced by Ziegler. J. F, 2008 are used in this work [7]. In these packages different input parameters can be set in order to achieve required doping profile. In general by changing the value of each input parameters such as energy, fluence (dose) and angle of incidence of the incident beam simulation plots can be achieved showing various output parameters of the implantation which are steady state broadening, on set for amorphization, sputtering yield, erosion rate, nuclear and electrical energy deposited, mean range and standard deviation from SUSPRE. By SRIM 2008 the output parameters are collision plots in the form of longitudinal and lateral directions, ion distribution, lateral distribution, ionization n, phonons, and energy to recoil and vacancy requirements such as specified depth attained by dopant ions for ultra-shallow junction and implantation energy for minimal damage event created by ion beams etc [8].

**2.1.2.2 Simulator used for Process optimization (TCAD)**

Simulator for Technology Computer-Aided Design (TCAD) is already a fundamental part of silicon industry and has largely promoted the development of silicon-based devices [9]. As optoelectronic devices are gaining importance in daily life appliances, simulator for their simulation analysis play a significant role in the near future. Today, several simulators for lasers have been released to the market but they are still challenged when dealing with the complicated devices like VCSELs. At the very beginning, Senturus, which is released by Synopsys, Inc., was chosen for this work.

**2.1.3 Ion Implantation**

A non-thermal method of introducing impurities into Silicon is called ion-implantation. In this process doping atoms are ionized, accelerated and directed at the Silicon wafer. The high-energy ions enter the crystal lattice, collide with the Silicon atoms and finally come to rest. The energies required in this process are in the range from a few keV to MeV and for the commonly used impurities such as Boron [10, 11] Indium, Carbon [12] Arsenic [4] and Antimony etc., this process can be used to implant ions from a depth of few nanometers to 10-1000 nm beneath the Silicon surface [11]. The acceleration energy control the average depth of the dopant atoms in the silicon and ion current during implantation controls the ion dose. Therefore to form a very shallow dopant layer, low energy implanters are needed. Ion implantation has become important because of its ability to control, with precision, the thickness and doping level of implanted layers by the energy and dose of the ion species [1].

Initially ion implantation was developed as a mean of doping these semiconductor elements of integrated circuits. It has several advantages over growth or diffusion techniques, such as accurate dose, depth control, good uniformity, reproducibility of doping, low temperature or room temperature operation, minimal lateral spread of dopants beneath a mask, and several dopants may be added. It is also often possible to introduce dopants, which cannot be introduced by diffusion. Because of the speed, accuracy, cleanliness and controllability of the process, it has become the standard for this type of work [13]. There exist several sources of evidence on the effect

that pre-amorphization enable obtaining better electrical activation of the dopants [14]. When all of the dopants being incorporated within a fully amorphized region above the position, where End of Range (EOR) defects would occur, this in turn allows more dopant atoms to occupy substitutional sites. By annealing at low temperature, dopants diffusion and probability of clustering can be minimized [15]. Ion implantation has become a routine method for the introduction of impurities into semiconductors [16].

This technique involves the production of positively charged ions, which are accelerated through a controlled potential and then allowed to impinge on the sample. Unlike diffusion methods, ion implantation allows independent control over the depth and concentration of the dopant. The main side effect of the technique is the production of a damaged layer because of the disturbance of the lattice introduced by the collisions induced, these damaged layers or defect can be removed using different annealing techniques. Due to the easy implementations of this technique, the microelectronic and nano-electronics devices industry has been extensively adopted it in the production from the last few years. Especially in the area of integrated circuit fabrication, it has become the dominant technology, for example in the production of CMOS devices.

#### **2.1.3.1 Ion Stopping and Range**

When an energetic ion enters a solid it loses energy through interaction with the electrons and nuclei of the target atoms. There are two basic stopping mechanisms by which energetic ions can be brought to rest. They are nuclear and electronic collisions [17]. In the first one kinetic energy is transferred to the struck atom, with the considerable deflection of the trajectory of the bombarding ion. At high velocity, or more precisely high incident energy, the nuclear effect is negligible and the electronics losses dominate the slowing down process. In the second one, the energy will be transferred to the electrons of the target atoms, and the ion will suffer no or negligible deflection. The sum of the two mechanisms gives the total stopping power (S). The usual expression for it is given in equation 2.1 [17]:-

$$S = (dE/dx)_n + (dE/dx)_e \quad (2.1)$$

Where  $dE/dx$  is the energy loss per unit path length of the ion. By the evaluation of the stopping power and its integration it becomes possible to find how far an ion will travel

inside the target before losing all its energy and coming to rest at some depth. The relative importance of the two mechanisms of stopping is well described in figure 2.1. In the usual cases of implantation for device fabrication the typical used range is between 10 to 200 eV. This energy window falls at the left of the figure where mainly the nuclear stopping mechanism takes place.

Both the stopping mechanism (electronic and nuclear) contributes to the energy loss of the incident ion inside the target. The ion once implanted follows a random path as it moves through the target. The total path length in Silicon is composed of a mixture of horizontal and vertical motion and is called Range (R). The projection of the range in the vertical direction (normal to the surface implanted) is called the Projected Range ( $R_p$ ). Considering the large concentration of ions introduced during the implantation process (usually larger than  $10^{12}$  ions /cm<sup>2</sup>), it is possible to consider that ( $R_p$ ) represents the average depth of the implanted ions. The distribution about that depth can be approximate as a Gaussian centered at ( $R_p$ ) and with a standard deviation ( $\sigma$ ) [18]. With this assumption the ion concentration  $n(x)$  as a function of depth will have the following expression:-

$$n(x) = n_0 \exp \left[ \frac{-(x-R_p)^2}{2 \sigma^2 p} \right] \quad (2.2)$$

Obviously this model is an approximation and the real distributions differ from it. To take into account those differences justifying the discrepancies between this real profile, other parameters such as Skewness and Kurtosis can also be considered [18]. When the implantation target is solid with crystalline structure the impinging ion can move through particular direction such as atoms rows or planes, so that it travels long distances without undergoing nuclear collisions. Ions are steered down these channels by glancing collision with the atoms rows or planes. Hence they can travel through the solid longer distances resting eventually at deeper position. This phenomena is known as channeling and it is responsible for an asymmetrical final implant distribution inside the target resulting in a tail on the deeper side of the distribution [19].

### 2.1.3.2 Implant Damage

While ion implantation allows an accurate dose of impurity atoms to be placed on a controlled distance from the surface of the substrate, it has the disadvantage of introducing damage to the material. When the high energy ions collide with the substrate they displace the substrate atoms from their positions in the crystals lattice. In addition only a small number of the implanted impurities end up in the electrically active lattice sites. As seen, an in its path along the atoms array of the solid target bombarded, loses its energy in different ways (nuclear or electronic collisions) reaching finally a resting position.

**Figure 2.1:** Relative amount of nuclear and electronic stopping power as a function of ion velocity.

In the case of electronics the energy lost by the ion is transferred to the target producing ionization or electronic excitation with consequently photon and thermal emission. In the nuclear scattering regime the effect is different. Since the binding energy of a lattice site is only 10 to 20 eV [20], so it becomes quite easy to produce displacement of the target atoms. However both ions and displaced atom have enough

energy to produce further displacement traveling through the target. The energy is spread over many moving particles resulting in the process called collision cascade. The overall result is the production of (vacancies) missing atoms in lattice positions and (interstitials) atoms resting in the lattice position producing a substitutional impurity. Implanting heavy ions into a light target results in a denser cascade with a resulting defects structure very different from the other extreme (light ions in heavy target). In the first case when the heavy ion (like Indium or Antimony) impinges on a surface of Silicon the deflected ion continues into the lattice accompanied by a primary recoil atom. Both of them could possess enough energy to produce other displacement in the following collisions. The ion energy shared between a numbers of atoms recoiled and the ion impinging will produce a collision cascade having a cylindrical form with its axis on the path of the ion. As the energy of primary ions decreases the fraction of energy transferred to lattice atoms increases. The recoil density will increase as the ion penetrates deeper in to the solids, until the ion energy will not be able to promote the displacement of lattice atoms. The disordered region produced by all the ions implanted will result in the production of a background zone of simple defect structures and a distribution of larger, disordered region.

The ion energy has an important effect on the amount of damage induced. In fact only nuclear scattering damages the target and is a function of the ion energy. However, for a given energy the heavier the ion implanted the larger will be the nuclear stopping power and consequently the more damage is produced [18].

#### **2.1.4 Annealing**

As an ion travel through the target it undergoes a series of nuclear collisions. Every time the ion is scattered a fraction of its energy is transferred to a target atom, which is displaced from its original position. The binding energy of a lattice site is only 10 to 20 eV [20], so it is easy to transfer enough energy to free an atom from its position and make it travel through the target as a second projectile. So both the ion and displaced target atom travel and cause further displacements. Eventually the energy becomes too small and the cascade stops. But after many ions have been implanted an initially crystalline target will be so disturbed that it will be changed to a highly

disordered state. Annealing is then required to repair the damage and put dopant atoms on substitutional sites where they will be electrically active. The success is often measured in terms of the fraction of dopant, which is electrically active however the challenge is not simply to repair the damage and activate the dopant, but to minimize the diffusion.

The time and temperature cycle of the heat treatment of implanted samples, known as the annealing cycle. It has a significant influence on the sitting of implanted impurities within the host substrate lattice. It is the installation of impurities within the host lattice, which determine the resistivity and consequently the conduction properties of the material. The concentration of activated impurity atoms is a function of the implanted dose as well as the annealing cycle. The goal of the post implant annealing is to restore the silicon lattice to the pre-implant state and to electrically activate the implanted dopant atoms. Since most implanted dopants do not occupy substitutional sites upon implantation [21]. A thermal step is required to provide the energy required to move the atoms to the correct lattice site. Electrical activation of the dopants in an amorphous layer proceeds differently from the activation of dopants within primary crystalline damage. Electrical activation in amorphous layers occurs as the impurities are incorporated into lattice sites during recrystallization [21, 22].

Electrical activation in areas of primary crystalline damage proceeds with more complexity. The movement of doping atoms according to a dopant gradient in a semiconductor material is called diffusion. It occurs during any high temperature processing steps, either as intentional or as parasitic effect. Due to the requirement of very shallow junction in modern semiconductor technology, diffusion is mainly a parasitic effect of the annealing step after ion implantation or of an oxidation step which is performed at high temperatures [21]. Nevertheless there are still applications in the (well) formation in complementary metal oxide semiconductor technologies or the in-diffusion of dopants from a chemical vapor source. There are strong variations in the diffusivity of different dopant species. Besides, diffusion can be enhanced by oxidation or retarded by nitridation, because these processes generate point defects at the surface. These surfaces generated point defects as well as implantation induced point defects can have a strong influence on the diffusivity because they facilitate complex diffusion

mechanism like transient enhanced diffusion [22]. At high concentration levels the dopant can form non-mobile cluster or precipitates which decrease the average diffusivity. The exact control of all diffusion mechanism is a very critical issue during the manufacturing of a semiconductor device because redistribution of the dopants significantly influences the electrical characteristics. When clustering and precipitations of dopant concentrations above the solid solubility limit (SSL) are introduced into the crystal lattice, a portion of the diffusion atoms appears to be electrically inactive at room temperature. As dopant concentrations above the SSL are common in today's technologies, we have to take into account the clustering phenomena for the simulation of the dopant diffusion [23]. Types of annealing used in this research work are Rapid Thermal Annealing (RTA) and furnace annealing:

#### **2.1.4.1 Rapid Thermal Annealing (RTA)**

Rapid Thermal Annealing (RTA), also referred to as Rapid Thermal Processing (RTP), is the most popular technique used today to activate dopants following ion implantation. The system configuration can vary greatly. However, for shallow junction formation the goal is the same: rapidly heat the wafer to a high temperature (600-800°C) for a short time (a few seconds or less). Lower temperatures for such short time result in little dopant activation and insufficient damage removal. The time the wafer is held at peak temperature is often referred to as the soak time. A popular type of RTA is a spike anneal. This involves ramping the wafer up to peak temperature and then ramping it down, holding it for only a few milliseconds at peak temperature. The ramp-up rate and minimum hold time at peak temperature is limited by the system configuration. Two common configurations are the lamp-based system and the hot-walled system. Since the process involves heating the whole wafer, the wafer is ramped up from 600-700°C where it is held for a few seconds before ramping up to peak temperature. This reduces the effects of stress that develops in the wafer due to thermal gradients and layers with mismatched lattice constants. Unfortunately, the hold at 600-700°C increases the thermal budget of the process. Also, since the whole wafer is heated, and cools by radiative cooling. [24]. Slow cool-down rates also add to the thermal budget seen by the wafer. In current mainstream IC processing heat treatment is achieved by

means of large, hot-wall ovens in which wafers are processed. In RTP, only the relatively small thermal mass of the wafer itself is heated to and cooled from the processing temperature. The walls of the reaction chamber are water-cooled and remain at room temperature. The windows are air-cooled or water-cooled. Consequently, process steps may need only ten seconds for completion. A wide variety of arrangement for heating wafers in RTP systems with infrared and/or visible light have been designed and built. Figure 2.2 represents a diagram of generic RTP system. The wafer is supported by three quartz pins, which contact the wafer near its edge (omitted from figure) and heated by lamps or lamp array, which is separated from the chamber by a transparent window. Light passes from lamp array to the wafer through the upper window. The lower window can be used for remote measurement of wafer temperature or for application of ultraviolet light to the wafer. Power requirements for the lamp array are typically from several to several tens of KW [25].

Figure 2.2: A Generic RTP system [25].

The advantages for the RTP system is the lower thermal budget, better process repeatability and shorter high temperature processing time for the wafer. However, since the wafer is very far from being in thermal equilibrium with its surroundings, the problem of temperature non uniformity over the wafer is much more acute. During the IC manufacturing silicon wafers undergo a number of processing steps typically at high temperatures under various atmospheric conditions, and high levels of heat power. However the control techniques required to provide real-time monitoring. One of the major problem is the control of the wafer temperature since it is required to maintain near uniformity temperature distribution over the wafer at all times, while following

fast temperature trajectories. A lot of research has been done to solve the non-uniformity problem. It is necessary to measure the temperature at various points across the wafer during RTP for multivariable control. The most popular approach is the use of pyrometers located outside the chamber. Recently there have been some new techniques developed such as double-pass infrared transmission and multi wavelength imaging pyrometer [25].

**Figure 2.3:** Furnace bell jar method, Emissivity corrected pyrometer uses reflectometers with in-situ chopped light and ex-situ integrating sphere [26].

#### 2.1.4.2 Furnace Annealing

A bell jar furnace method for annealing implant monitors was developed at High Temperature engineering and improved with an emissivity compensating temperature measurement scheme [26]. Figure 2.3 shows a rough schematic. The wafer, on a support platform, is elevated into a heated zone with a vertical temperature gradient. The maximum temperature at the top of the bell-jar is set to be about 200°C above that of the desired process temperature. The comparatively weak sensitivity of wafer temperature to wafer emissivity within the near blackbody environment at high temperature has made this a viable method for open loop operation in some production.

Elevator motion is sufficiently fast to produce thermal spiking with 0.5 sec dwell time within 2°C of peak temperature. Under closed loop temperature control with

pyrometer focused on the backside of the wafer, some of the best results for process reproducibility and uniformity have been claimed. The pyrometer for the bell jar method detects the thermal energy flux emitted by the wafer and measures the emissivity of the wafer. Emissivity,  $E$  is defined for practical purposes as the ratio of thermal emission received from the wafer relative to that of a blackbody at the same temperature [27]. The operating wavelength of the pyrometer about  $0.95 \mu\text{m}$  is above (in energy) the Si band gap [21], where optical transmission through the wafer can be neglected [21]. An expression derived from energy conservation and the Kirchoff's law, which reduces to  $E=1-R$ , is used to compute emissivity from a separate measurement of reflectivity,  $R$ . The reflectivity is determined by mapping geometrical and background reflection factors as a function of elevator height and then normalizing bi-directional reflection signals to separate existed precision measurement of  $R$  at room temperature using hemispherical illumination. Wafer temperature is then computed from the Planck radiation law and a gauge factor for the detector sensitivity.

### **2.1.5 Theory of Electrical Characterization Technique**

The following three techniques were used for the electrical characterization of our samples. In the following, brief introduction of these techniques is described.

#### **2.1.5.1 Hall Measurement Technique**

Hall Effect measurements are used in many phases of the electronics industry, from basic materials research and device development to device manufacturing [29]. A Hall Effect measurement system can actually be used to determine quite a few material parameters, but the primary one is the Hall voltage ( $V_H$ ). Other important parameters such as carrier mobility, carrier concentration ( $n$ ), Hall coefficient ( $R_H$ ), resistivity, magneto- resistance ( $R$ ), and the conductivity type (N or P) are all derived from the Hall voltage measurement [28, 29, 30]. With the addition of some other instruments, I-V characterization curves can be created with a similar test setup. Hall Effect measurements are useful for characterizing virtually every material used in producing semiconductors, such as silicon (Si) and germanium (Ge), as well as most compound semiconductor materials. They are equally useful for characterizing both low resistance

materials and high resistance semiconductor materials, including semi-insulating GaAs, gallium nitride (GaN), and cadmium telluride (CdTe) [29].

#### **2.1.5.1.1 History of Hall Effect**

The history of the Hall Effect begins in 1879 when Edwin H. Hall was working on his doctoral degree at Johns Hopkins University in Baltimore, Maryland discovered that if a thin gold plate is placed in a magnetic field, which is at right angles to its surface, an electric current flowing along the plate can cause a potential drop at right angles both to the current and the magnetic field termed the Hall Effect [30]. In order to determine both the mobility and the active dose, both resistivity measurements, similar to 4PP, and Hall measurements are needed. The Van der Pauw technique is widely used in the semiconductor industry to determine the resistivity of uniform samples and is used in this work. The Hall Effect can also be used to determine the carrier type (electrons or holes). The primary drawback to Hall Effect is the difficulty of forming ohmic contacts on high resistivity samples such as those with very low dopant concentrations. It is also highly sensitive to electrical defects [29].

#### **2.1.5.1.2 The Hall Effect and the Lorentz Force**

The basic physical principle underlying the Hall Effect is the Lorentz force. When an electron moves along a direction perpendicular to an applied magnetic field, it experiences a force acting normal to both directions and moves in response to the force and the force affected by the internal electric field [31]. For an *n*-type, bar-shaped semiconductor as is shown in figure 2.4, the carriers are predominately electrons of bulk density, *n*. It is assumed that a flow of current, *I* was along the x-axis from left to right in the presence of a z-directed magnetic field. Electrons subject to the Lorentz force initially they drift away from the current line toward the negative y-axis, resulting in an excess surface electrical charge on the side of the sample. This charge results produced the potential drop across the two sides of the sample (Note that the force on holes is toward the same side because of their opposite velocity and positive charge). This transverse voltage is the Hall voltage  $V_H$  and its magnitude is equal to  $IB/qnd$ .

where,  $I$  is the current,  $B$  is the magnetic field,  $d$  is the sample thickness, and  $q$  ( $1.602 \times 10^{-19}$  C) is the elementary charge.

**Figure 2.4:** Schematic of the Hall Effect in a long, thin bar of a semiconductor with four ohmic contacts. The direction of the magnetic field  $B$  is along axis and the sample has a finite thickness,  $d$ .

In some cases, it is convenient to use layer or sheet density ( $n_s = nd$ ) instead of bulk density:-

$$n_s = IB/q|V_H| \quad (2.3)$$

Thus, by measuring the Hall voltage,  $V_H$  and from the known values of  $I$ ,  $B$ , and  $q$ , we can determine the sheet density,  $n_s$  of charge carriers in semiconductors. The Hall voltage is negative for n-type semiconductors and positive for p-type semiconductors. The sheet resistance,  $R_s$  of the semiconductor can be conveniently determined by use of the van der Pauw resistivity measurement technique. Since sheet resistance involves both sheet density and mobility, we can determine the Hall mobility from the equations:-

$$\mu = |V_H|/R_s IB = 1/(q n_s R_s) \quad (2.4)$$

$$\mu = R_H R_s \quad (2.5)$$

If the conducting layer thickness  $d$  is known, we can determine the bulk resistivity ( $\rho = R_s d$ ) and the bulk density ( $n = n_s/d$ ) [32].

### 2.1.5.1.3 The van der Pauw Technique

Traditionally four point probe (4PP) is considered as standard measurements tool for resistivity characterization, however this technique provides no means of decoupling the effects of mobility enhancement and carrier density increase. Van der Pauw sheet resistance measurements were used as they avoid the penetration issues associated with the 4PP technique. In a 4PP measurement, the efficacy of the probe contacts is assured by weighting the probe arm. This results in penetration of the probe tips into the sample. As a result of the ultra-shallow nature of the implant profiles being investigated, this penetration can result in large errors in the measured sheet resistances. Van der Pauw measurements proceed through deposited ohmic contacts rather than weighted mechanical contacts, thus avoiding these errors.

So in order to determine both the mobility,  $\mu$  and the sheet density,  $n_s$  a combination of a resistivity measurement and Hall measurement is needed. The Van der Pauw technique, due to its convenience, is widely used in the semiconductor industry to determine the resistivity of uniform samples. The objective of the resistivity measurement is to determine the sheet resistance,  $R_s$ . Van der Pauw demonstrated that there are actually two characteristic resistances  $R_A$  and  $R_B$ , associated with the corresponding terminals shown in figure 2.5  $R_A$  and  $R_B$  are related to the sheet resistance,  $R_s$  through the Van der Pauw equation [33]. The bulk electrical resistivity  $\rho$  can be calculated as in equation 2.6:-

$$\rho = R_{sd}. \quad (2.6)$$

The objective of the Hall measurement in the Van der Pauw technique is to determine the sheet carrier density,  $n_s$  by measuring the Hall voltage,  $V_H$ . The Hall voltage measurement consists of a series of voltage measurements with a constant current,  $I$  and a constant magnetic field,  $B$  applied perpendicular to the plane of the sample. Once the Hall voltage  $V_H$  is acquired, the sheet carrier density,  $n_s$  can be calculated via  $n_s = IB/q|V_H|$  from the known values of  $I$ ,  $B$ , and  $q$  [34].

**Figure 2.5:** Schematic of the Van der Pauw configuration used in the determination of the two characteristic resistances  $R_A$  and  $R_B$ .

#### 2.1.5.2 Semiconductor Characterization System Keithley Model 4200

Electrical characterization is important in determining how much the junction is efficient and behaves in different annealing regime. Keithley Model 4200-SCS Semiconductor Characterization System is able to simply test and analyze critical electrical measurements [34]. The Model 4200-SCS is well-suited for performing a wide range of measurements, including DC and pulsed current-voltage (I-V), capacitance-voltage (C-V) and capacitance-frequency (C-f) because it is an integrated system that includes instruments for making DC and ultra-fast I-V and C-V measurements, as well as control software, graphics, and mathematical analysis. Keithley's Model 4200-CVU instrument comes as a module that plugs into any available instrument slot of the Model 4200-SCS Semiconductor Characterization System, allowing fast and easy capacitance measurements from femto-Farads to nano-Farads, at frequencies from 10 kHz to 10 MHz. Developed with the most modern and high performance circuitry available, the Model 4200-CVU design provides intuitive point-and-click setup, simple cabling, and built-in element models that eliminate the guesswork in obtaining valid C-V measurements. Good for advanced CMOS pulse I-V testing and high speed single pulse charge trapping [35].

**2.1.5.3 CV System**

Electrical measurements have also been performed on a Material Development Corporation (MDC) Probe Station equipped with a Keithley 237 voltage source/picoammeter and an Agilent 4980A precision LCR meter. This set-up is computer controlled by the MDC software package CSM/Win Quiet CHUCK. The CV plotting system is customized with the above mentioned MDC mercury probe, hot-chuck and with a capacitance–voltage meter that performs measurements using a low frequency measurement method as shown in figure 4.4. The CV-plotting system includes components such as an output device, memory (random access memory, read only memory, a hard disk drive), and a processor or CPU. The processor is in communication with the memory, capacitance–voltage meter and out-put device. Any desired output devices can be employed in the CV plotting system (printer, digital plotters and network devices) to report, store, graph or transfer the measurement data. The capacitance voltage meter has two electrodes or terminals for connection to a probe, a force electrode or terminal and a sense electrode or terminal. These electrodes are connected to a probe station which acts on a semiconductor wafer to obtain electrical measurements. One of the electrodes is connected to an area that is much larger than the area of the mercury tip and faces semiconductor wafer. Then capacitance voltage measurement is taken by using low frequency measurement method and quasi static measurement method. In this work MDC /CSM is chosen because we can get high resolution at the probe tip (DC biasing down to millivolts and capacitance measurement down to femto-farads) and can measure Low capacitance (pico-farad and smaller values) [37, 38].

**2.1.6 Ellipsometry**

According to J. A. Woolam 2008 Spectroscopic Ellipsometry (SE) is unconventional but one of best non-contact, non-destructive tool to study the optical properties [39, 40]. Spectroscopic Ellipsometry (SE) is traditionally used in the Ultra-Violet, visible and near IR wavelength region (250–1850 nm) for the measurement of layer thicknesses (from sub-nanometer thickness up to tens of microns and the optical properties from transparent to absorbing materials), refractive indices and carrier concentrations [39, 41, 42].