**Architecture and Simulation of

Very Long Instruction Word

Reconfigurable Instruction Set Processor

(VLIW-RISP)**

*Submitted by*

Uzma Saeed

275-FAS/MS/CS/F05

*Supervised by*

M. Aqeel Iqbal

and

Asim Munir

**Department of Computer Science,

Faculty of Applied Sciences,

International Islamic University,

Islamabad**

*IN

THE

NAME

OF ALLAH

THE MOST BENIFICIENT

AND THE MOST MERCIFUL*

**Department of Computer Science

International Islamic University

Islamabad**

Date of External 25<sup>th</sup> August, 2009

**FINAL APPROVAL**

It is certified that we have read the project report submitted by Ms. Uzma Saeed reg. no 275-FAS/MS/CS/F05 and that this project is of sufficient standard to warrant its acceptance by International Islamic University, Islamabad for the Masters of Science in Computer Sciences.

**COMMITTEE**

**External Examiner**

Dr. Abdul Sattar

Director General (Ret.)

Pakistan Computer Bureau

**Internal Examiner**

Mr. Muhammad Nadeem

Assistant Professor,

International Islamic University,

Islamabad

**External Supervisor**

Mr. M. Aqeel Iqbal

Assistant Professor,

Fauji Foundation University,

Rawalpindi

**Internal Supervisor**

Mr. Asim Munir

Assistant Professor,

International Islamic University,

Islamabad

## **ACKNOWLEDGEMENT**

First of all I would like to sincerely thank my supervisors Mr. M. Aqeel Iqbal and Mr. Asim Munir for giving me this wonderful opportunity to work on this project under their kind supervision and guidance throughout the project. I do acknowledge their true coordination and support.

Then at last but not the least, I would like to thank my dear parents for their moral and all kind of support during this project. I never forget their help during the tough times of the project.

Thank you all again!

**Uzma Saeed**

**275-FAS/MS/CS/F05**

## **DECLARATION**

All sentences or passages quoted in this report, or computer code of any form whatsoever used and/or submitted at any stages, which are taken from other people's work have been specifically acknowledged by clear citation of the source, specifying author, work, date and page(s). Any part of my own written work, or software coding, which is substantially based upon other people's work, is duly accompanied by clear citation of the source, specifying author, work, date and page(s). I understand that failure to do this amount to plagiarism and will be considered grounds for failure in this module and the degree examination as a whole.

**Uzma Saeed**

**275-FAS/MS/CS/F05**

# Table of Contents

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| Chapter No.1 .....                                                               | 3  |

| INTRODUCTION .....                                                               |    |

| 1.1 RC Architecture .....                                                        |    |

| 1.2 Motivation.....                                                              | 8  |

| Chapter No.2 .....                                                               | 9  |

| Literature Review.....                                                           | 9  |

| 2.1 Classification.....                                                          | 9  |

| 2.1.1 Granularity .....                                                          | 9  |

| 2.1.2 Host Coupling .....                                                        | 9  |

| 2.1.3 Reconfiguration Methodology .....                                          | 11 |

| 2.1.4 Memory Organization.....                                                   | 11 |

| 2.2 Reconfigurable Computing Architecture; A Survey.....                         | 12 |

| 2.4 Related Work.....                                                            | 12 |

| 2.4.1 Coupling of a Reconfigurable Architecture and a Multithreaded Processor    |    |

| Core with Integrated Real-Time Scheduling.....                                   | 12 |

| 2.4.2 Introduction to Reconfigurable Computing.....                              | 12 |

| 2.4.3 Reconfigurable Instruction Set Processors from a Hardware/Software         |    |

| Perspective.....                                                                 | 13 |

| 2.4.4 Reconfigurable VLIW Processor for Streaming Data.....                      | 13 |

| 2.4.5 Reconfigurable Computing Systems Design: Issues at System-Level            |    |

| Architecture.....                                                                | 15 |

| 2.4.6 Intelligence Reconfigurable Instruction Set Processor (I-RISP) Design..... | 16 |

| Chapter No.3 .....                                                               | 18 |

| Dedicated Machines and Reconfigurable Computing .....                            | 18 |

| 3.1 The Philosophy of a dedicated machine .....                                  | 18 |

| 3.1.1 The Main Theme Behind Instruction Set Specialization .....                 | 18 |

| 3.2 FPGAs.....                                                                   | 19 |

| 3.2.1 The Basic FPGA Architecture.....                                           | 22 |

| 3.2.2 FPGA Technology .....                                                      | 26 |

| 3.2.4 Commercial FPGAs .....                                                     | 27 |

| 3.2.5 FPGA Performances .....                                                    | 28 |

| 3.3 Reconfigurable CPUs.....                                                     | 29 |

| 3.3.1 Totally reconfigurable processors.....                                     | 29 |

| 3.3.2 The coprocessor Approach .....                                             | 30 |

| 3.3.3 A Partially reconfigurable CPU.....                                        | 30 |

| Chapter No.4 .....                                                               | 32 |

| The Proposed Architecture.....                                                   | 32 |

| 4.1 Overall Design Goal .....                                                    | 32 |

| Module No.1 (Compiler Design for VLIW-RISP) .....                                | 32 |

| Module No.2 (VLIW-RISP Design using Verilog-HDL).....                            | 32 |

| 4.2 Tool Issues .....                                                            | 32 |

| 4.2.1. Importance of HDLs .....                                                  | 33 |

| 4.2.2. Why not to use a general purpose language.....                            | 33 |

| 4.2.3. Verilog-HDL.....                                                          | 33 |

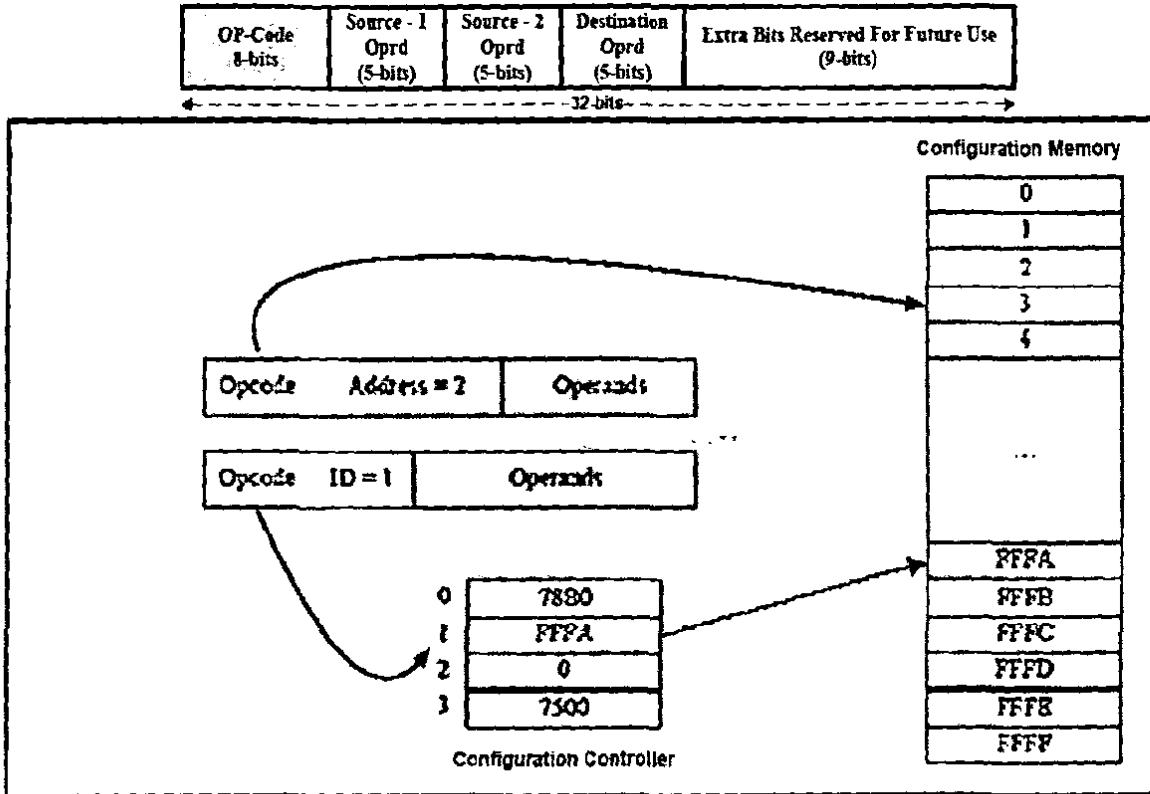

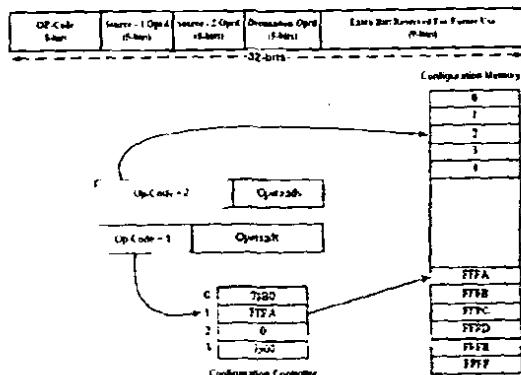

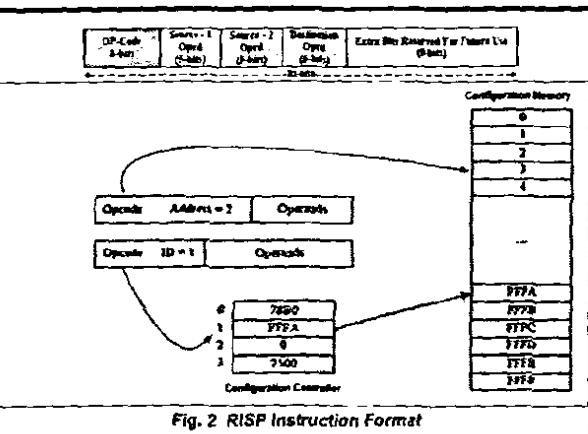

| 4.3 Instruction Format of proposed VLIW-RISP .....                               | 35 |

| 4.4 VLIW-RISP Design Simulation using Verilog-HDL .....                          | 36 |

|                                                      |    |

|------------------------------------------------------|----|

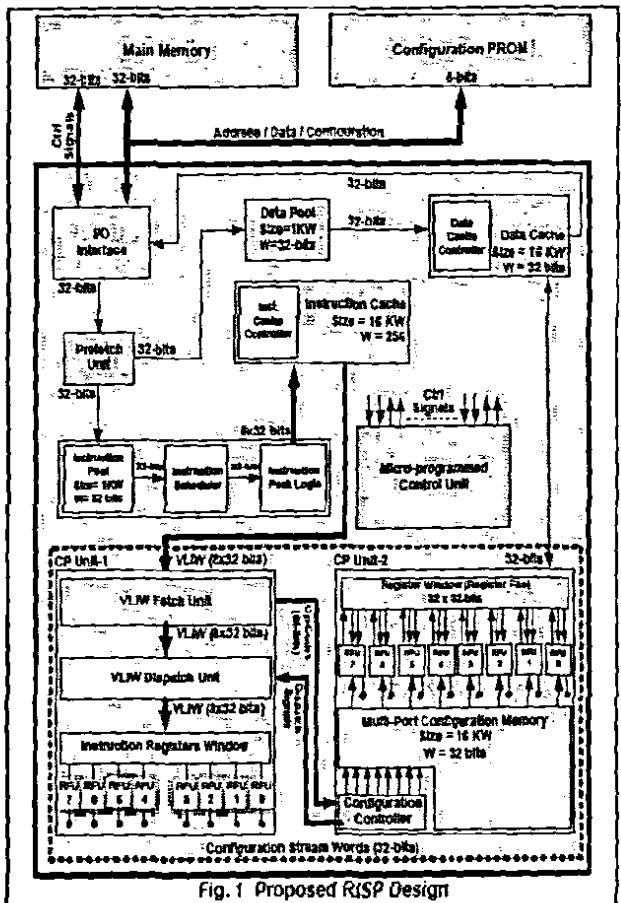

| 4.5 PROPOSED RISP DESIGN:.....                       | 36 |

| 4.5.1 Input / Output Interface (IO Interface): ..... | 39 |

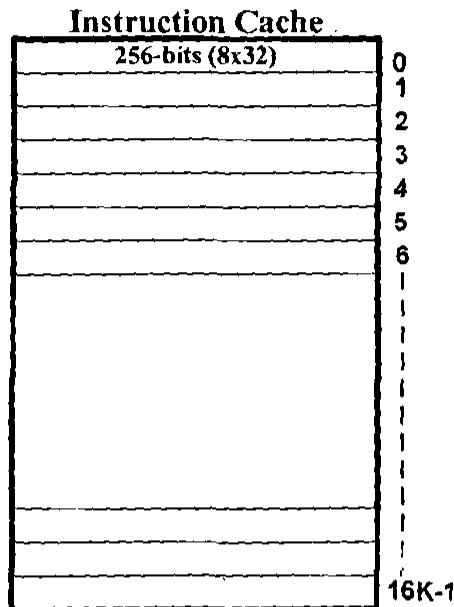

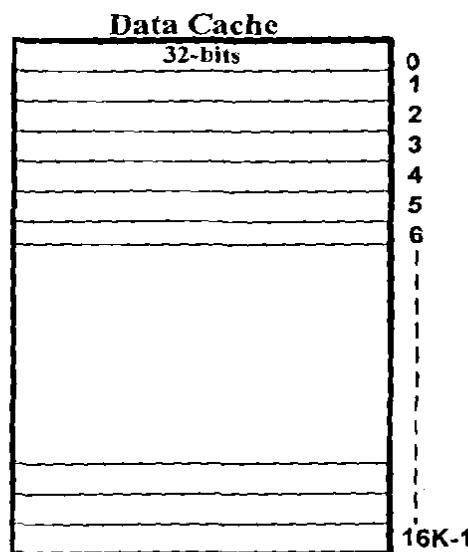

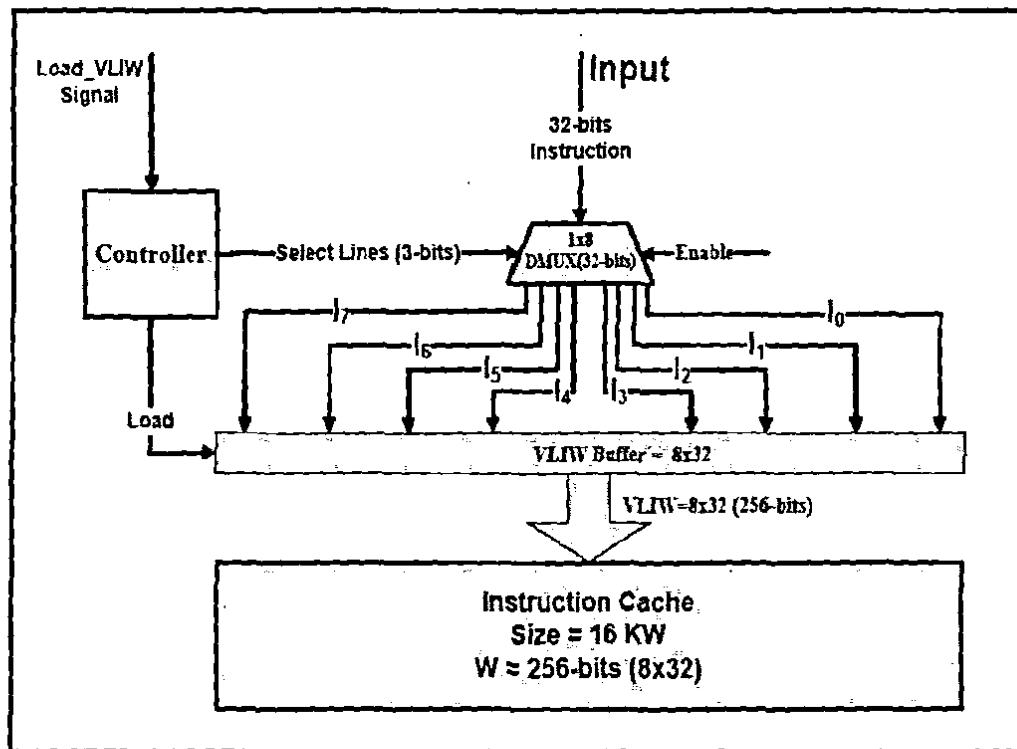

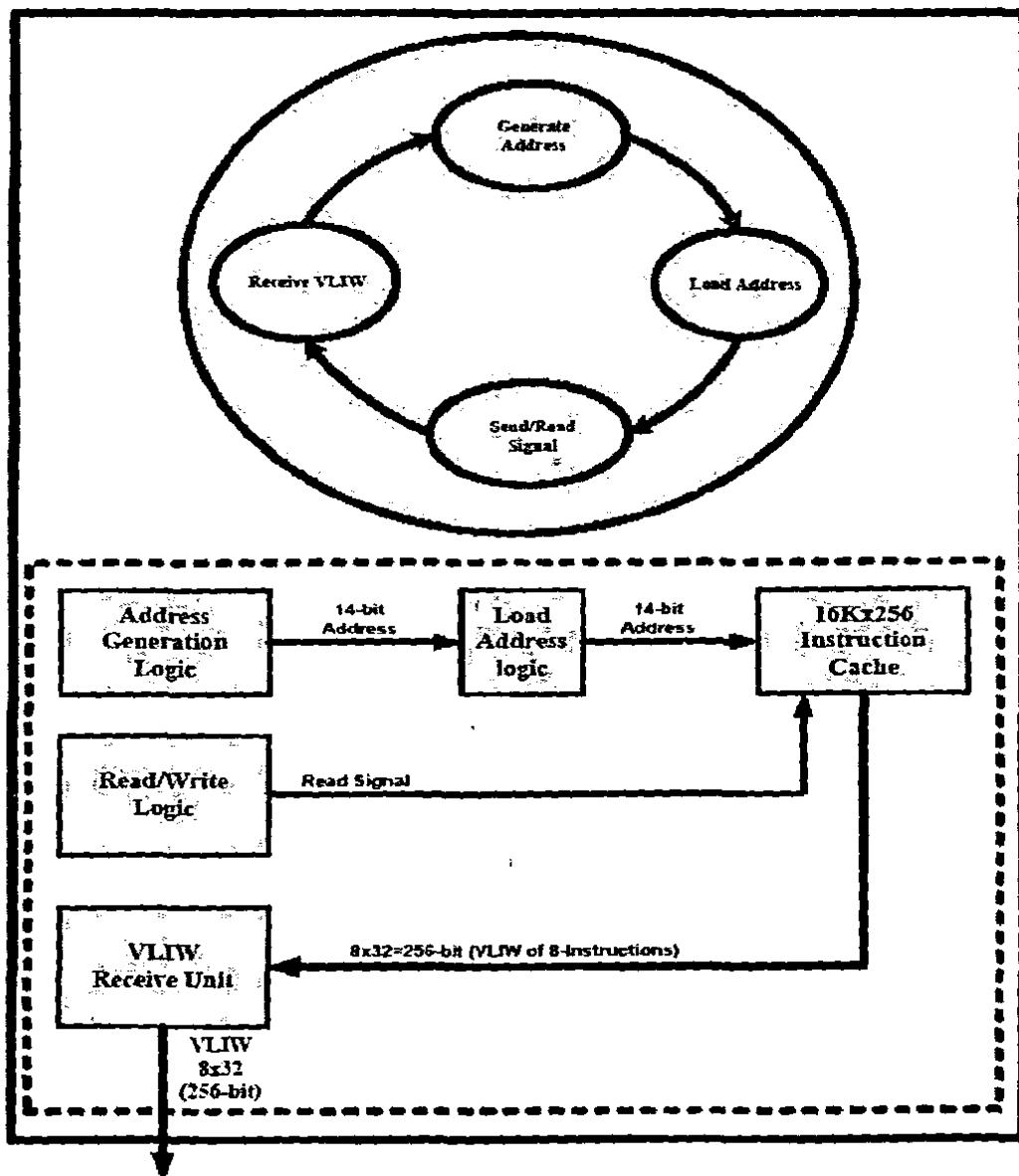

| 4.5.2 Cache Memories .....                           | 40 |

| 4.5.3 Pre-fetch Unit (PFU):.....                     | 41 |

| 4.5.4 Instruction Scheduler Unit (ISU).....          | 43 |

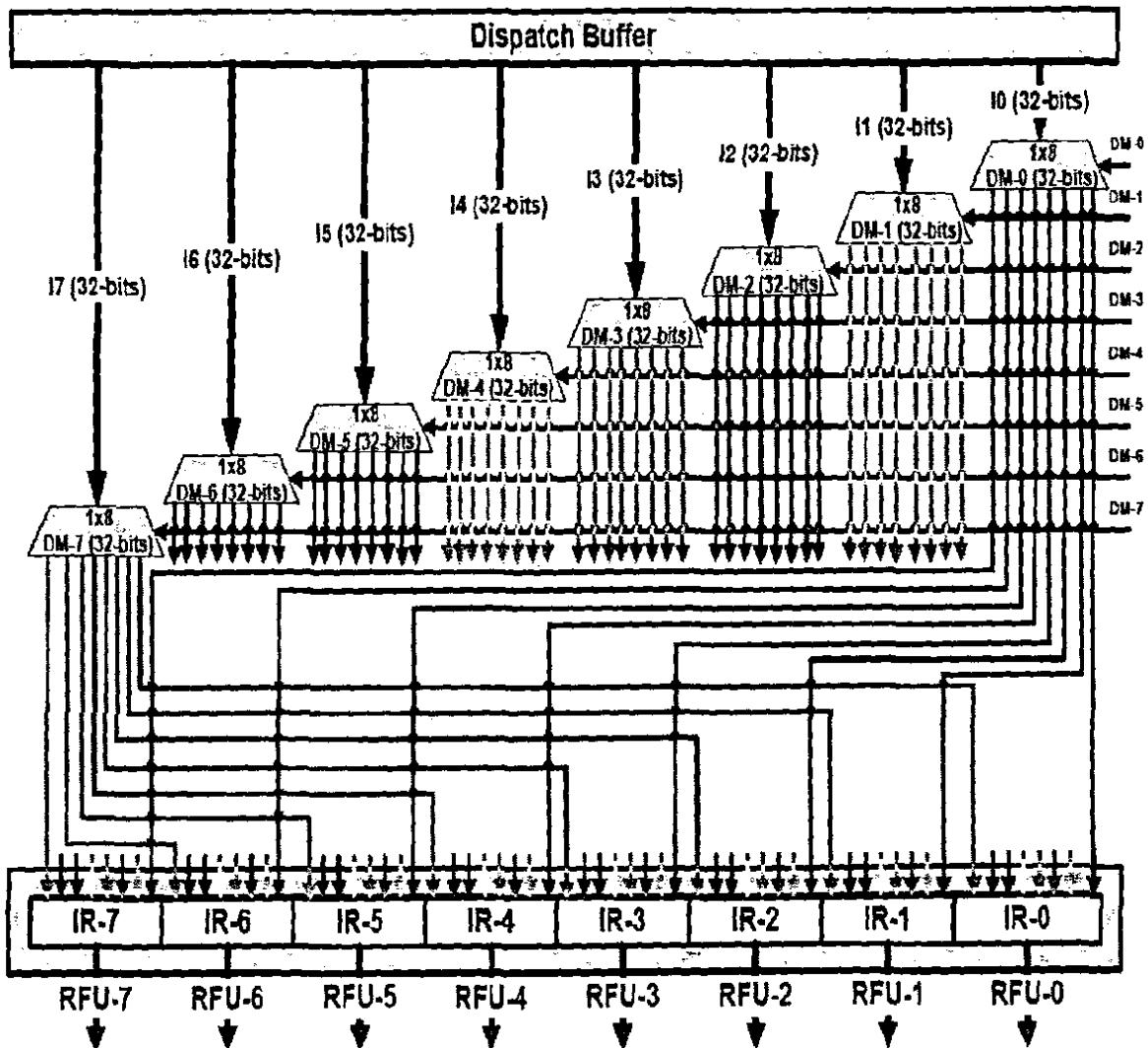

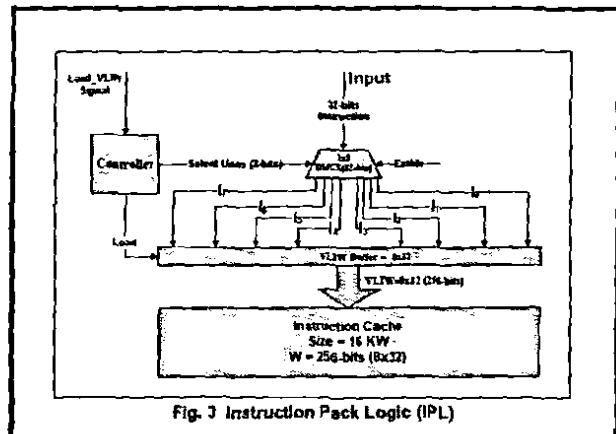

| 4.5.5 Instruction Pack Logic (IPL) .....             | 43 |

| 4.5.6 Computational Pipeline-1 (CP-1) .....          | 44 |

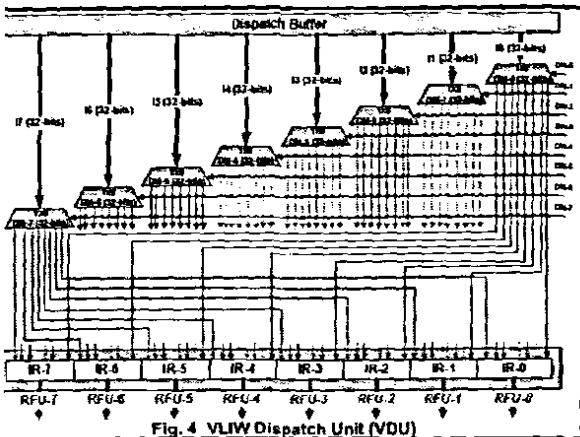

| 4.5.7 Computational Pipeline-2 (CP-2) .....          | 45 |

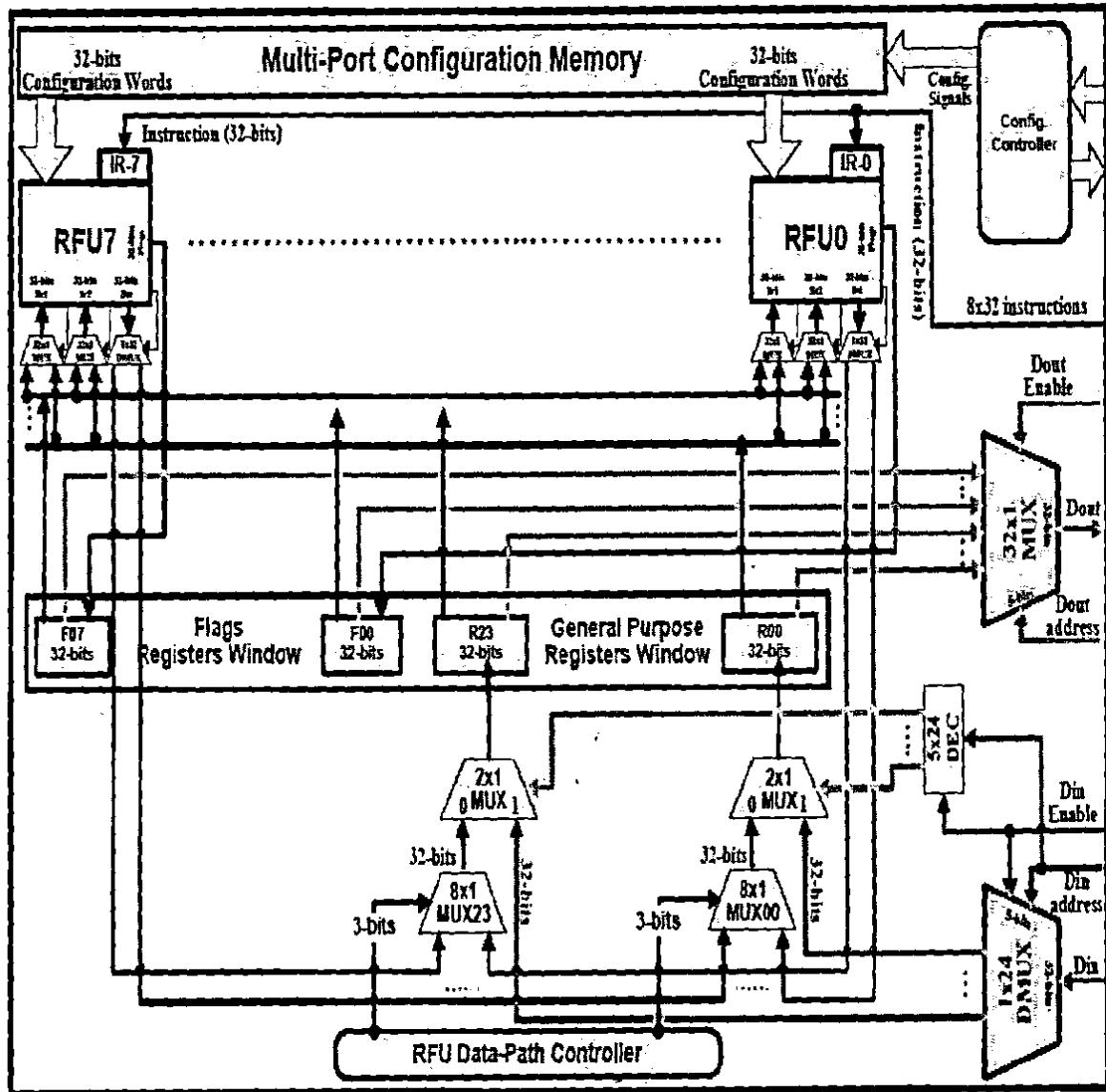

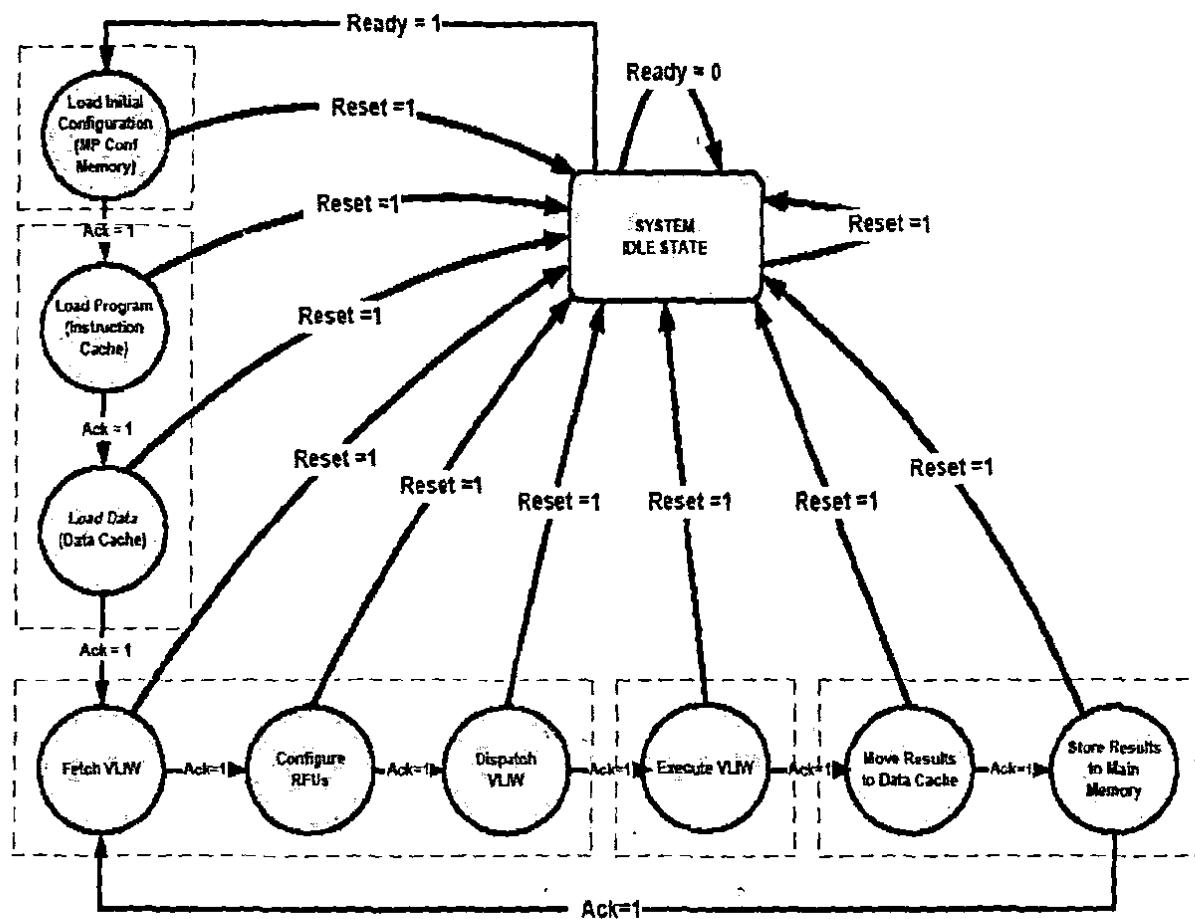

| 4.5.8 Micro-programmed Control Unit (MCU).....       | 54 |

| Chapter No.5 .....                                   | 57 |

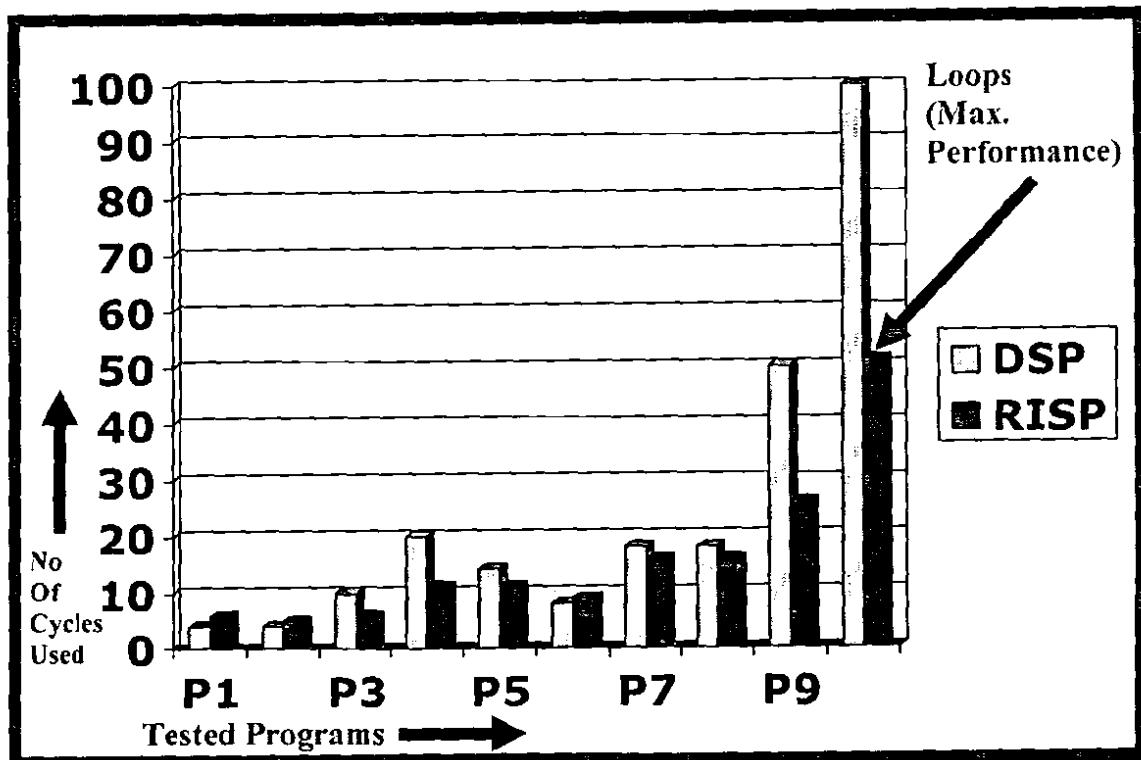

| Statistics and Performance Analysis.....             | 57 |

| 5.1 DSP (TMS320C6X) Statistics [46].....             | 57 |

| 5.2 VLIW-RISP Statistics.....                        | 58 |

| 5.3 DSP vs VLIW-RISP Performance Analysis.....       | 71 |

| Chapter No.6 .....                                   | 72 |

| Conclusion and Future Work.....                      | 72 |

| 6.1 Conclusion .....                                 | 72 |

| 6.2 Future Work .....                                | 73 |

| 6.2.1 Hardware Improvement .....                     | 73 |

| 6.2.2 Configuration Protocol.....                    | 73 |

| 6.2.3 Configuration Techniques.....                  | 73 |

| Bibliography .....                                   | 74 |

| Appendix.....                                        | 78 |

## Table of Figures

|                                                                         |    |

|-------------------------------------------------------------------------|----|

| Figure 1.1 Reconfigurable Computing System.....                         | 07 |

| Figure 2.1 Host Coupling Approaches .....                               | 10 |

| Figure 2.2 Generating the FPGA code.....                                | 15 |

| Figure 3.1 Typical FPGA Board, Device and Logic block architecture..... | 21 |

| Figure 3.2 A Generic FPGA Architecture .....                            | 22 |

| Figure 3.3 A Generic Programmable Logic Block .....                     | 23 |

| Figure 3.4 Three-Input Look-Up Table .....                              | 24 |

| Figure 3.5 Basic Programmable Switch Types.....                         | 25 |

| Figure 3.6 I/O Block Architecture .....                                 | 25 |

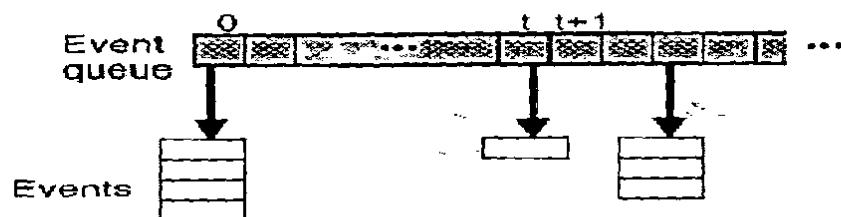

| Figure 4.1 Event driven Systems .....                                   | 34 |

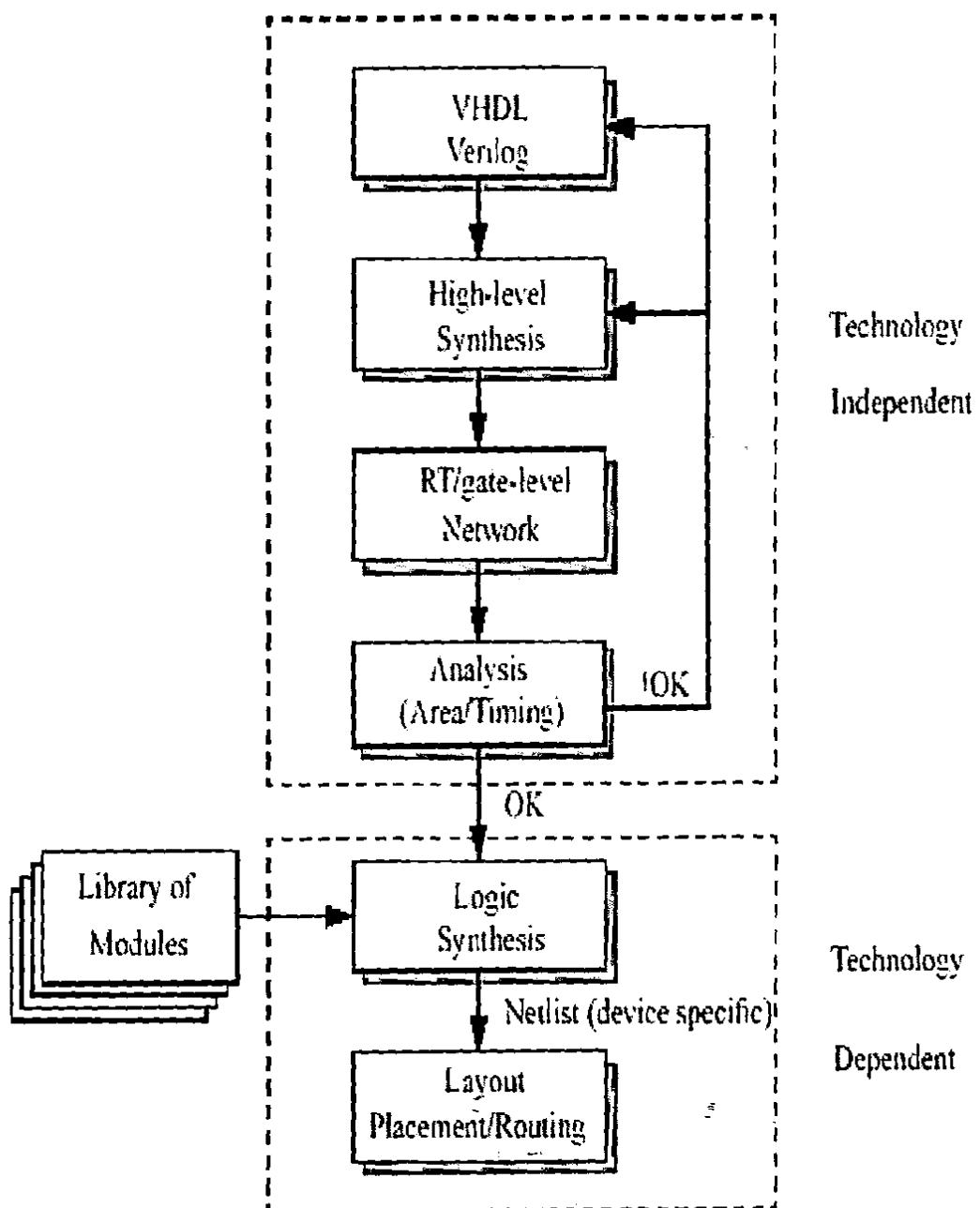

| Figure 4.2 Design Flow Using Verilog-HDL .....                          | 34 |

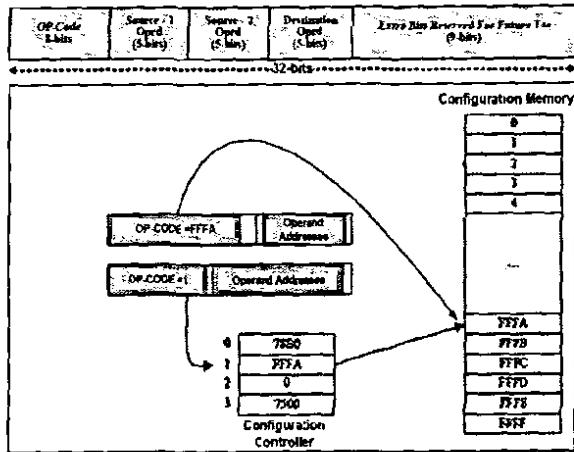

| Figure 4.3 Op-Code Interpretation.....                                  | 35 |

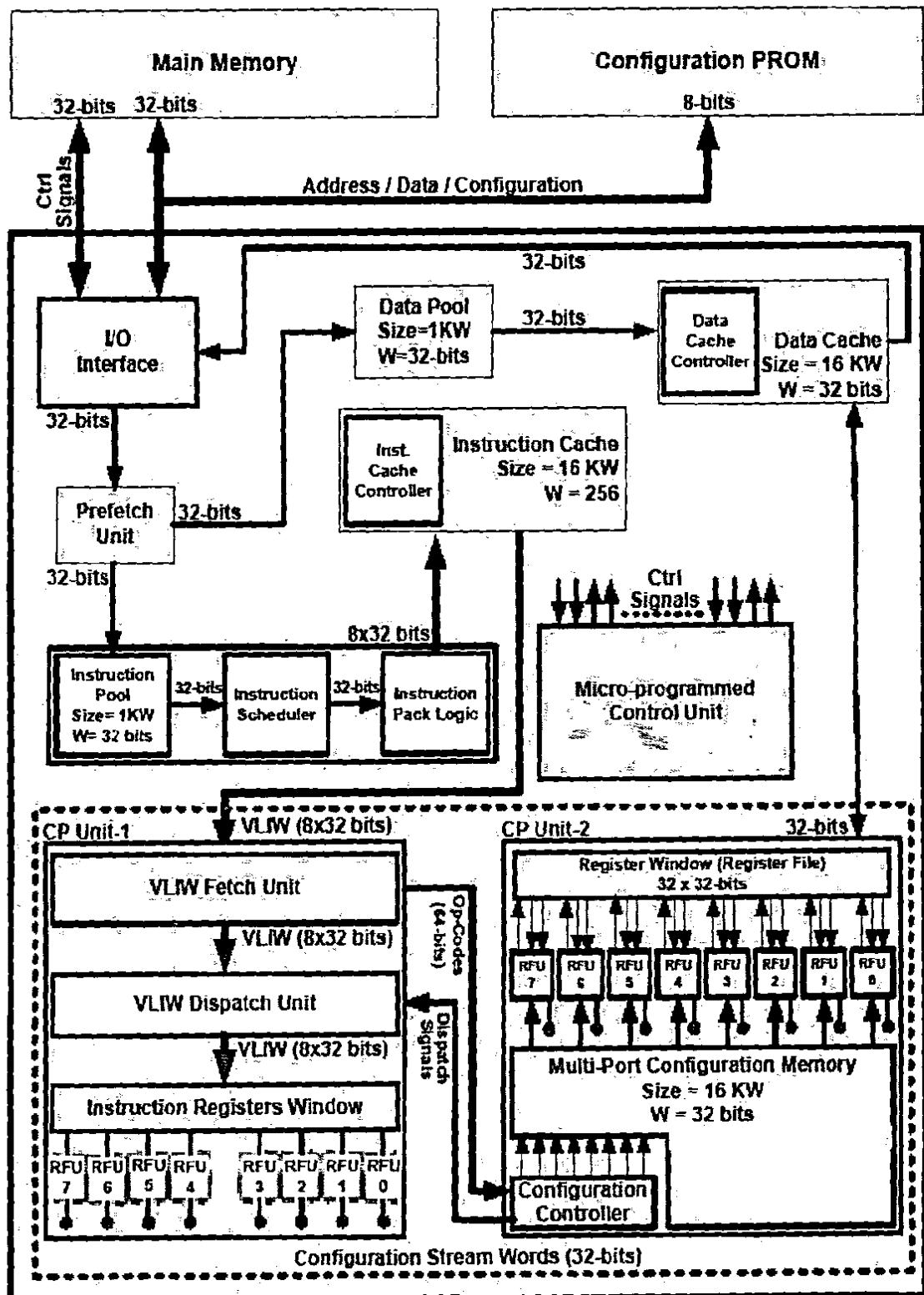

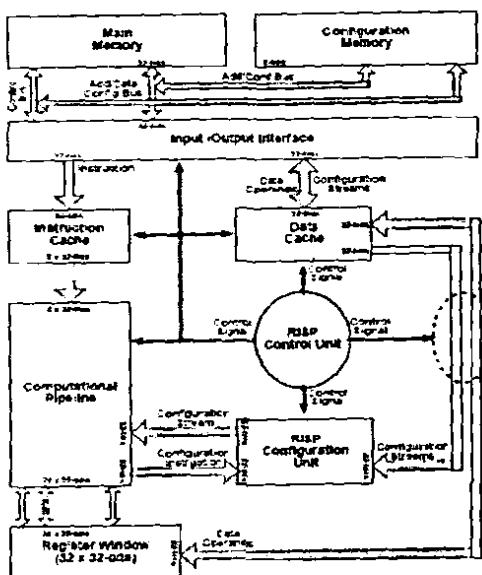

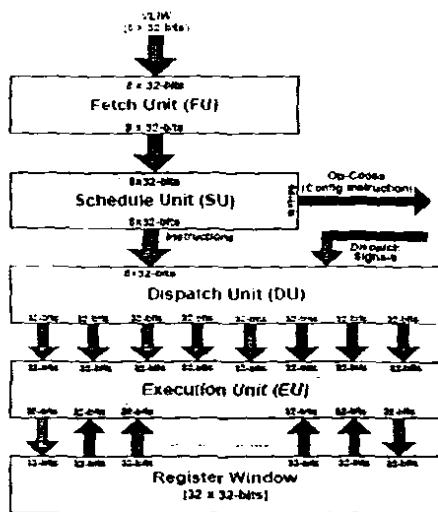

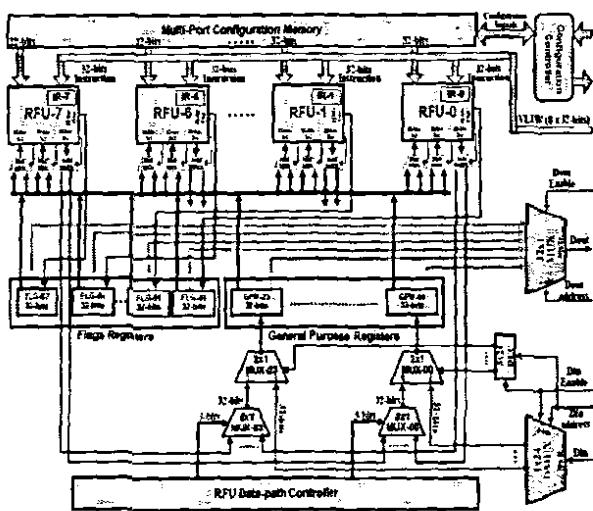

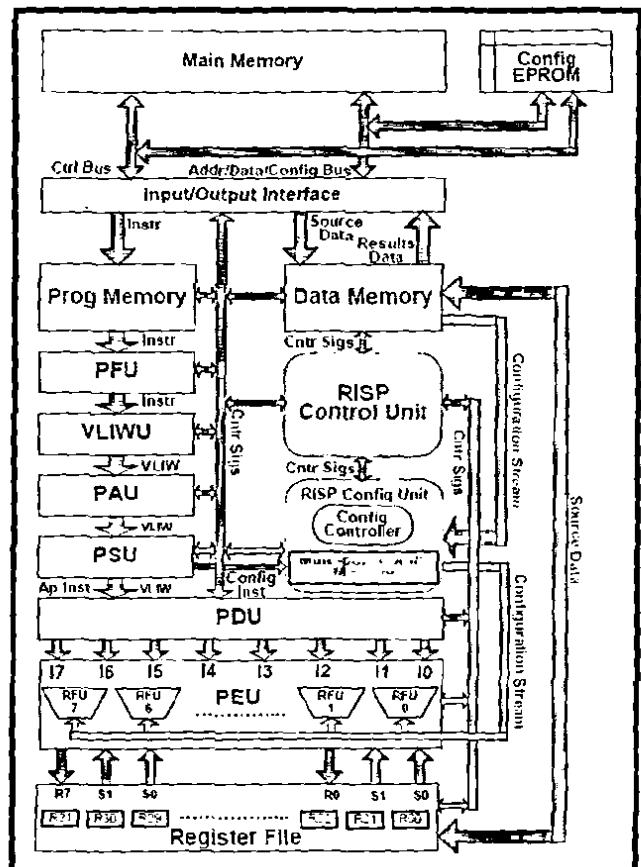

| Figure 4.4 Proposed VLIW-RISP Design.....                               | 38 |

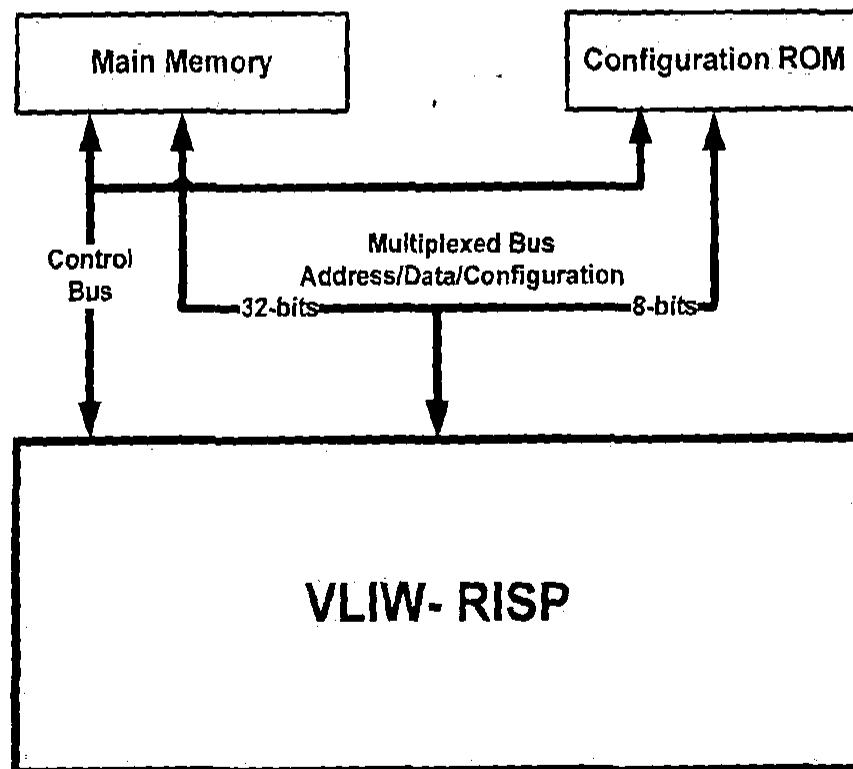

| Figure 4.5 External Interface .....                                     | 39 |

| Figure 4.6 Instruction Cache.....                                       | 41 |

| Figure 4.7 Data Cache.....                                              | 42 |

| Figure 4.8 Instruction Pack Logic.....                                  | 43 |

| Figure 4.9 VLIW Fetch Unit.....                                         | 44 |

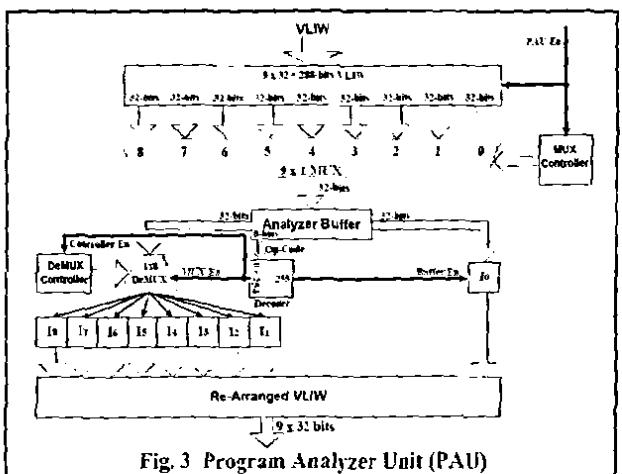

| Figure 4.10 VLIW Dispatch Unit .....                                    | 45 |

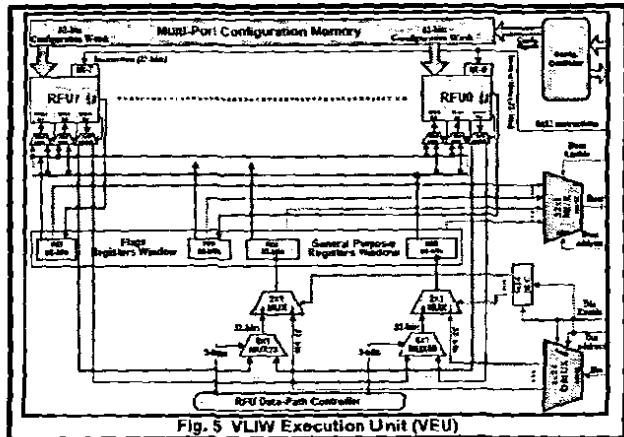

| Figure 4.11 VLIW Execution Unit .....                                   | 46 |

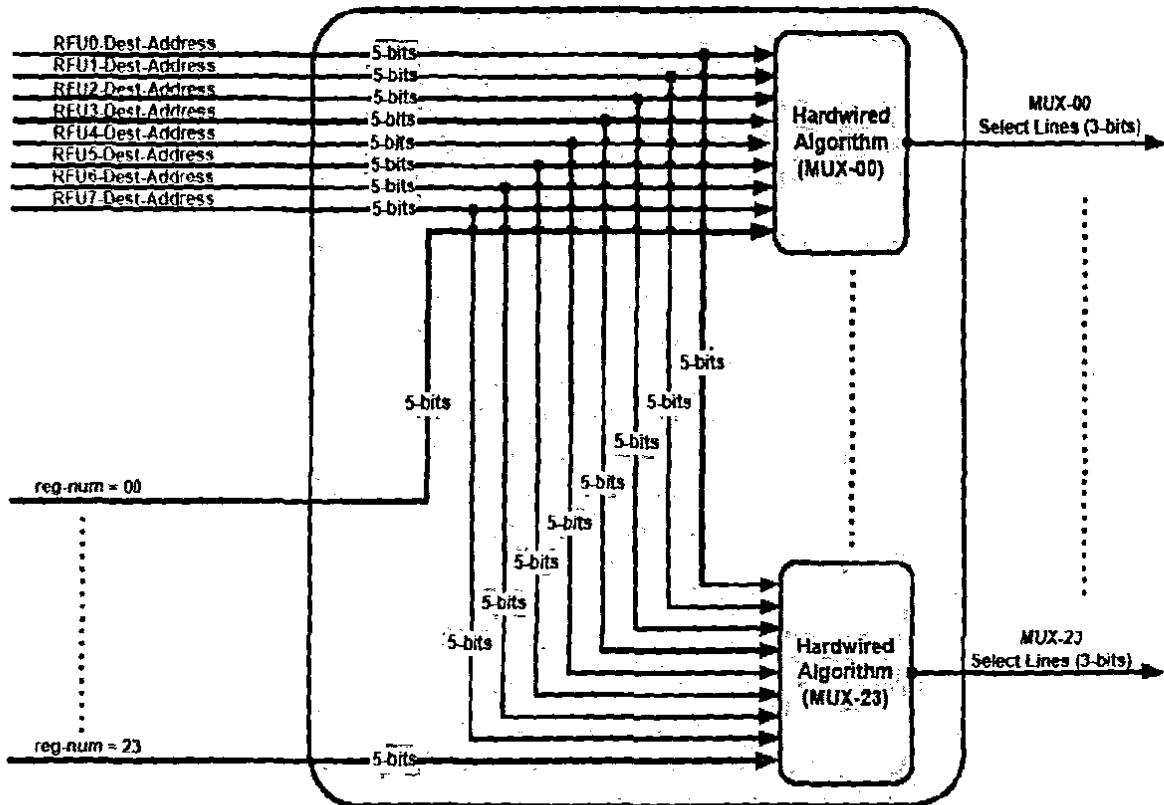

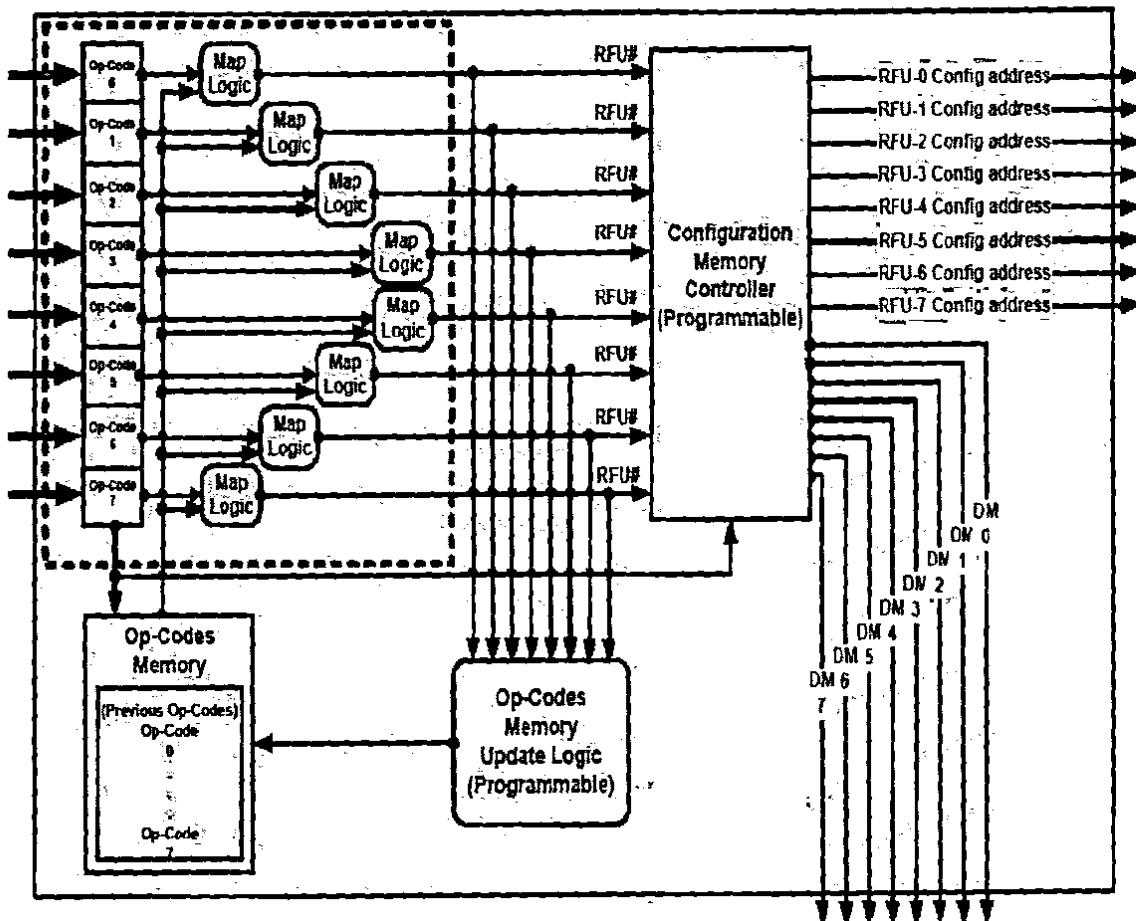

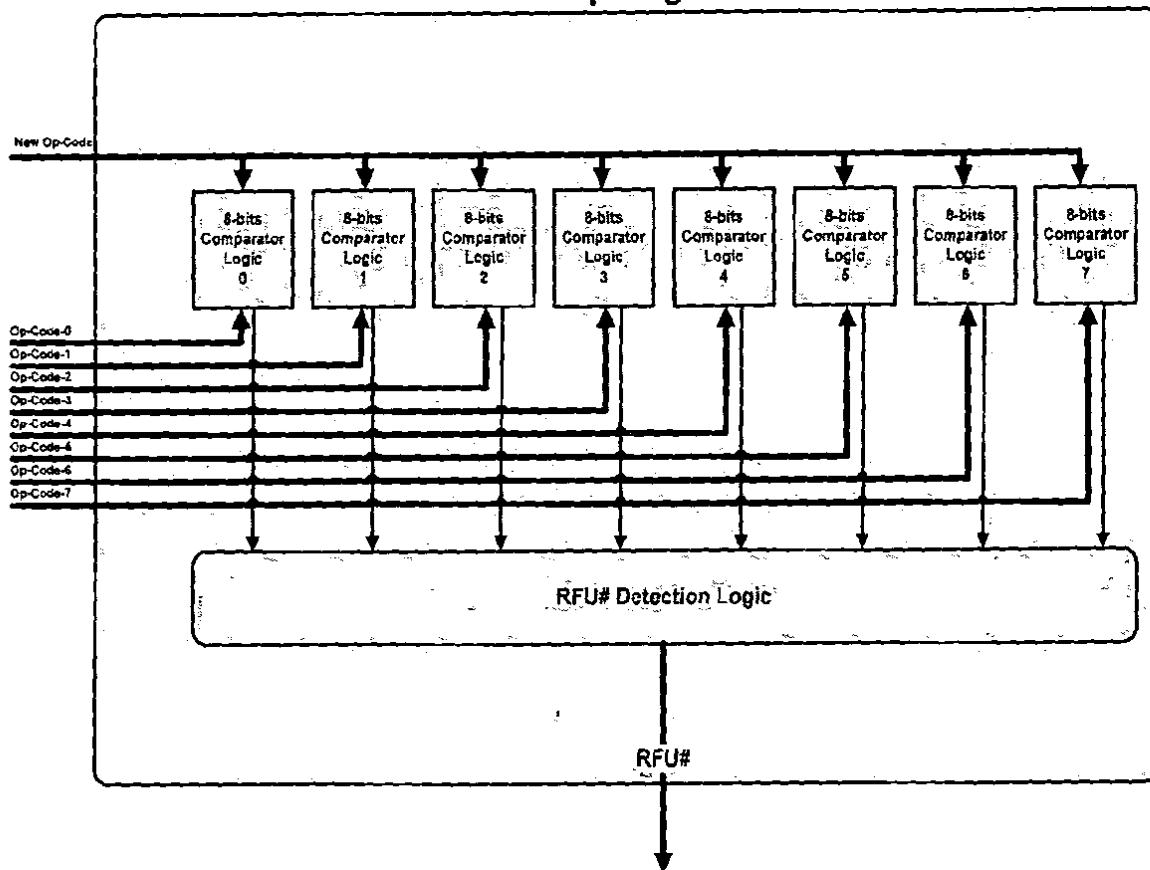

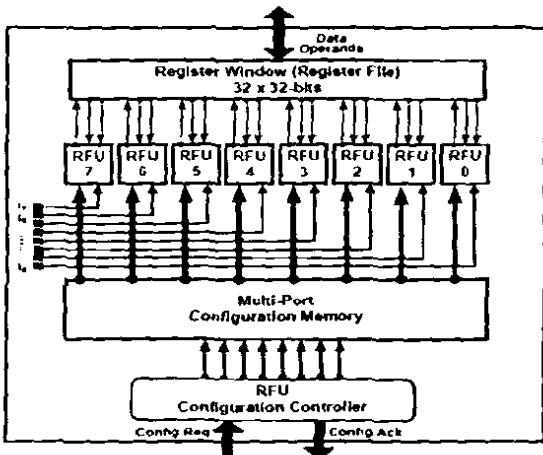

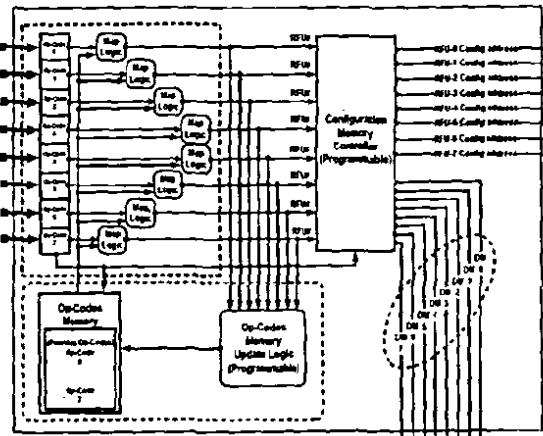

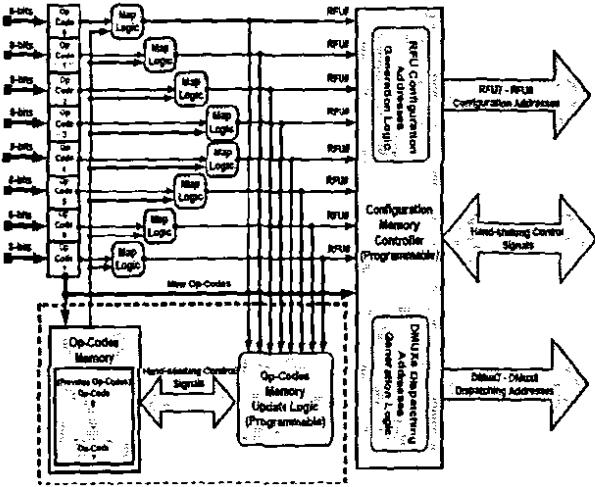

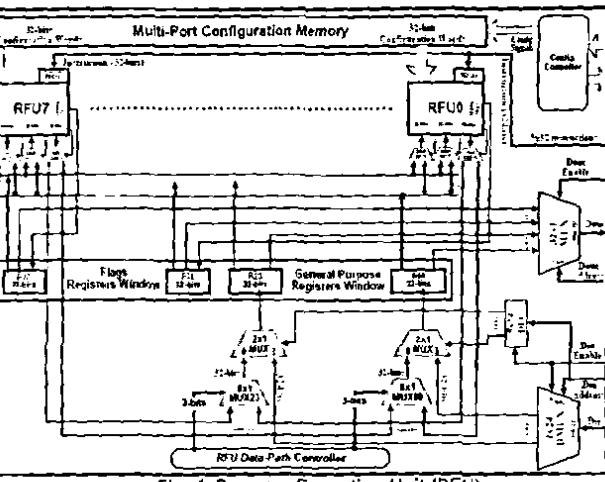

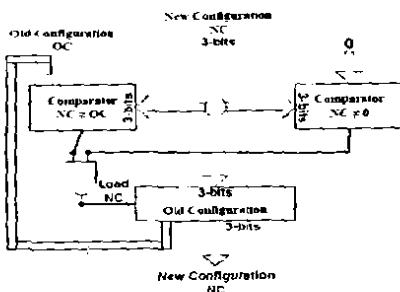

| Figure 4.12 RFU Data Path Controller .....                              | 48 |

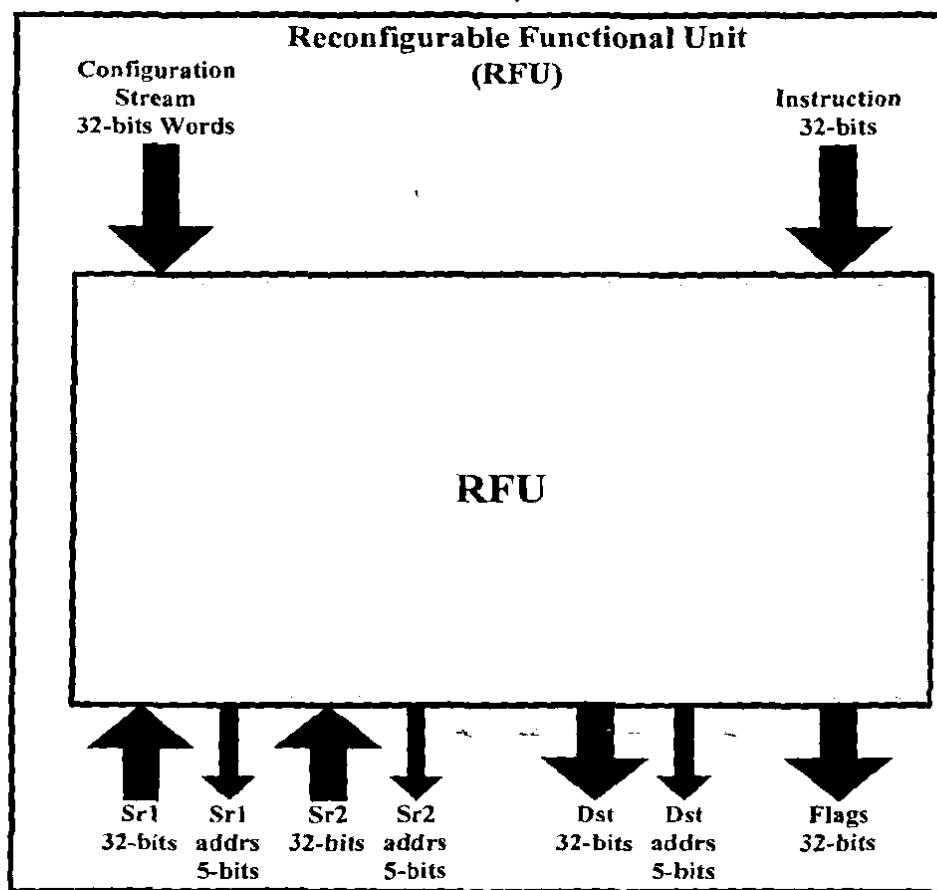

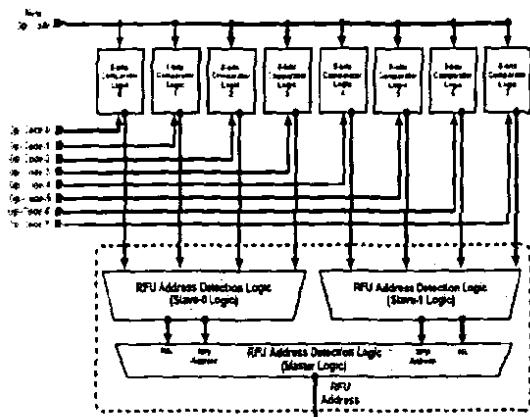

| Figure 4.13 Reconfigurable Functional Unit Interfaces .....             | 49 |

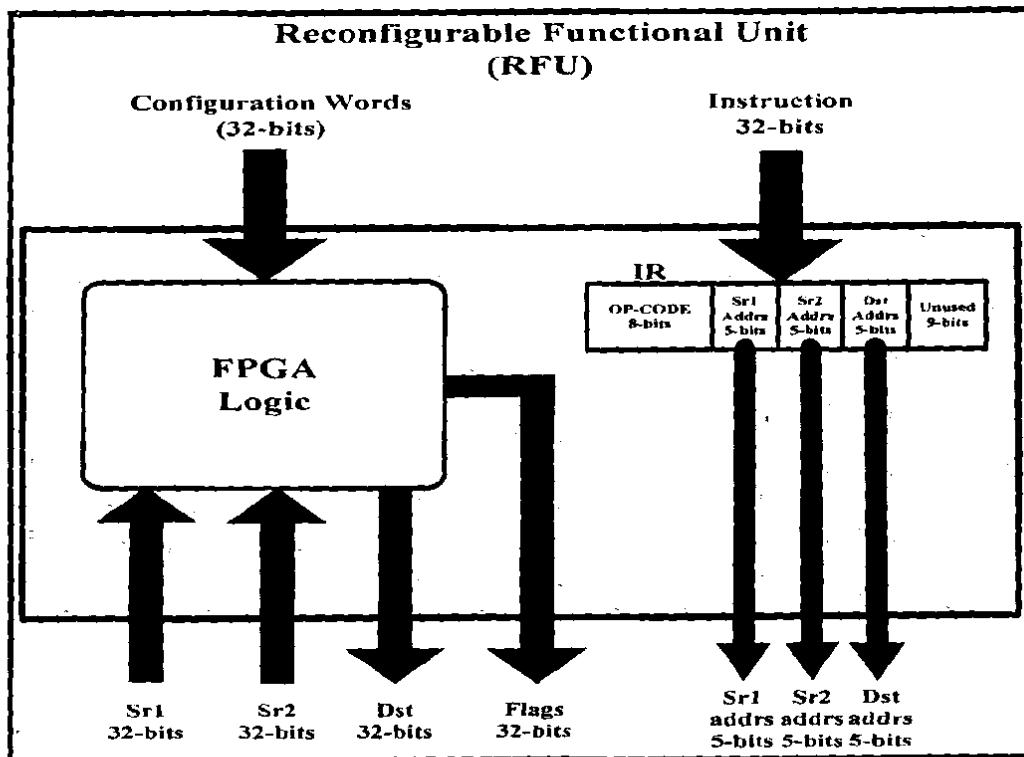

| Figure 4.14 Reconfigurable Functional Unit Interfaces .....             | 51 |

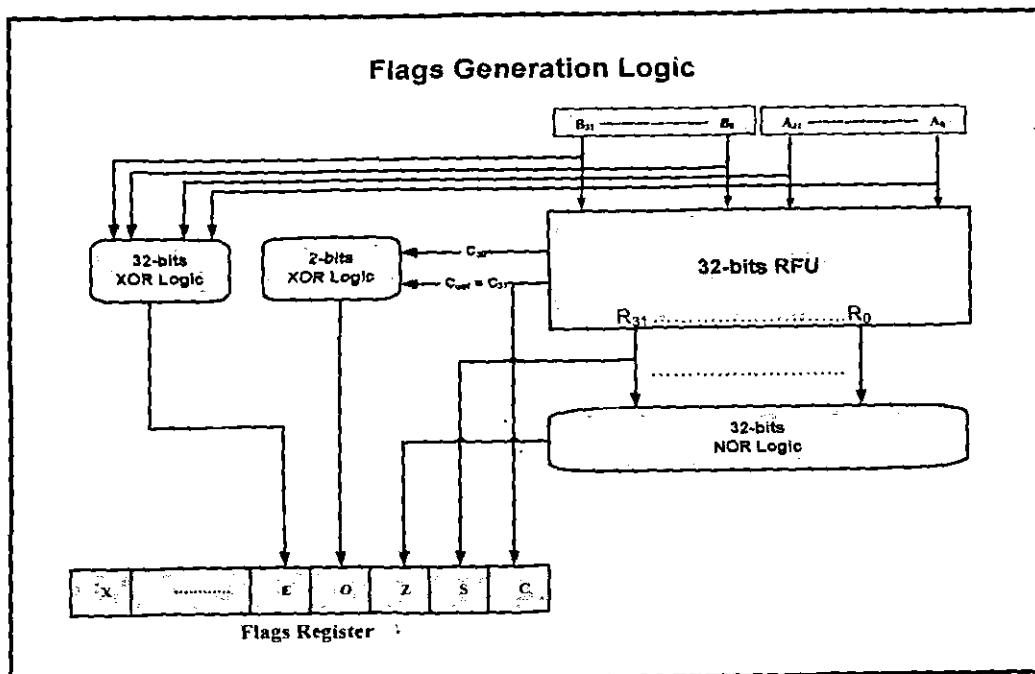

| Figure 4.15 Flags Generation Logic .....                                | 49 |

| Figure 4.16 Micro-programmed Control Unit .....                         | 54 |

| Figure 4.17 Micro-programmed Control Unit .....                         | 55 |

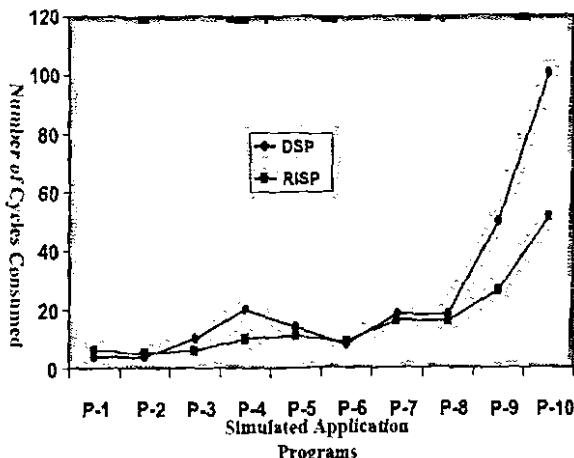

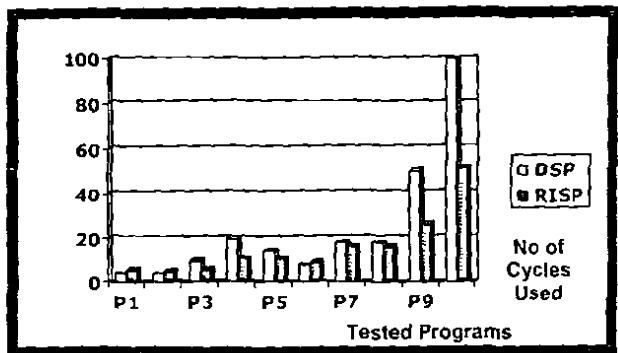

| Figure 5.1 DSP vs VLIW-RISP Performance Analysis.....                   | 71 |

## List of Tables

|                                                                                                                                       |    |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 3.1 Logic Component Clustering Sizes of LUT Based FPGAs.....                                                                    | 24 |

| Table 3.2 Cell Count and maximum Operating speed (one operation per cycle) for some arithmetic circuits in the Atmel 6000 device..... | 28 |

| Table 5.1 Statistics And Execution Formula of DSP Processor.....                                                                      | 54 |

| Table 5.2 Statistics And Execution Formula of VLIW-RISP.....                                                                          | 55 |

| Table 5.3 Calculated Statistics of Both Processors.....                                                                               | 67 |

# **Chapter No. 1**

## **Introduction**

## Chapter No.1

### INTRODUCTION

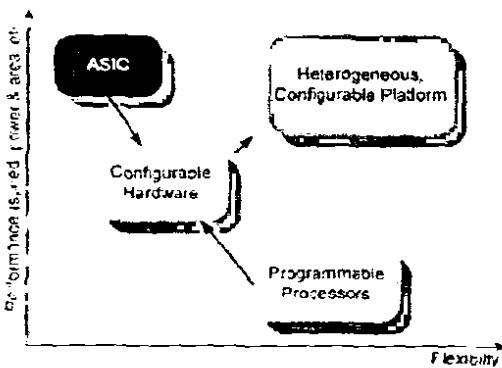

The revolution occurred in the field of embedded systems due to the microelectronics market is ever-increasing. In such a context the definition of efficient and cost-effective design approaches is mandatory. Hardware and software co-design solutions generally take into account architectures composed of one or more standard microprocessors and of suitable application specific integrated circuits executing the most time-critical segments of the application. Recently, the innovative concept of “mass customization” has been introduced. This concept considers the possibility of specialization of a micro-processor instruction set so as to optimize its performance for a given application or for a group of applications. Such an approach combines the time efficiency of application-specific functional units with the flexibility of *programmable logic circuits*. This innovation of programmable technology opens doors towards a new field of research known as *Flexible Instruction Set Micro-processors*.

In a broader sense the different levels of coupling or integration can be envisioned in architecture. A more traditional design approach is that of considering the reconfigurable part as a coprocessor, which is effectively working like a hardware accelerator that stalls the core-processor when under execution. Normally the co-processor approach requires coarse-grain functions to be executed in the part and therefore the speedup given by the co-processor program execution, when compared to processor application execution, must be considerably high [4]. A more realistic or innovative approach and an interesting challenge in academic terms is one that sees the part of the processor as a *Functional Unit* while operating in parallel with the other data-paths of the processor and where an extension of the instruction set is executed. The programmable processor so envisioned issues a set of native instructions to the native Functional Units, while these new customized instructions are issued to the Reconfigurable Functional Units (RFUs) [5]. A fine-grained function can be chosen for implementation in the part when compared to the co-processor approach since the integration is much higher and the RFU can be reached without any additional delay being embedded in the micro-processor.

*Reconfigurable Architectures* can be divided in two main categories: *fine grained* and *coarse grained* architectures [2]. The fine-grained architectures are based on programmable devices such as FPGAs (Field Programmable Gate Arrays) which include units (CLBs – Configurable Logic Blocks) that perform single functions on a bit basis. On the other hand, the coarse-grained architectures include word length units or small microprocessor distributed on an array of processing units. All architectures also include I/O, memory and Inter connect units. The advantages of coarse-grained architectures over fine-grained ones are mainly the reduction of configuration time and reconfiguration memory [1]. Fine-grained architectures also use significantly more area overhead to routing functions between CLBs and expend significantly more energy.

**Reconfigurable computing devices** can be configured after their fabrication to solve any computational algorithm or task. Such kind of reconfigurable devices are best exemplified now-a-days by FPGA [3]. In such devices the algorithms or tasks are implemented by spatially composing the built-in or primitive operations and operators with the possibility of temporally *varying or changing* the hardware of the operators. The re-configurable processor on FPGA can perform different operations on each bit of data or program and hence the re-configurable devices can be optimized to the data width of streaming data flows. The main theme of this kind of research work is to mix the advantages of *non* Von-Neumann architectures with the advantages of re-configurable processing devices or fabrics.

**Field-Programmable Gate Array (FPGA)** is a kind of silicon chip containing a set or an array of configurable logic blocks known as CLBs [3]. Unlike an Application Specific Integrated Circuit (ASIC) which can perform a single dedicated or specific function for the lifetime of the chip; a FPGA can be re-programmed many times to perform a variety of different functions in a matter of micro-seconds. Before it is programmed an FPGA knows nothing about how to communicate with the external connected devices surrounding it. Hence this is in fact both a blessing and a curse as it allows a great deal of flexibility in using the FPGA while greatly increasing the complexity of programming it. This type of generic ability to re-program FPGAs has led them to be widely used by hardware engineers and designers for prototyping digital electronic circuits. The performance advantage achieved from the FPGAs derives from the fact that the programmable hardware is likely to be customized to a particular algorithm. The field programmable gate arrays are configured to comprise only the operations that are appearing in the concerned algorithms [6]. The specialized instruction set micro-processor in fact contain ALUs of specific or specialized data bandwidths like 8-bits, 16-bits and 32-bits and always has pre-coded or determined control flow patterns.

The re-programmability and versatility of FPGAs definitely comes at a price. Only a few years ago, the algorithms or tasks that could be implemented in a single FPGA chip were very small. For example in 1995 the largest FPGAs could be programmed for circuits of about maximum of 10,000 to 15,000 logic gates at most. Since only a fast 32-bit adder requires a few hundreds logic gates, the capabilities of such devices were somewhat bounded. More recently the FPGAs have reached a size where it is possible to implement reasonable sub-pieces of an application in a single FPGA part [7]. This has led to an emerging new concept for computing. If a processor was to include one or more FPGA-like devices, it could in theory support a specialized application-specific circuit for each program.

The unlimited re-configurability of an FPGA permits a continuous sequence of custom circuits to be employed where each one is optimized for the task of the moment. Because FPGAs demonstrate a better performance scale than superscalar techniques, such designs have the potential to make better use of continuing advances in device electronics in the long term. The idea of reconfigurable computing has been a subject of research for a more than a decade, but most projects have investigated the potential of connecting one or more commercial FPGAs to an existing micro-processor via a standard

external bus such as the PCI bus [8]. If reconfigurable computing is really to become the computing paradigm of the future high speed platforms, then the main parts must be brought closer together. Only a few studies have considered the integrating of a micro-processor core and FPGA into a single device with the both tailored to co-operate very closely with each other and so there remains an important question about how such a device might be built and re-programmed and how it would fit within an existing general purpose-computing framework. Such a question must be addressed before the bigger issue of whether reconfigurable computing is really a good design model for computations can be answered.

**Reconfigurable computing** using reconfigurable devices like FPGAs have become an alternative to fill the gap between ASICs and general-purpose computing systems. Although the basic concept of reconfigurable computing was proposed in the 1960s, the reconfigurable computing systems have only recently become very vital and quite feasible. This is mainly due to the availability of high-density VLSI devices that use the programmable switches and routing networks to implement the extremely flexible hardware architectures. Most of the reconfigurable systems consist of a general-purpose processor core tightly or loosely coupled with reconfigurable logic [9]. These systems can implement specific functionality of applications or a set of applications on reconfigurable hardware rather than on the general-purpose processor and hence providing significantly better performance.

In a **statically programmed system** the individual data operations of an application will remain idle when they are no more required. For an example, the data dependencies within an application program may cause an operation to be idle and waiting for data inputs from other operations. Hence placing all operations onto the FPGA all at once is a poor choice hence resulting of wasting of a large no of precious hardware resources. Run-time re-configuration can be used to remove or recover such kind of idle operations by making them share limited hardware resources. Also the run-time reconfiguration provides a design method for large class of applications that are too big for the available hardware resources on the FPGA [10].

Many recently advanced systems, such as Garp [4], PipeRench [11] and Chimaera [10], are using run-time reconfiguration. In such kind of systems the hardware configuration can change frequently at run-time to reuse hardware resources for several different parts of a computation. Such systems have the potential to make more effective use of chip hardware resources than even standard well designed ASICs, where fixed hardware may be used only in a portion of the application algorithm or computation. Also the run-time reconfigurable systems have been shown to accelerate a variety of applications. An example of such kind of systems is the run-time reconfiguration within **automatic target recognition** (ATR) application developed at the UCLA to accelerate a template matching. The algorithm in this system was based on a correlation process between incoming image data from the radar and a set of target templates. Without taking considerations of the reconfiguration time, this system improves performance by a factor of 25 to 30 over a general-purpose computing system.

However, the drastic speed advantages of run-time reconfiguration do not come without a cost. By requiring a set of multiple reconfigurations to complete a computation, the time it takes to reconfigure the FPGA becomes a really significantly a key concern. The serial-shift configuration method transfers programming bits into the FPGA device in a serial way. This type of very slow method or programming approach is still used by a large class of existing FPGAs [7], [12]. Recent devices have moved the technology to cutting-edge domain and hence resulting in FPGAs with more than one million logic gates. The configuration size for such devices is more than one megabyte [13]. It could take from few hundred milliseconds to few seconds to transfer such a large configuration data stream using the serial-shift approach.

In most of such systems the devices must sit idle while they are being reconfigured and hence wasting cycles that could otherwise be performing useful work. For example, the ATR system uses 98% of its execution time on performing reconfiguration process, meaning that it uses merely 2% of total time in doing computation. DISC and DISC-II systems have been found to spend up to 90% [6] of their execution time on performing reconfiguration process. It is obvious that a significant improvement in system performance can be achieved by eliminating or reducing this configuration overhead associated with reconfiguration delays.

## 1.1 RC Architecture

*Reconfigurable Instruction Set Processor (RISP)* design offers many advantages over ASIC Processor design. It offers the flexibility of in circuit hardware reprogrammability. By using RISP design we can get the speed advantage of nearly an ASIC Processor design and flexibility of software. RISP design is not an easy task [11]. In RISP designing the most important issue is the reconfiguration methodology. Many different techniques have been introduced to provide an efficient reconfiguration process including partial reconfiguration, run time reconfiguration, static reconfiguration and the most recently introduced configuration cloning [1], [2]. Most of these methods of reconfiguration suffer from a problem of excessive reconfiguration (reconfiguration overheads).

Till now the reconfigurable computing is suffering from this problem and no one has provided satisfactory solution. Reconfiguration time should be minimized in order to obtain a level of satisfactory performance [3], [4], [11]. This can be easily achieved by using the already existing resources within the programmed device [15]. But the solution to this problem is in software tools not hardware [14].

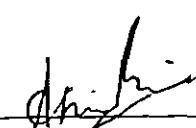

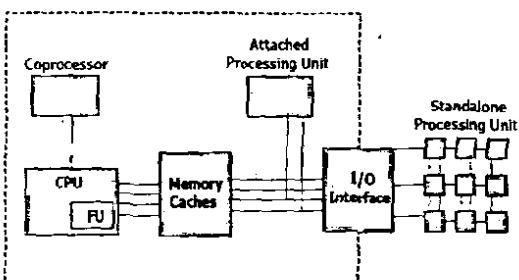

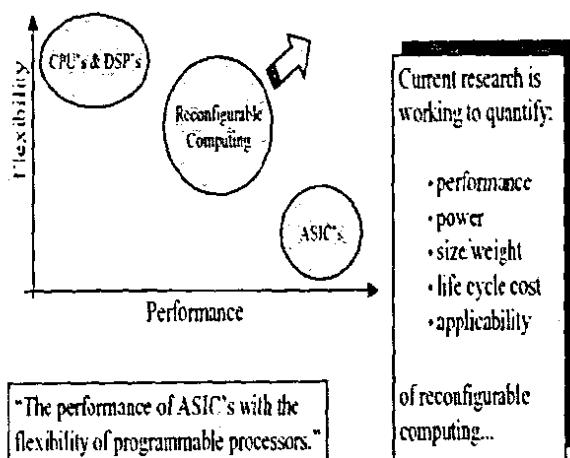

Figure 1.1 Reconfigurable Computing System

## VLIW Architectures

Very Long Instruction Word architecture refers to a CPU architecture that has been designed to take the advantage of instruction level parallelism (ILP) found in the program execution. A micro-processor that executes every instruction one after the other may use the micro-processor resources inefficiently at any time instant, potentially leading to drastically poor performance. The performance of such system can be improved by executing different sub-steps of sequential instructions simultaneously using the concept of pipelining or even executing the multiple instructions entirely simultaneously as is done in superscalar micro-processor architectures [15], [16].

Increase of computational performance is better achieved, for this case, if a micro-processor architecture supporting instruction level parallelism is chosen as the architectural platform or paradigm. Instruction level parallelism processing has become the new emerging architectural challenge since the eighties up to now, by enabling issue and execution of multiple instructions of an application within the same clock cycle. This paradigm would allow our envisioned reconfigurable architecture to fully exploit the native functional unit in parallel with the customized, reconfigurable cores.

Two main classes of ILP machines naming superscalar and VLIW have been flourishing. The former performs dynamic scheduling algorithms of instructions, and therefore granting binary compatibility with previous code versions, the latter relies on static or compile time scheduling, by delivering all instruction dependence analysis to the related compiler.

## 1.2 Motivation

Future interactive multimedia applications will be based on standards like MPEG-4. Using an object-based approach to describe and composite an audiovisual scene, MPEG-4 combines many different coding tools not only for natural audio and video but also for synthetic objects and graphics. Objects are coded and transmitted separately and composed at the decoder side, letting the receiver interact and influence the way the scene is presented on the receiving display and speakers. Due to this user interaction, the number and the type of decoders that needs to be implemented on the system is not known at the design time, but rather at the run-time [17].

This fact forces the designers of the platforms for these applications to use new approaches. Traditionally, multimedia applications have been implemented on custom VLIW processors that provide enough parallelism to accelerate these computation intensive applications [18], while at the same time retaining low power consumption. In order to increase even further the computational power of these devices, they have been enhanced with costume hard ware for acceleration of the most common multimedia operations. An example of this is the Trimedia Processor [18], which contains the specialized units for DCT (Discrete Cosine Transform) and motion estimation.

Unfortunately, due to the a variety of the algorithms that can be used in new interactive applications and the fact that the actual number and the type of the objects is not known till run time, it is no longer economically viable to make specialized functional units for each algorithm. The picture is further complicated if we also take into account that a platform designed for these applications may have to decode an object encoded with an algorithm for which it was not conceived. Therefore, in order to maintain the power efficiency and the real time constrains, we need a platform that can be specialized at run-time to the algorithm at hand. A platform based on reconfigurable instruction set processors (RISPs) provides this type of run-time specialization [5].

# **Chapter No. 2**

# **Literature Review**

## Chapter No.2

# Literature Review

### Introduction

Reconfigurable computing architectures have been evolved from the most prominently Field Programmable Gate Arrays (FPGAs). Recently, there is a variety of FPGAs now available commercially. A large class of computing systems has been developed by integrating multiple FPGAs chips and dedicated memory modules. A small no of systems have been coupled with a general purpose processor or some kind of application specific integrated circuit core such as a DSP processor to the field programmable gate arrays. In order to minimize the communication overhead and memory access bottlenecks being faced by the system for configuration bits the new arriving computing systems are integrating a reconfigurable logic onto the single same chip as that of the processor core chip [19].

### 2.1 Classification

There has been much different reconfigurable computing architecture that has been developed over the last few years by researchers. Reconfigurable computing architectures can be broadly classified based on several different parameters. In the following section, some of the most distinguishing architectural parameters which can be used to classify reconfigurable computing architectures have been discussed.

#### 2.1.1 Granularity

The granularity of the computational or reconfigurable logic is the size of the smallest functional unit that is addressed by the software mapping tools. In general the FPGAs have smaller granularity such as 2-input or 4-input functional units [20]. Several reconfigurable computing architectures such as Chameleon [19] implement coarse grain computational or arithmetic units of larger size such as 32-bits. Lower granularity in fact provides more flexibility in adapting the hardware to the computational algorithm. But, lower granularity has a great performance penalty due to the larger delays introduced when constructing computation modules of larger size using smaller functional units. A class of reconfigurable computing architectures implements features that are specifically targeted towards the reduction of these computational overheads.

#### 2.1.2 Host Coupling

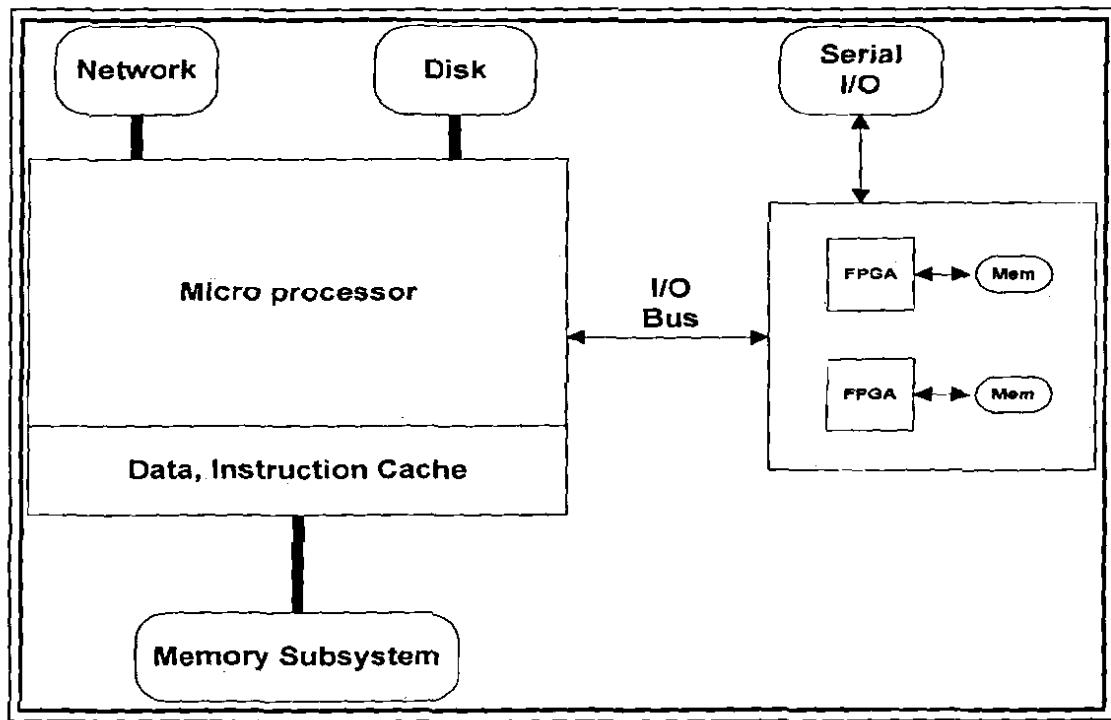

A large amount of logic is utilized as a processing fabric attached to a host micro-processor. The host micro-processor performs the control and supervision functions to configure the logic, schedule data input and output streams, external interfacing, among other the things. The type of logic coupling to such a host system dictates the

computational as well as configuration overheads in utilizing logic to speed-up computations. *The degree of coupling in fact affects the reconfiguration and the data access cost.* The degree of coupling can be roughly partitioned into three basic classes:

Figure 2.1 Host Coupling Approaches

**System-level Coupling (Loosely coupled):** This type of coupling includes the computing architectures which have logic communicating to the host through an I/O interface similar to other peripheral devices. A large class of initial FPGA based logic boards were architected with this degree of host coupling. Such architectures include SPLASH.

**Chip-level Coupling (Coprocessor or Attached Processing Unit):** These systems reduce the overheads in communicating to the relevant host by using direct communication between the host and the reconfigurable logic. An example of such a computing architecture is the PRISM [25]. A large class of the existing computing architectures with reconfigurable logic has been architected using this technique.

**Tight On-chip coupling (Tightly coupled):** The availability of large class of the transistors has resulted in the intensive integration of reconfigurable logic on the same chip as a host micro-processor, and hence significantly reducing the communication overheads between different components of the architecture. Such kind of architectures includes the well known Garp, Chameleon etc.

### 2.1.3 Reconfiguration Methodology

Conventionally, a reconfigurable device is configured by downloading a sequence of bits known as a bit-stream onto the device [21] during its operation. The speed and methodology being used during the download of bit stream depends on the interface supported by the device [22]. There are two main types of interfaces namely, Bit-serial and bit-parallel interfaces. The time required for the configuration of the device is directly proportional to the size of the bit-streams as well as on the type of the interfaces being used for this purpose [22]. Fine-grain and Coarse-grain devices have difference in the configuration overheads or time because coarse grain devices typically need smaller amount of configuration bit-streams. The flexibility of reconfiguration is achieved at the cost of reconfiguration cost. Reconfigurable logic has to stop computations for initiating a new configuration process. This reconfiguration time or overhead can be significant, especially for fine-grain multi-million gate FPGAs.

Some architectures support partial and dynamic reconfiguration processes. Partial reconfiguration allows the reconfiguration of the functionality of a piece or portion of the device while the remaining portion retains its functionality [23]. On the other hand the dynamic reconfiguration allows the reconfiguration of a piece or portion of the device while other portions of the device are performing computations [23].

A large class of other computing architectures addresses this problem by utilizing multiple contexts of reconfiguration or a reconfiguration cache [24]. Both are similar in basic principle. Some configurations of the device can be stored in on-chip memory. At run-time, it is less expensive to switch to one of the configurations being available in these memory chips or areas compared with loading a new configuration from external memory devices [24]. The organization of the cache varies among the computing architectures. Some computing architectures implement the architecture as an external memory device, whereas some other architectures have distributed context memories. For example, Chameleon RCP has a cache holding one configuration on-chip, which allows single cycle reconfiguration completion [27], [28].

### 2.1.4 Memory Organization

The computations being performed on the reconfigurable logic needs to access data from memory. Intermediate results from computations also need to be stored back before the reconfigurable logic can be reconfigured to perform the next computation [29]. *The organization of the memory system affects the data access cost and is a really significant fraction of the actual execution time or overhead.* Recently the most of the computing architectures include a large memory on the reconfigurable logic device [31], [33]. This memory can be implemented as large memory blocks just like those being available in Virtex FPGA as a Block RAMs or as distributed memory blocks just like those being available in Chameleon LSMs [34], [35].

## 2.2 Reconfigurable Computing Architectures; A Survey

In the latest computing domain the parallel processing techniques being based on Field Programmable Gate Arrays first time appeared in the domain of computing in the year of start of 1985-1990. In a broader sense the reconfigurable computational architectures can be classified into four main categories:

1. The Input / Output Bus Accelerators Systems

2. The Massively Parallelly Processing FPGAs Architectures

3. The Reconfigurable Computing Super-computers

4. The Reconfigurable Processing Logic Co-processors

## 2.4 Related Work

### 2.4.1 Coupling of Reconfigurable Architecture and a Multithreaded Processor Core with Integrated Real-Time Scheduling [47]

This research paper defines a real-time interface between the simultaneous multi-threaded CarCore micro-processor and a MOLEN-based reconfigurable computing unit. The CarCore is in fact IP core that enables simultaneous execution of one hard-real-time thread and further multiple non-real-time threads. The type of the hardware coupling described in this research paper extends CarCore by a reconfigurable computing hardware such that the both can execute different threads simultaneously, while the real-time behaviour of the hard-real-time thread is not disturbed. The main challenge under consideration is the design of a common memory interface for both, the CarCore and the reconfigurable computing hardware such that the memory operations fulfil hard-real-time constraints. Experimental results with an MJPEG benchmark have been obtained which show an overall application speedup of 2.75 which approaches the theoretically attainable maximum speedup of 2.78.

### 2.4.2 Introduction to Reconfigurable Computing Architectures [48]

In fact this mentioned research paper describes an overview of the research of the currently developed hardware and software based systems for reconfigurable computing architectures. This research paper also presents the alternating techniques that dedicatedly are targeting the concept of run-time reconfiguration process. They conclude this discussion by considering FPGAs in general and also by an exploration of the various hardware architectures used in reconfigurable computing systems. Further they worked at the layer of software based applications that were required for the assembling or de-compilation or compilation of the algorithms to reconfigurable computing systems and the trade-offs between manual map and rout and automatic techniques. Further more they have discussed FPGAs hardware in details and have also presented the detailed study about the hardware level coupling of the reconfigurable computing devices.

### 2.4.3 Reconfigurable Instruction Set Processors from a Hardware/Software Perspective [49]

In this research paper the authors have presented the design alternatives for reconfigurable instruction set processors (RISPs) from a hardware/software point of view. Reconfigurable instruction set processors are in fact programmable processors that contain a reconfigurable logic in one or more of their functional units. Hardware design of such processors can be split in two main tasks. First task is the design of the reconfigurable logic and the design of the interfacing mechanisms to the rest of the micro-processor. Among the most important design parameters include the granularity of the reconfigurable logic, the design or structure of the configuration memory, the instruction encoding formats and the type of instructions being supported. On the software side the code generation tools require new techniques to be coping up with the reconfigurability of the processor. Aside from the traditional computing techniques, the code generation requires the creation and evaluation of new reconfigurable instructions and the selection of instructions to minimize reconfiguration time.

### 2.4.4 Re-configurable VLIW processor for streaming data [50]

This research paper describes the instruction set level design of a reconfigurable VLIW processor for streaming data applications with alternating data bandwidths. It discusses the design of reconfigurable data stream processor, the design of VLIW processor for the reconfigurable approach, data control and address path design of the configurable VLIW and generating the FPGA code - VLIW re-configurable procedure.

#### *Reconfigurable RISC processor for variable data bandwidths:*

The reconfigurable processor core is in fact a two-address machine with RISC instruction set architecture and orthogonal general purpose register file.

- Address bus width is of size of 16 bits.

- Data busses width is of sizes of 8-bits, 16-bits, 32-bits and 64 bits for different functional units (ALU, GPR)

#### *Re-configurable systolic array - the data width sorter:*

The reconfigurable systolic array - *the data width sorter* is based on the hardware design research work. The research in Generic Algorithms is centered on the development of a novel design which uses systolic arrays. The generic concept is in fact extended by exploiting the pipeline architecture and principle to design a device that is independent of the lengths of the chromosomes being used in a particular problem [36]. The systolic arrays themselves are easily scalable to implement different population sizes. Prototype systolic array cells have been designed and targeted to the Xilinx XC4000 FPGA [37].

### *Re-configurable VLIW-CPU instruction set and format*

The first task designing the instruction set is to discuss the instruction to join the instruction set for the data stream approach in order to ensure ISA and EXO compatibility of the processor. Each VLIW instruction has 8 major fields:

- The *Systolic sorter* fields controls the systolic operation ALU and the global LOAD/STORE operations via crossbar. The information on the streaming data type sorted on every data output of the systolic sorter is coded as output in the *FPGA Condition Code Registers* of the systolic sorter

- The *R-CPUa*, *R-CPUb*, *R-CPUc* and *R-CPUd* fields control the four R-CPU's function. The R-CPU is a two-address machine.

- The *FPU\_memory* and *FPU\_control* fields control the 32 bit RISC *FixedProcesor Unit (FPU)* in performing LOAD/STORE and/or control oprerations.

- The *FPGA-code* contains the FPGA-SRAM images of the RPU and systolic units.

### *Data control and address path design of the configurable VLIW*

The VLIW core implements the host function for the systolic sorter and the four reconfigurable R-CPU calculators. The VLIW core executes all ALU, control and LOAD/STORE instructions in the program. There are no streaming data instructions. The main task of the VLIW core is to synchronize the Out-of-Order the operations of the R-CPU and the systolic sorter to execute the FPGA based code to reconfigure the R-CPUs and to invoice the LOAD/STORE operations for the systolic sorter. The *crossbar switch* between the *R-CPU data registers*, the *main memory* and the execution units is in fact a central part of the VLIW architecture. The *R-CPU data register set* is read-only through this device which virtually provides it with four ports. The crossbar switch extends the R-CPU data register set's read ports, making four "vertical" buses for all R-CPU and each bus is connected to one of the input ports of the dual-port memory with "horizontal" buses. It also performs some data width formatting (byte, word, etc). Accessing a R-CPU data register takes two cycles. One cycle for the register set and another for the crossbar.

Figure 2.2 Generating the FPGA code - VLIW re-configurable procedure

The main task of the systolic sorter is to generate a *condition code* for the different data widths as the result of sorting the streaming data. The compiler drives reconfigurations of the FPGA prior to execution of the application code, or possibly at the beginning of every section of code that requires reconfiguration.

#### 2.4.5 Reconfigurable Computing Systems Design: Issues at System-Level Architectures

In this research paper the authors discuss the issues involved in the design space of reconfigurable computing systems. They have identified nine key steps in RCS design as application analysis, system partitioning into hardware (HW) and software (SW), architectural design space analysis, mapping of the design library onto the architecture, partitioning of fixed HW and RLU of HW part, reconfiguration process, HW and SW synthesis, compilation and scheduling tasks and Integration of all the components. They briefly described the different models, architectures, compilation and scheduling of tasks, reconfiguration methods, optimal mapping of the design library on the RLU and the state-of-the art of RCSs. Finally they explain how they are going to solve some of the issues and methods in their system design. The nine steps of system design described in seven steps are as follows.

## **1. First step**

The first step is the modeling different architectural choices for a given application which will be optimized in terms of performance versus either given constraints or default design constraints after the application analysis.

## **2. Second step**

The second step is the proposing the optimized reconfigurable the architecture for a given application by exploring the different 'design space of the architecture' for reconfigurable architectures.

## **3. Third step**

The third step is the translating application onto DFG/CDFG or Hybrid architecture depending upon application requirement.

## **4. Forth step**

The fourth step is the partitioning the application using hardware (HW)-software (SW) partitioning methods and algorithms; here we may use best existing HW-SW partitioning methods and algorithms for our application with two level one level for basic partitioning that is HW-SW tasks and other level is reconfigurable logic block (RLB)-fixed kind of HW (F-HW) partitioning.

## **5. Fifth step**

The fifth step is the design and implementation of the optimized algorithms for mapping of the design library on to the proposed reconfigurable architecture.

## **6. Sixth step**

The sixth step is the design and implementation of optimized algorithms for scheduling the reconfigurable tasks (RTs), which will be implemented in RLB before mapping the design on to the reconfigurable architecture (RA).

## **7. Seventh step**

The seventh step is the implementation of prototype of the complete system; this involves integration of the entire modules using designed algorithms for scheduling of RTs and mapping of these RTs on to the proposed RA for given application.

### **2.4.6 Intelligent Reconfigurable Instruction Set Processor (I-RISP) Design [38]**

This Thesis presents the design alternatives for Reconfigurable Instruction Set Processor (RISP) from hardware point of view. Reconfigurable Instruction Set Processors

are programmable processors that contain reconfigurable logic in one or more of their processing units. In RISP the most important aspect is the re-configurability. Reconfiguration time will have to be minimized in order to obtain satisfactory performance. The solution to this problem is in software tools or to design such a hardware which minimizes the configuration overheads. In order to avoid excessive reconfiguration, the I-RISP (Intelligent Reconfigurable Instruction Set Processor) design has introduced an ICAU (Intelligent Configuration Analyzer Unit) using hardware approach. ICAU intelligently analyzes the expected configurations and reuses the existing resources (configuration). The ability to reuse the existing resources significantly increases the performance of I-RISP.

The proposed processor is based on VLIW architecture, having an Intelligent Reconfiguration Analyzer Unit. The purpose of Intelligent Reconfiguration Analyzer Unit is to minimize re-configuration overheads faced by RISPs. In existing systems the intelligence was created by using software techniques. This software based intelligent reconfiguration techniques are considerably slow speed due to the conventional instruction cycle concept. In order to eliminate this software based overhead the intelligence has been incorporated in hardware rather than in software.

The detailed architecture of the proposed design consists of the following modules:

1. Scheduler

2. Fetch Unit (FU)

3. VLIW (Very Long Instruction Word)

4. Intelligent Computational Unit

5. Intelligent Configuration Analyzer Unit (ICAU)

6. Configuration Unit (CU)

7. Reconfigurable Processing Units (RPUs)

# **Chapter No. 3**

## **Dedicated Machines and**

## **Reconfigurable Computing**

## Chapter No.3

# Dedicated Machines and Reconfigurable Computing

### 3.1 The Philosophy of a dedicated machine

One of the main issues in the evolution of computing architectures is their *specialization*. Many reasons can lead hardware designers towards pursuing a specialized computing architecture. The requirement of obtaining the high performances in a typical or particular application domain is one reason for it. Also, the timing issues in real-time embedded applications pushed the designers towards architecturing application-specific solutions which could more aggressively meet these requirements. Similarly other very important parameters include the cost and the power consumptions. These are the key design factors in the domain of embedded systems.

All these reasons and constraints introduce the requirements for a new design paradigm which takes these features into account and leads to the definition of new specialized cores or architectures. Hence one option is the general purpose computers, where the main issue is that of achieving more generally high performance in a very large spectrum of applications. The second option is the application-specific computers, where embedded applications or algorithms guide architectural design in more compact form. Dedicated or application specific architecture, performances are generally not measured on conventional benchmarks but they are measured only on the application the machine is designed for.

A large no of the different approaches have been taken by architectural researchers to guide the design of application-specific solutions or algorithms. One of the early approaches proposed for the design of this kind of machines was the ASIP (Applications Specific Instruction set Processor) philosophy. It was an emerging design paradigm in the field of application specific computing. ASIPs are programmable processors where the Instruction Set is adopted to a particular application.

#### 3.1.1 The main theme behind Instruction Set Specialization

The elements of the Instruction Set of a micro-processor, i.e. the op-codes are the *bricks* into which a high level code is broken down for execution on a micro-processor. The operation specified by each op-code is commonly executed on a most dedicated and highly optimized functional unit and therefore we can see the functions specified by each of the op-codes as the *hardware execution bricks* of the software execution flow.

If these bricks increase in granularity or size by performing more complex operations than those which are typically available in the instruction set of RISC micro-processors, then the instructions in the code will more generally correspond to more complex functional units, possibly characterized by more latency and performing 'larger' computations when compared to RISC functional units. Since we know that the hardware

execution speed is much faster than the software execution speed hence an application broken down into bigger bricks will in generally be faster to execute than one broken down into smaller ones. However, no doubt that the simple operations are common to many software applications, the more complex operations become the less likely it is that they are common to a large number of applications. Therefore, while a more complex functional unit will speed up execution of the algorithm when extensively used by a typical application, it is also true that the area dedicated to such a type of the unit would result wasted, when running those applications programs that do not exhibit such complex operations in their program code. Moreover, the presence of complex instructions mostly complicates some program code generation tasks such as code selection and register allocation among others.

The ISA specialization has been studied deeply in the past few decades [39]. In a library of re-current sub-graph patterns is generated. Pattern matching and graphs covering is then performed. The problem of optimizing area of functional units through their specialization is also deeply considered and it is observed that much of the ALU functionality is not used when only one or a few embedded system applications are considered for execution. The embedded system application code is analyzed so as to discover that which functionalities of the ALU are actually required. Functional Units having lower cost and area can then be designed and specialized to the application analyzed.

### 3.2 FPGAs

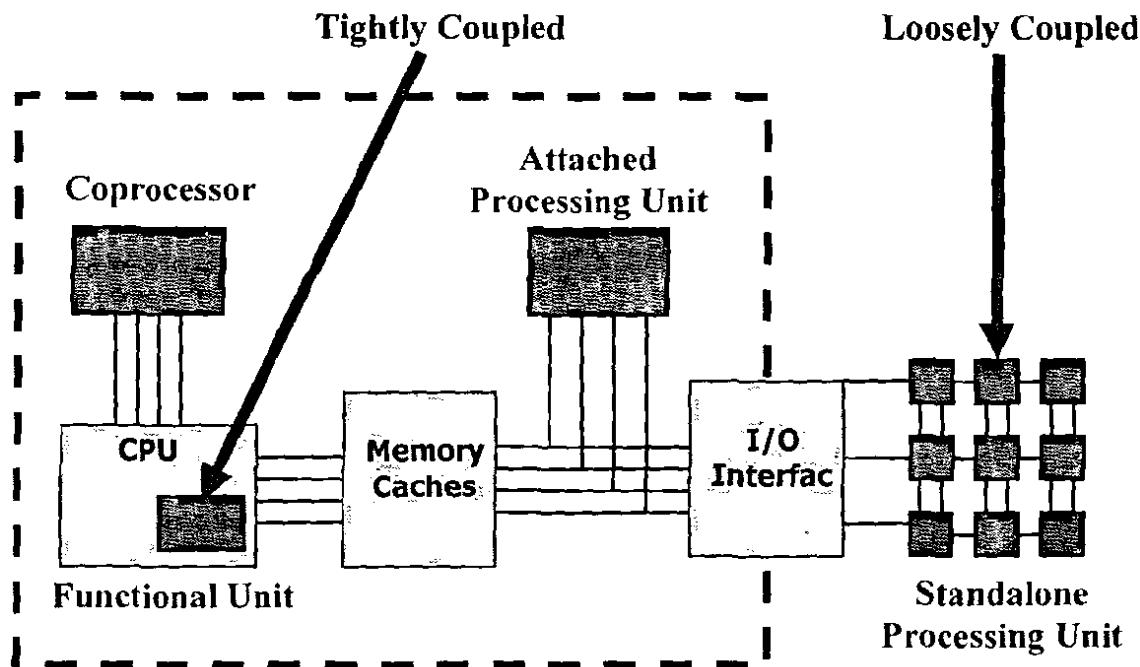

A Field Programmable Gate Array is consisting of an array of combinational logic clouds or blocks overlaid with an interconnection network of horizontal and vertical wires. Both the combinational logic blocks and the interconnection network are configurable or programmable [40]. Their configurability is achieved by using either anti-fuse elements based technology or SRAM based memory bits to control the configurations or programming of the transistors. The Anti-fuse based technology uses a strong electric or electronic charges or currents in order to create a programming connection between the two adjacent required terminals. Hence in this way in fact this is a typically less reprogrammable system. Static RAM based program configuration can be re-programmed unlimited number of times on the fly by simply downloading a set of different configuration bit streams into the Static RAM based memory cells.

Typically a configurable logic block shortly known as CLB architecture in fact is consisting of a look-up table shortly known as LUT, a Delay flip-flop shortly known as D-FF, some other form of additional combinational logic circuitry and also consisting of a set of Static RAM based memory cells to control the process of configuration of the laid down configurable logic blocks (See Figure 3.1) [41]. The laid down digital logic circuitry or blocks of the FPGA device also perform the Input/Output operations in order to load and store the data streams being required for the processing. On the other hand the horizontal and vertical interconnecting networks can also be reconfigured by programming or changing the connections between the laid down configurable logic blocks and the set of wires and by configuring the integrated programmable switch boxes

shortly known as PSB, which connect different horizontal and vertical wires. These programmable switch boxes (PSB) for the interconnecting networks are also controlled or programmed by the Static RAM based memory cells. In this way the logical functions being computed inside the available configurable logic block (CLBs), the horizontal and vertical interconnecting networks and the Input/Output blocks can be configured and reconfigured by using the external data streams. Field Programmable Gate Arrays typically allow the unlimited number of reconfigurations for the laid down device. These versatile kind of programmable devices so far have been used to build even large scale micro-processor cores and co-processor cores whose internal architectures and as well as interconnections can be reconfigured in order to match the requirements of a hand on running application. In order to a very brief reconfigurable computing architectural survey of Field Programmable Gate Arrays and some other important improvements of the concerned technology consider the references of [3], [7], [13].

Current and future generations of reconfigurable computing systems or devices have ameliorated the reconfiguration and configuration costs by providing a typically high speed and most optimized partial and dynamic reconfigurability process [42]. In the process of partial reconfiguration of the under laid device [23], it is quite possible to update or change the configuration bit streams of any one part of the working under laid device while the at the same time the configurations of the remaining part is still retained in its original form. On the other hand in the process of dynamic reconfiguration of the under laid device, the under laid devices allow this partial reconfiguration process even during the interval when even other configurable logic blocks are performing their regular operations or computations [43].

Figure 2 Typical FPGA Board, Device and Logic block architecture

Typically, the requirements of the applications are increasing at a rate which is much faster than the increasing rate in the size or density of the computational logic resources mostly available on the most of Field Programmable Gate Arrays. Field Programmable Gate Arrays architectures have limitations on their Input/Output capability of processing due to the limitation on the available total number of Input/Output (IO) pins which are physically available on the under laid device. In order to map and rout such kind of large scale user applications onto the available configurable logic blocks, the different computing systems have been designed which have several Field Programmable Gate Arrays some times on a single board or even some time on a single chip.

These board level reconfigurable computing architectures are mostly designed to function under the supervision an external configuration controller or kind of configuration supervisor or some times even they may use one of the on-board Field Programmable Gate Arrays as a main controller. There are a large number of such systems available. The examples of such systems may include the DECPeRLe board, and SPLASH-2 [30], the TERAMAC and the WILD series of devices being provided from Annapolis Micro-systems. Also some other sort of software tools exist which have the ability to automatically partition the whole design between the physically available

multiple Field Programmable Gate Arrays on a single board by using the kind of higher-level of programming abstractions [27].

### 3.2.1 The Basic FPGA Architecture

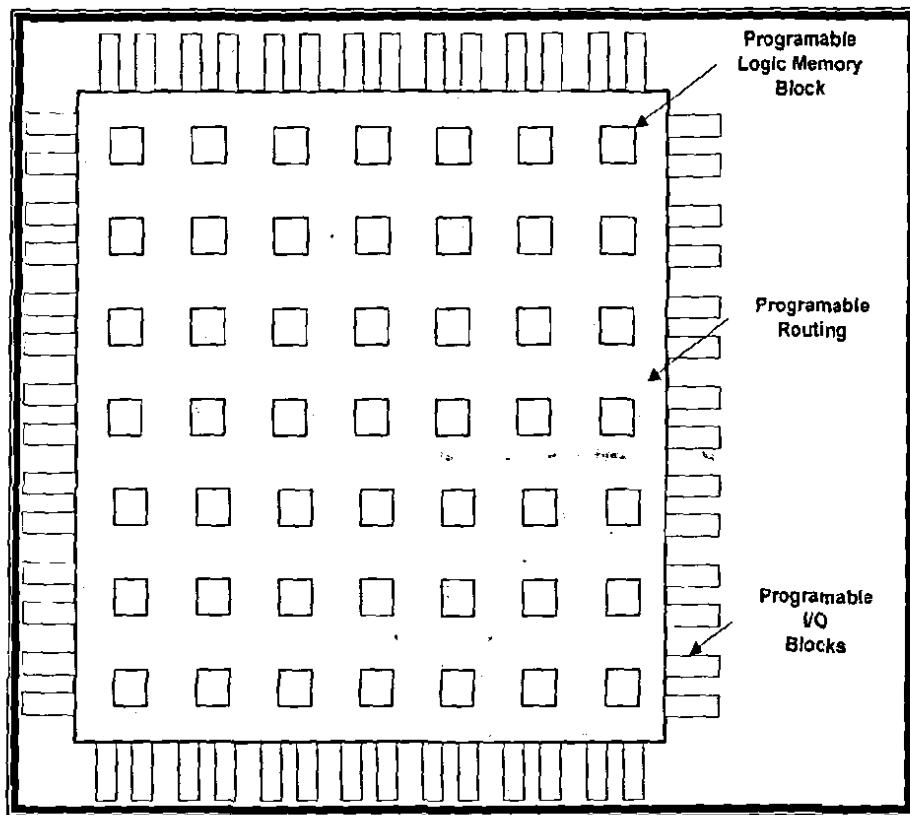

The basic architecture of Field Programmable Gate Arrays consists of broadly three kinds of components. These mentioned components include configurable logic blocks, programmable routing resources and a set of input/output logic blocks or IO blocks [44].

Generally, Field Programmable Gate Arrays consist of an array of programmable logic blocks known as CLBs that can be interconnected to other CLBs and also as well as to the programmable Input/Output blocks of the system through some kind of reprogrammable routing resources or architecture. Figure 3.2 provides a very simplified block diagram of the internal architecture of a generic Field Programmable Gate Array.

Figure 3 A Generic FPGA Architecture

#### i. The Programmable Logic

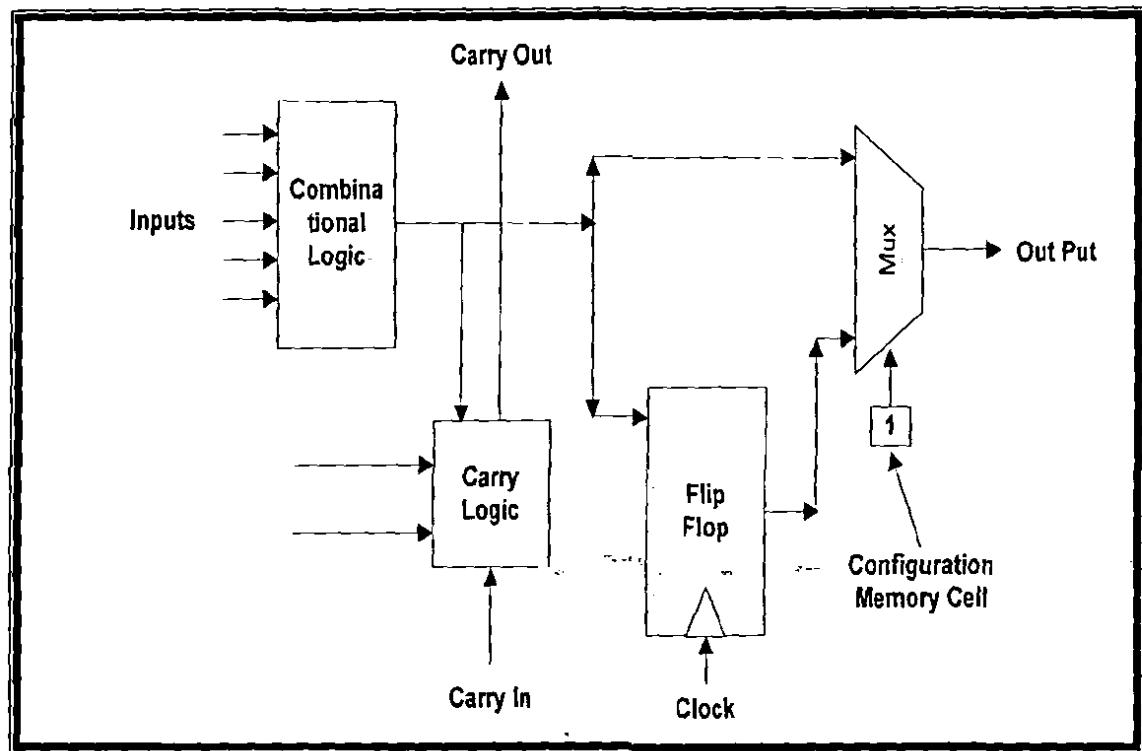

Field Programmable Gate Arrays designers have designed a large number of a variety of programmable logic architectures for Field Programmable Gate Arrays after their great invention in the mid-1980-1990. Since from few decades the much of the programmable logic structures being used in Field Programmable Gate Arrays can be optimally generalized as shown in Figure 3.3. The fundamental programmable logic element being

integrated inside the FPGA generally consists of some kind of programmable combinational logic or CLB, a delay type flip-flop D-FF or kind of latching mechanism, and a kind of fast carry control logic to reduce the area density and typical delay costs for implementing such kind of carry logic.

Unlike other generic configurable logic component or element, the currently available commercial Field Programmable Gate Arrays devices provide a large number of programming flexibility within the available logic element. For example, a delay flip-flop D-FF in many commercially available Field Programmable Gate Arrays can be made to operate as a simple latch circuit and can be programmed to have many combinations of asynchronous as well as synchronous sets / resets and can be negatively- edge triggered or positively-edge triggered.

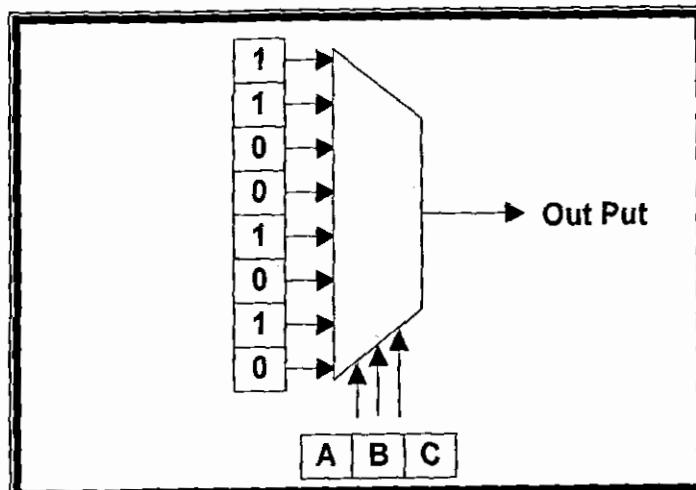

Figure 4 A Generic Programmable Logic Block

Although the most of the reprogrammable Field Programmable Gate Arrays use Look-Up Tables for their combinational logic, several other architectures like [12], [13], [14]) have been found to be used combinations of multiplexers and digital logic design gates to implement this programmable logic architecture or structures [45].

Figure 5 Three-Input Look-Up Table

| Device Name       | Year | LUT Width | Cluster Name | Cluster Size |

|-------------------|------|-----------|--------------|--------------|

| Xilinx XC2000     | 1985 | 4         | CLB          | 1            |

| Xilinx XC3000     | 1987 | 4         | CLB          | 2            |

| Xilinx XC4000     | 1990 | 3 & 4     | CLB          | 1 & 2        |

| Altera Flex 8000  | 1992 | 4         | LAB          | 8            |

| Altera Flex 10K   | 1995 | 4         | LAB          | 8            |

| Xilinx Vertex     | 1998 | 4         | CLB          | 4            |

| Altera Apex 20K   | 1998 | 4         | LAB          | 10           |

| Xilinx Vertex II  | 2000 | 4         | CLB          | 8            |

| Altera Apex II    | 2001 | 4         | LAB          | 10           |

| Altera Stratix    | 2002 | 4         | LAB          | 10           |

| Xilinx Vertex 4   | 2004 | 4         | CLB          | 8            |

| Altera Stratix II | 2004 | 3 & 4     | LAB          | 24 & 16      |

Table 1 Logic Component Clustering Sizes of LUT Based FPGAs

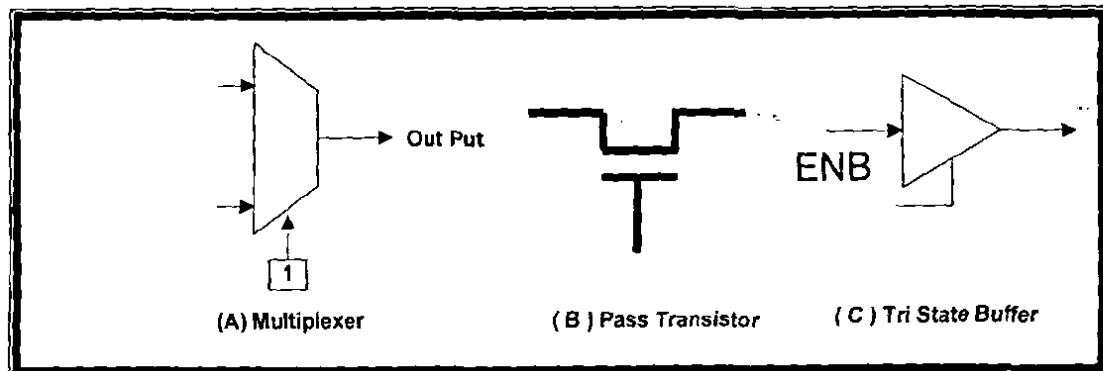

## ii. Programmable Routing Resources

The Field Programmable Gate Arrays designers have used a large class of different routing resources or structures within their Field Programmable Gate Arrays. Different kinds of forms or designs of routing resources exist through out the designs of each Field Programmable Gate Array. Commonly some amount of routing resources is also included within the design of the each logic clustering element so that the laid down logic elements can be combined to form bigger and more complex functions.

In order to implement the nature of the programmable routing of the resources, there are three basic switch types that have been used. These types include the digital multiplexers, the pass transistor circuits and a commonly used tri-state buffer gates. Figure 3.5 describes each of these mentioned switches with a Static RAM memory cells controlling their outputs. Commonly, the passing transistor circuits and the digital multiplexers have been used within the area of a logic cluster in order to connect the logic

elements or components together while all of the above three have been used for the more global routing structure.

Figure 6 Basic Programmable Switch Types

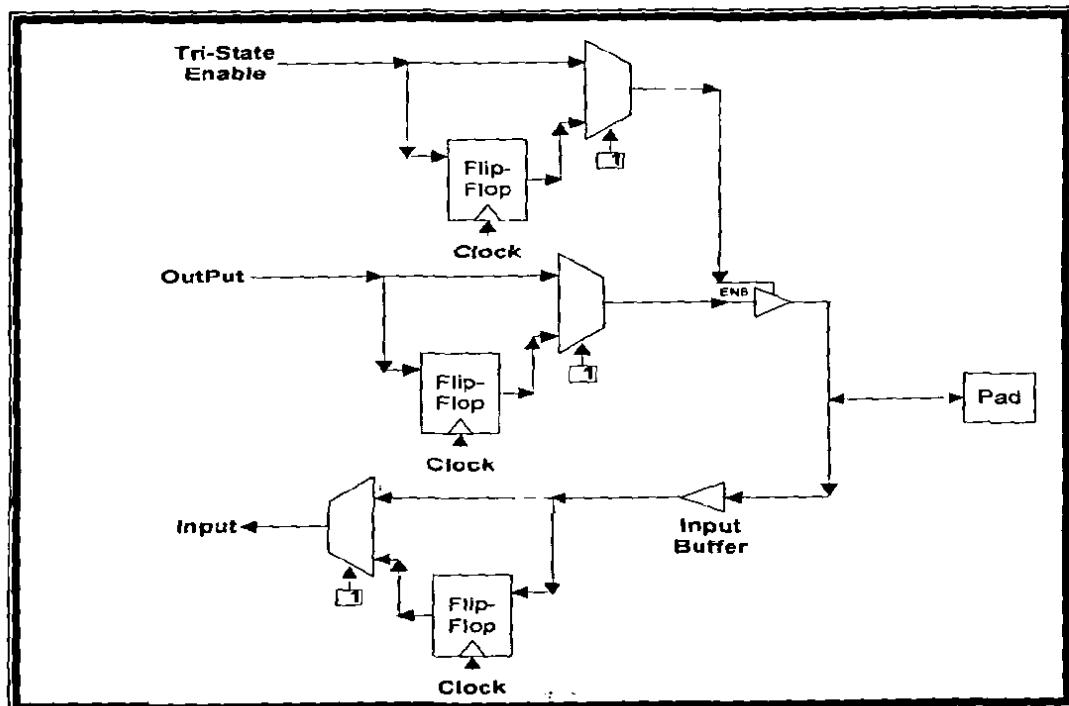

### iii. Programmable Input/Output Architectures

Unlike programmable logic resources and routing resources, the basic input/output resources or IO architecture, as is shown in Figure 3.6, is very similar among the different Field Programmable Gate Array families being evolved so far. The Input/Output logic blocks have been found with the tri-state buffer gates for the outputs and input buffer gates for the inputs of the system. The tri-state logic enable / disable signal, the output logic control signal and the input logic control signals can be individually latched or registered by using flip-flops within the Input/Output blocks or can be programmed as the un-registered being depending on the fact that how the I/O block is being programmed.

Figure 7 I/O Block Architecture

### 3.2.2 FPGA technology

Field Programmable Gate Arrays can be traditionally divided into two main categories:

#### 1. *Anti-fuse Based FPGAs*

#### 2. *SRAM Based FPGAs*

Recently another FPGA technology has been introduced by Alcatel, which is based on Flash/CMOS based circuits [72].

The first type or category of FPGAs uses anti-fuses as a mean to program the device. Anti-fuses implemented in a CMOS technology are being initially open circuits and after that once they are programmed they take on a low resistance. The main characteristic of this kind of FPGA is the fact that it can be programmed *only once*.

The second category of FPGAs uses SRAM cells as a mean for programming the device. A 1-bit SRAM can control FPGA switches in two different ways including either by controlling the gate node of a pass transistor or by controlling the select line of a multiplexer drives the inputs of logic blocks.

The main advantage of SRAM-based FPGAs lays in their nature of *re-programmability*. The logic value of the SRAM cells can be overwritten or updated for a number of times and hence allowing the FPGA to be reconfigured even *on-the-fly*. Another characteristic of such kind of FPGAs is the fact of being volatile, i.e. the configuration must be loaded onto the device every time the system is booted up or powered-up. The interest of this thesis for SRAM-based FPGA is indeed due to re-programmability nature of it on-the-fly: as it will be seen, this allows change of the IS of the proposed architecture while the application is running.

Further FPGA technology features of interest for this thesis include the latest techniques of partial reconfiguration or re-programmability and context switching. The former is the capability of re-programming only a specific part of the whole device, while the rest part of the device is remains operational. The latter feature called context-switching of the configuration is a new technology which enables an FPGA to hold contexts of the multiple configurations at the same time. Configurations are stored in a series of memory blocks or memory banks so that it is possible to rapidly switch between them within the delay of nanoseconds [36].

### FPGA Mapping Tools

Implementation of a circuit onto an FPGA platform requires sophisticated CAD tools. Hardware description language or a schematic description is used to enter the design. In the process of transforming such descriptions into the FPGA configuration, there are three main phases.

*1. Mapping phase**2. Placement phase**3. Routing phase*

In the mapping phase the circuit is logically partitioned into modules or parts so that each one is assigned to one configurable logic block of the FPGA. The second phase, called placement, is the process of assigning the computation of every configurable logic cell generated in the mapping phase to a *physical* logic cell being available on the device. The third phase, called routing, targets at defining all the connections among cells through programming the available horizontal and vertical switches. The complexity of the CAD tools is very high and the three phases can take much more time from few seconds to few hours for large circuits.

### 3.2.4 Commercial FPGAs

#### Xilinx:

Xilinx FPGA devices consist of a two dimensional array of configurable logic cells connected by horizontal and vertical layers of wires. The most widely used FPGA include the generations of Xilinx devices XC4000 [45] which claimed the density or capacity from 2K to 15K equivalent gates.

In the XC4000 FPGA device Configurable Logic Block (CLB) is based on lookup tables. A lookup table is in fact an array of 1-bit memory cells, where inputs are the address of memory lines, and the one bit output is the data line; thus, a lookup table with  $\kappa$  inputs will have  $2^k$ -1 bit possible memory cells. A lookup table can implement any  $k$ -inputs logic function or computation. A CLB mostly has more than one lookup tables, and one or more than one flip-flops. The XC4000 CLB consists of 3 lookup tables, two of them with 4-inputs and one with 3-inputs and two flip-flops. One of the circuits that a CLB can implement is a full adder, so that CLB can be configured or programmed to implement any fast arithmetic circuit as carry-save or carry-look-ahead adders. CLBs can also be used as read/write SRAM cells. A CLB is programmed by setting the memory cells to the values given by the truth table of the digital logic circuit to be implemented.

The second distinguishing feature of FPGAs is their routing connections or interconnects. The XC4000 features horizontal and vertical channels. Each of these channels consists in short, long, and medium distances wires. Short distance wires are used for interconnecting two close CLBs, while the long distance wires can connect far CLBs. In fact long distance wires tend to have much less switches than shorter wires. The final delay of the circuit depends heavily on how the CAD tool has assigned wire segments to physical wires after the process of routing.

### Altera FLEX:

The Altera Flex 8000 series of FPGAs has a logic density or capacity of 4K to more than 15K equivalent logic gates. The device consists of a 3-level hierarchy. The lowest level is a set of lookup tables. The basic logic block, called configurable logic element, consists of a 4-input lookup table, a flip-flop and some additional circuitry for fast carry propagation purposes. At a highest level, is the Logic Array Block? This consists of eight logic elements, connected together through a local interconnect. Any two logic elements of the block can be connected to each other by programmable wires. The local interconnect and every logic element are connected to the Fast Track global interconnects, similar to the XC4000 long distance wires.

The Flex 10000 family of FPGA features a different characteristic to that of 8000 series of family. Every row of the device contains an embedded array block which can be configured either as an SRAM memory cell block or as a lookup table. The latter use serves to implement any complex digital logic circuit through a multi-output lookup table. To more exploit this feature Flex tools contain various macro-functions to be implemented in embedded logic blocks.

### Atmel:

The AT40K and AT6000 FPGAs family or series present the particular feature of *partial configurability*. This means that specific parts of the an FPGA device can be reconfigured while the rest continues to operate without disruption. This is particularly useful in reconfigurable systems where instructions are taken in and out of the programmable functional unit. The AT6000 logic cell contains a D-type register and about twelve logic gates. Interconnect is peculiar in that it provides diagonal connection as well, in addition to the usual vertical and horizontal programmable interconnections. Every cell is therefore *octagonal and hence* it can be connected with eight neighbors. The Atmel devices provide an internal SRAM memory that can be used for caching configurations. A more advanced context-switching FPGA device is currently under development at NEC. It is claimed that the area required to store multiple contexts does not grow linearly with the number of context [12]. In the future, the usage of even DRAM cells instead of SRAM cells to save FPGA contexts could increase even more FPGA potentialities.

### **3.2.5 FPGA performances**

The FPGA performance in terms of execution speed is affected by two main features. The time needed to download a configuration describing a certain circuit and the time needed to execute the function implemented by loaded circuit. Another important issue is the time the software tool takes to generate configurations.

This is not as easier to give these performance figures in a straight forward way. The time overhead for reconfiguration varies considerably depending on the size of the device. Obviously a device implementing small logic functions will take less time to

reconfigure because a smaller number of reconfiguration bits streams are involved. A good measure of reconfiguration time overhead could therefore be given *per configurable logic block used* or even *per gate equivalent* which is even better because it is not affected by the block granularity of the FPGA device. Another important issue is the frequency at which the device operates, which is directly proportional to reconfiguration time overhead. In the Atmel 6000 the reconfiguration for the full device takes from 1 to 8 mili seconds and this corresponds to almost 0.2 micro seconds for per Cell. Altera 10K claims 115 MHz performances with a density of up to 250 K logic gates. Xilinx has recently launched a new line of FPGAs called VIRTEX series which targets operation frequency of more than 300 MHz.

Table 3.1 gives performance of the Atmel6000 in terms of execution delay of some arithmetic circuits.

| Circuit                       | Cell Count | Max Speed |

|-------------------------------|------------|-----------|

| 16bit Ripple Carry Adder      | 64         | 8.9MHZ    |

| 16bit Fast Ripple Carry Adder | 96         | 11.4MHZ   |

| 16bit Carry Select Adder      | 222        | 15.7MHZ   |

Table 2 Cell Count and maximum Operating speed (one operation per cycle) for some arithmetic circuits in the Atmel 6000 device

### 3.3 Reconfigurable CPUs

Since FPGAs present both advantages of re-programmability as well as the high performance of custom circuit; it is appealing to combine a micro-processor core with reconfigurable resources in order to achieve a speed or performance improvement over either a separate micro-processor or a separate reconfigurable FPGA device [3]. While it is possible to combine conventional micro-processors with available reconfigurable FPGA devices at the circuit board level; the integration changes the I/O costs for both devices. An architectural solution which is definitely appealing is therefore the integration of an FPGA on-chip. A number of different solutions are as under:

- i. *Totally reconfigurable processor.*

- ii. *The co-processor approach.*

- iii. *A partially reconfigurable CPU.*

#### 3.3.1 Totally Reconfigurable Processors

This is a kind of the design approach where a CPU together with a reconfigurable accelerator is designed or implemented by means of a reconfigurable logic. An important project of this kind is the Dynamic Instruction Set Computer (DISC), designed at Brigham Young University [6]. DISC consisted of two CLAy31 FPGAs developed by National Semiconductors and memory on a circuit board connected to a personal micro computer. DISC made extensive use of the latest technique of partial reconfiguration. The first FPGA was consisting of a permanent control unit while the second was divided into

rows to simplify array management and allow for custom-instruction spatial caching. Custom instructions were intended to be swapped into and out of the FPGA similar to that of the pages of virtual memory. Before initiating execution of a custom instruction the device operating program asks the FPGA for the presence of the custom-instruction configuration. If the custom instruction is currently really on the FPGA, then the execution is initiated otherwise program execution pauses while the custom instruction is configured on the FPGA.

### 3.3.2 The Co processor Approach

Such an approach in fact proposes a *loose* coupling between micro-processor core and the reconfigurable logic. The latter acts as a coprocessor where it is a slave computational unit located either on the same die as the processor or off the chip. The granularity of the implemented function in the reconfigurable section is much higher than that of the mixed CPU approach. This is due to the fact that the communication with a coprocessor is much slower than that of the communication with a parallel data-path of the CPU. Therefore the block of computation delivered to it must be large in order to give high performance gain or improvement. A research project that fits in this category of reconfigurable computing is the Garp by the BRASS group at Berkeley [4]. The proposed architecture in fact consists of a MIPS processor placed in the same die with a reconfigurable coprocessor. The coprocessor is activated by the processor when a reconfigurable function is called. At this point the processor turns off and the coprocessor carries out the computation of the reconfigurable instruction set having also access to both the processor core and cache memory. The coprocessor also includes a memory for caching configurations so that to allow a fast context switching.

### 3.3.3 A Partially Reconfigurable CPU

This kind of approach proposes a very close or tight coupling between the main processor core and the CPU. Contrarily to the coprocessor approach here the CPU and the reconfigurable logic both compute simultaneously. The reconfigurable module is indeed added to the data-paths of the core CPU and hence introducing a special kind of functional units called Reprogrammable Functional Units (RFUs). This kind of system organization allows definition of an extension of the architecture Instruction Set by the implementation of new instructions on the RFUs. Also since the FPGA can be run-time reprogrammed; one element of the instruction set can be mapped onto an RFU for the whole length of the application as well as such element can vary during the application execution time through reconfiguration of the FPGA section. A number of projects have used the mixed CPU architectures in the past. The PRISC project [35] developed at Harvard presented to extend the Instruction Set of a RISC processor through implementation of particular functions onto one or more Programmable Functional Units. A framework is proposed where the choice of the functions to be implemented in the PFUs is very transparent to the programmer. The most general computational model for a PFU is said to be a multi-cycle sequential state machine. Performance gains were measured on the SPECint92 benchmark suite and a speedup factor of 10% to 90% was reported. A second proposal of tightly coupled micro-processor core and a

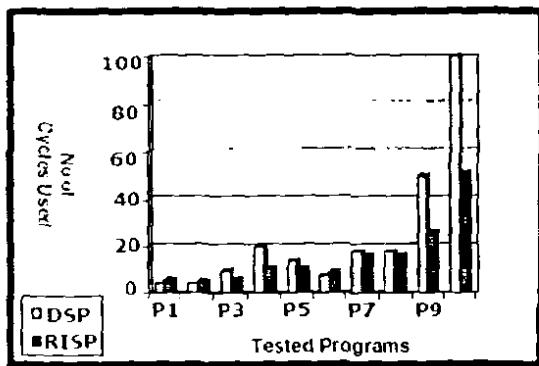

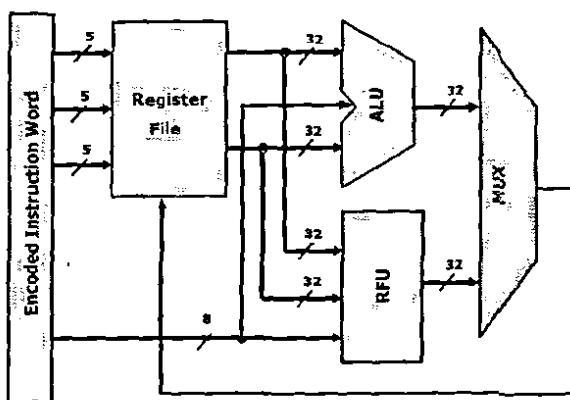

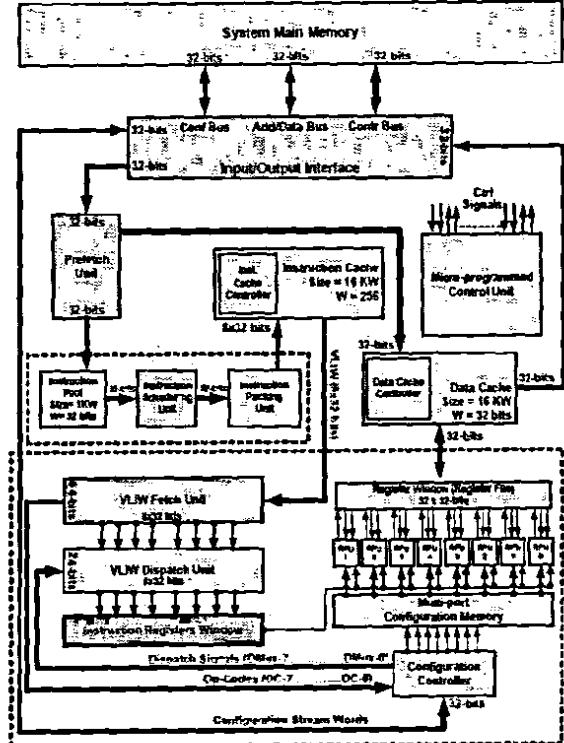

Reconfigurable Logic is that of the OneChip project. OneChip proposes an architecture which is very close to that of PRISC. The major difference from the PRISC approach is that in this system any kind of function is allowed to be implemented in the PFU.